Package carrier and manufacturing method thereof

A technology for packaging a carrier board and a manufacturing method, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, and electrical solid-state devices, etc., can solve the problems of low packaging yield, poor electrical reliability, and small size, and achieves reliable structure. The effect of thinness, improved packaging yield, and good electrical conductivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

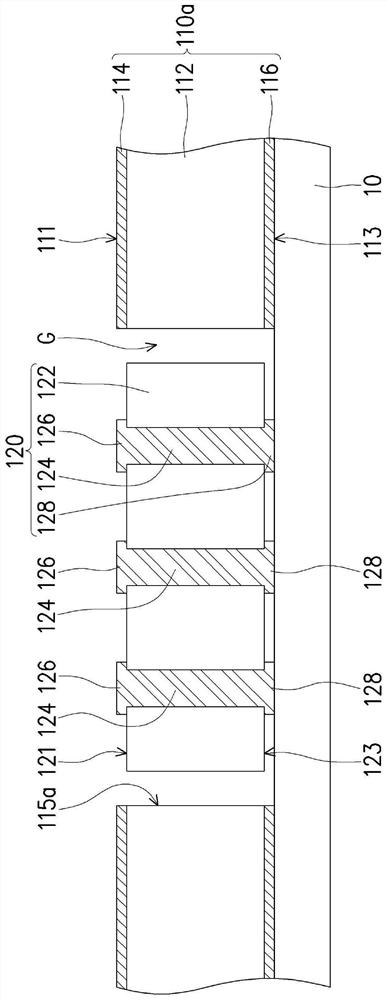

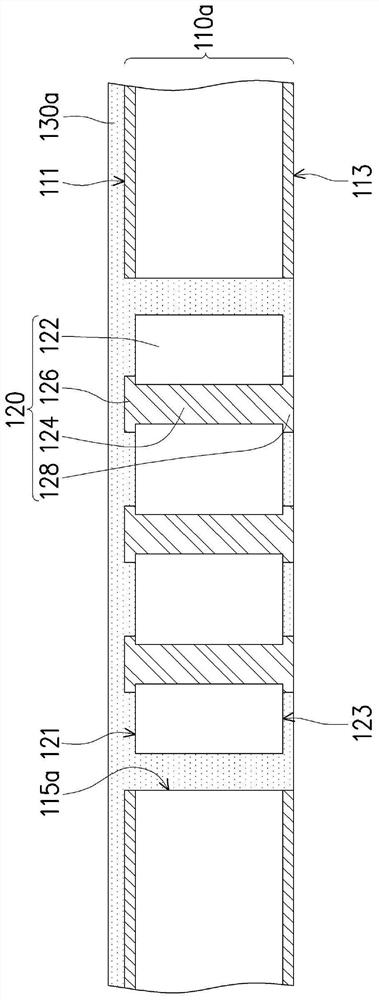

[0062] Reference will now be made in detail to the exemplary embodiments of the present invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used in the drawings and description to refer to the same or like parts.

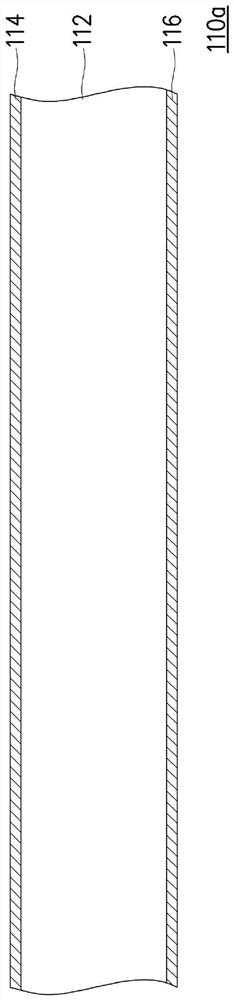

[0063] Figure 1A to Figure 1H is a schematic cross-sectional view of a manufacturing method of a package carrier according to an embodiment of the present invention. Regarding the manufacturing method of the packaging carrier of this embodiment, first, please refer to Figure 1A , providing a substrate 110a. In detail, the substrate 110a of this embodiment includes a core layer 112, a first copper foil layer 114, and a second copper foil layer 116, wherein the first copper foil layer 114 and the second copper foil layer 116 are located opposite to the core layer 112, respectively. on both surfaces. Here, the substrate 110a is, for example, a copper foil substrate, and the material of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More