Duty ratio adjusting circuit of clock signal, chip and duty ratio adjusting method

A clock signal, adjusting circuit technology, applied in information storage, digital memory information, transforming continuous pulse trains into pulse train devices with required patterns, etc. Poor and other problems, to achieve good linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The following will clearly and completely describe the technical solutions in the embodiments of the present application with reference to the accompanying drawings in the embodiments of the present application. Obviously, the described embodiments are only part of the embodiments of the present application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

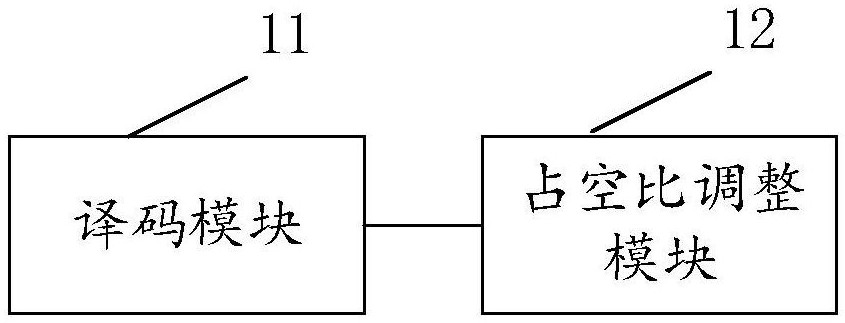

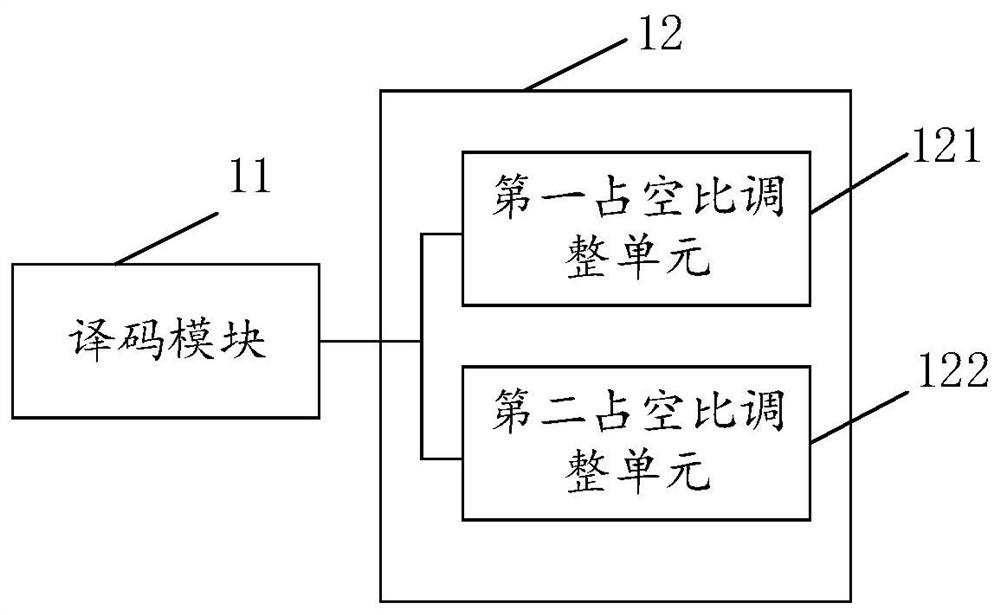

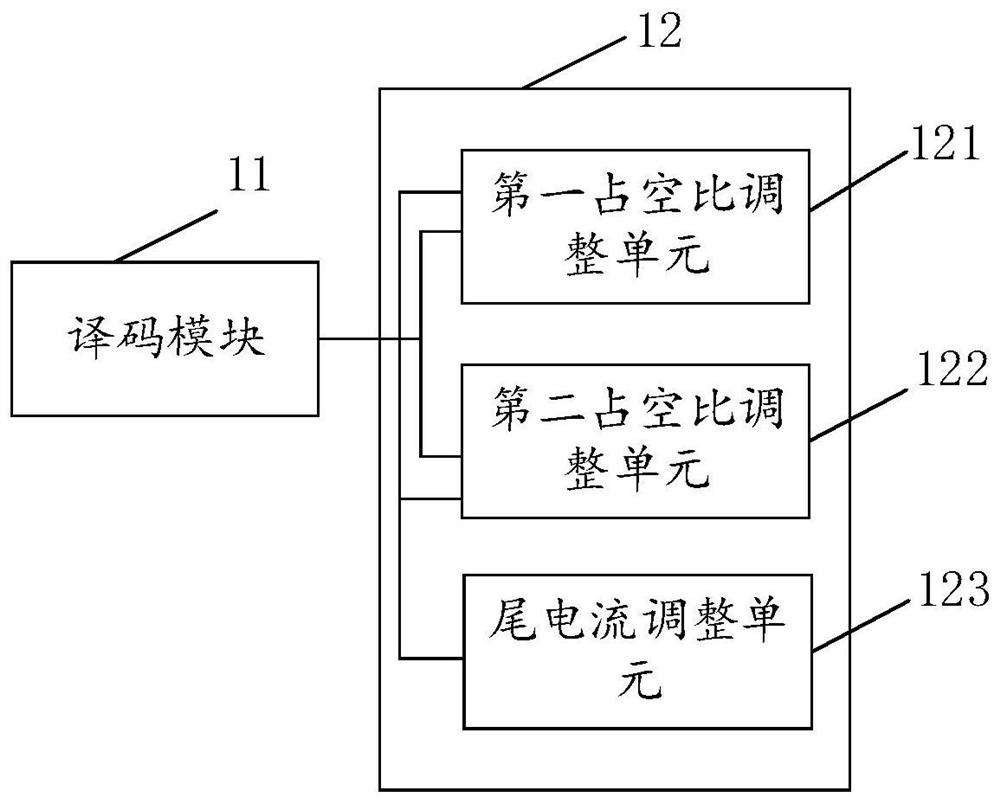

[0031] See figure 1 , is a schematic diagram of functional modules of the first embodiment of the clock signal duty ratio adjustment circuit of the present invention, specifically including: a decoding module 11 and a duty ratio adjustment module 12 .

[0032] Wherein, the decoding module 11 receives the configuration signal mrtrm, and generates the control signal SEL based on the configuration signal mrtrm. Wherein, the configuration signal mrtr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More