Error correction decoding method, storage medium and ssd device of nand flash memory chip

A flash memory chip and decoding technology, which is applied in the fields of error correction decoding, storage media and SSD equipment, can solve problems such as performance degradation and limited number of reads and writes, so as to improve the success rate, improve error correction ability, and reduce the number of attempts Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

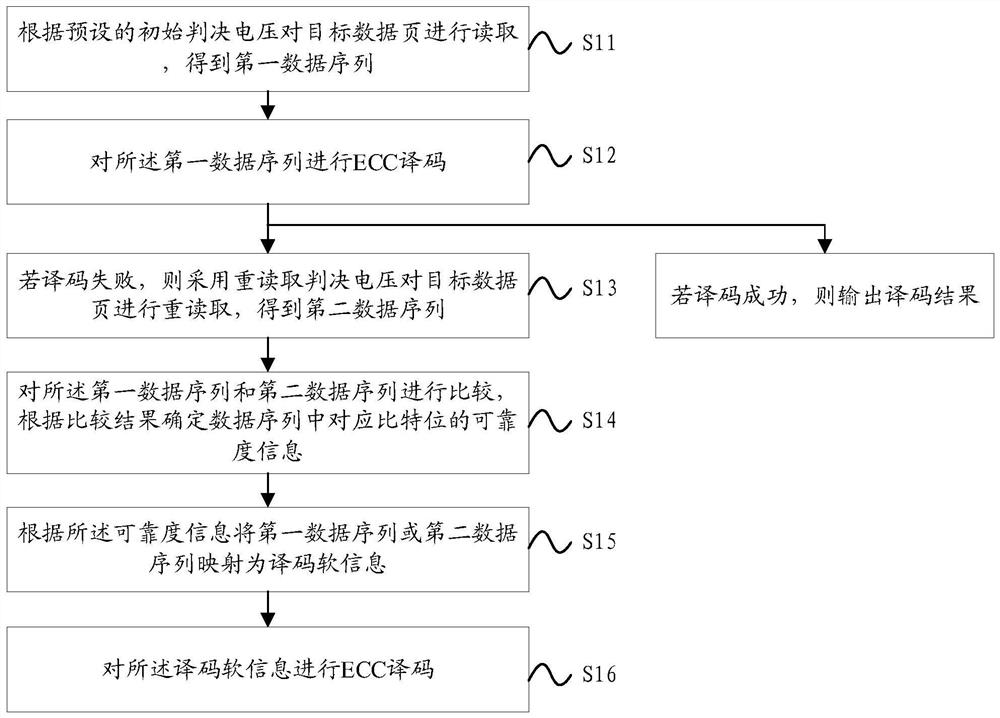

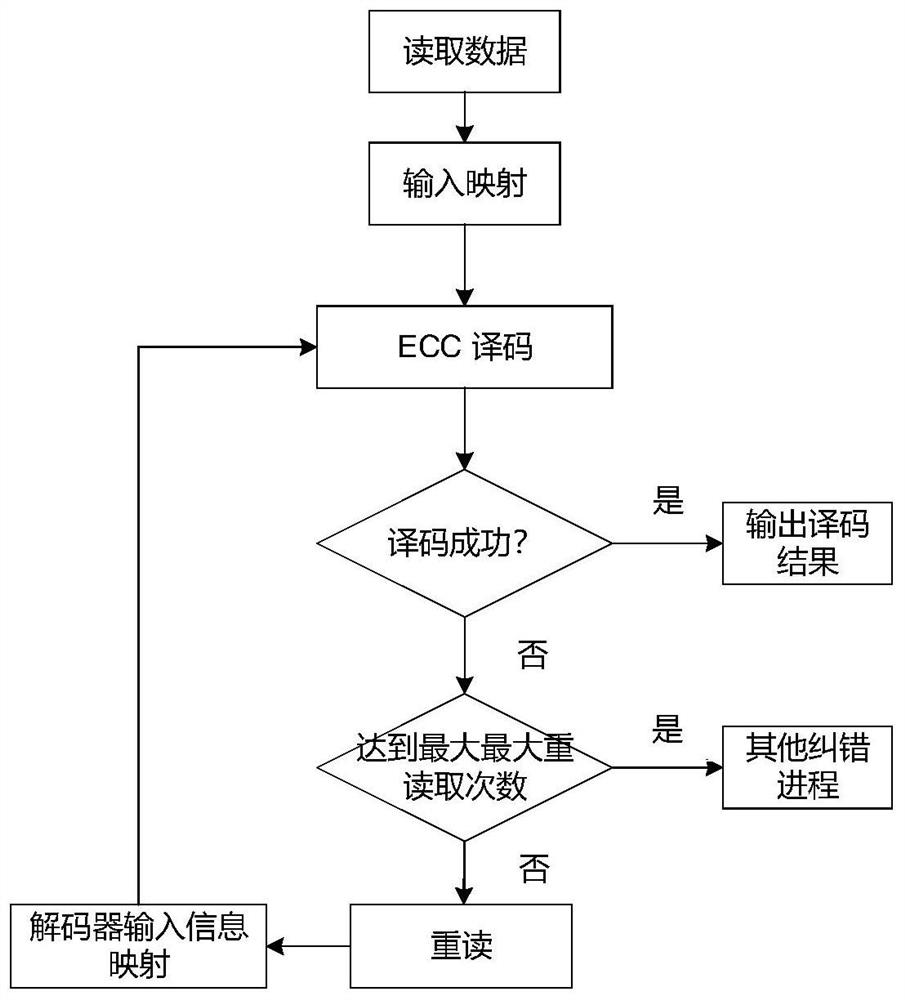

[0058] figure 1 A flowchart of an error correction decoding method for a NAND flash memory chip according to an embodiment of the present invention is schematically shown. refer to figure 1 , the error correction decoding method of the NAND flash memory chip according to the embodiment of the present invention specifically includes the following steps:

[0059] S11. Read the target data page according to the preset initial decision voltage to obtain a first data sequence.

[0060] The basic storage unit of a NAND flash memory chip is a data page (Page), and the effective capacity of each page is a multiple of 512 bytes. An SSD disk usually includes multiple NAND flash memory chips, and their operations are realized through SSD control.

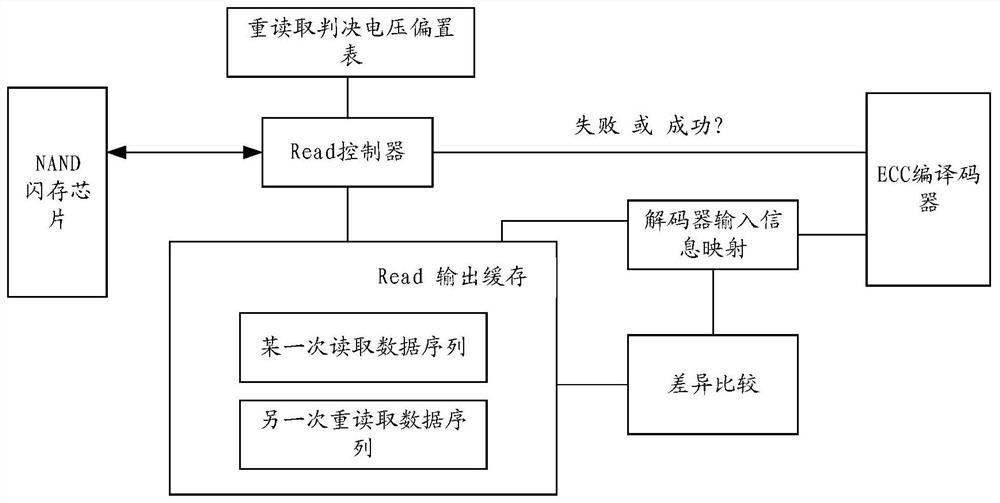

[0061] Read controller is a component of SSD controller like figure 2 As shown, the Read controller is responsible for reading data from the target data page of the NAND flash memory chip. Each read needs to configure the threshold volta...

Embodiment 2

[0115] Embodiments of the present invention further provide a computer-readable storage medium, on which a computer program is stored, and when the program is executed by a processor, implements the steps of the above error correction decoding method for a NAND flash memory chip.

Embodiment 3

[0117] An embodiment of the present invention further provides an SSD device, the SSD device includes a storage controller, the storage controller includes a memory, a processor, and a computer program stored in the memory and executable on the processor, the processor When the program is executed, the steps of the above error correction decoding method of the NAND flash memory chip are realized. E.g figure 1 S11 to S16 shown.

[0118] In the specific implementation process of the second embodiment to the third embodiment, reference may be made to the first embodiment, which has corresponding technical effects.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More