Buried gate transistor, manufacturing method thereof and semiconductor memory device

A manufacturing method and storage device technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of resistance-capacitance hysteresis and affecting the performance of semiconductor storage devices, etc., to reduce resistance-capacitance hysteresis, improve performance, and reduce power consumption The effect of loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

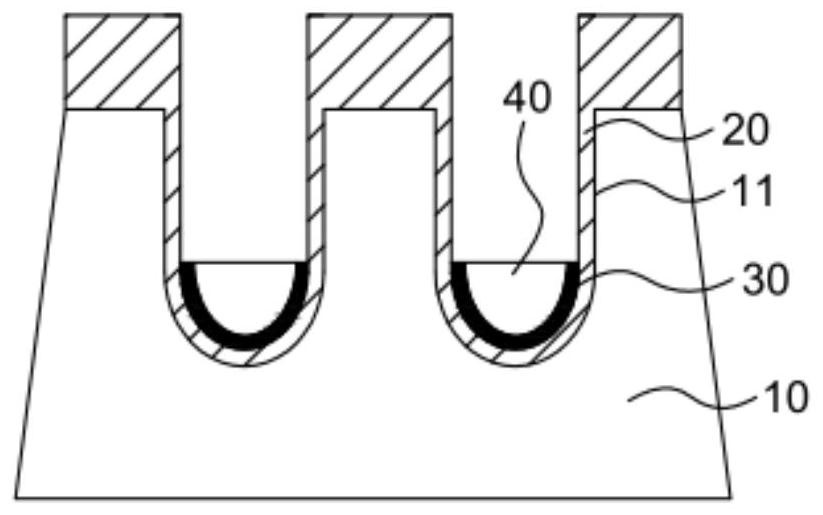

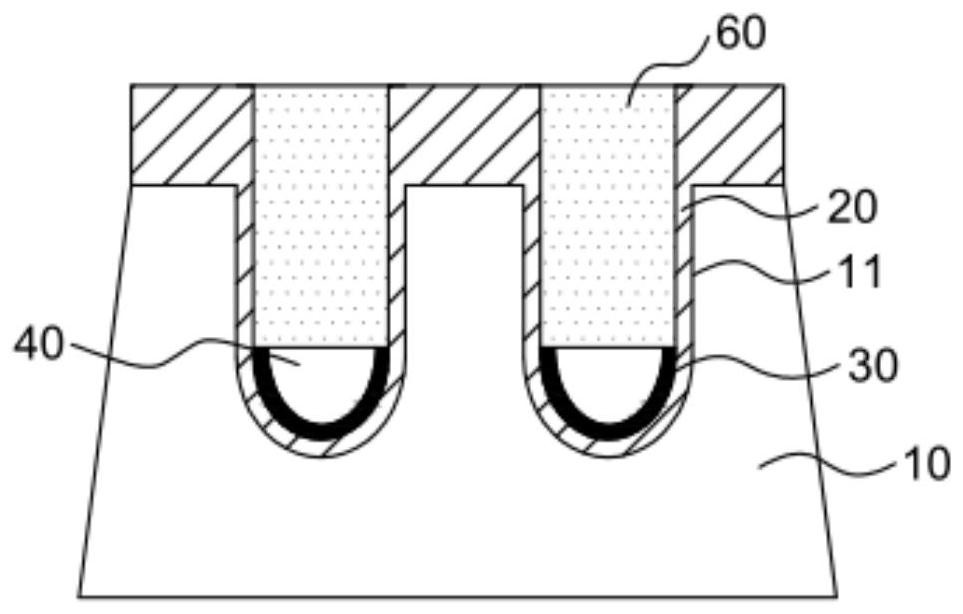

Embodiment Construction

[0030] In order to clearly describe the technical solutions of the embodiments of the present invention, in the embodiments of the present invention, words such as "first" and "second" are used to distinguish the same or similar items with basically the same function and effect. Those skilled in the art can understand that words such as "first" and "second" do not limit the number and execution order, and words such as "first" and "second" do not necessarily limit the difference.

[0031] It should be noted that, in the present invention, words such as "exemplary" or "for example" are used as examples, illustrations or illustrations. Any embodiment or design described herein as "exemplary" or "for example" should not be construed as being preferred or advantageous over other embodiments or designs. Rather, the use of words such as "exemplary" or "such as" is intended to present related concepts in a concrete manner.

[0032] In the present invention, "at least one" means one ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More