Array processor capable of avoiding loaduse risk pause under dual-mode instruction set architecture

An array processor and instruction set architecture technology, applied in the field of array processors, can solve problems such as the failure of data bypass methods, and achieve the effects of simplifying design, improving performance, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

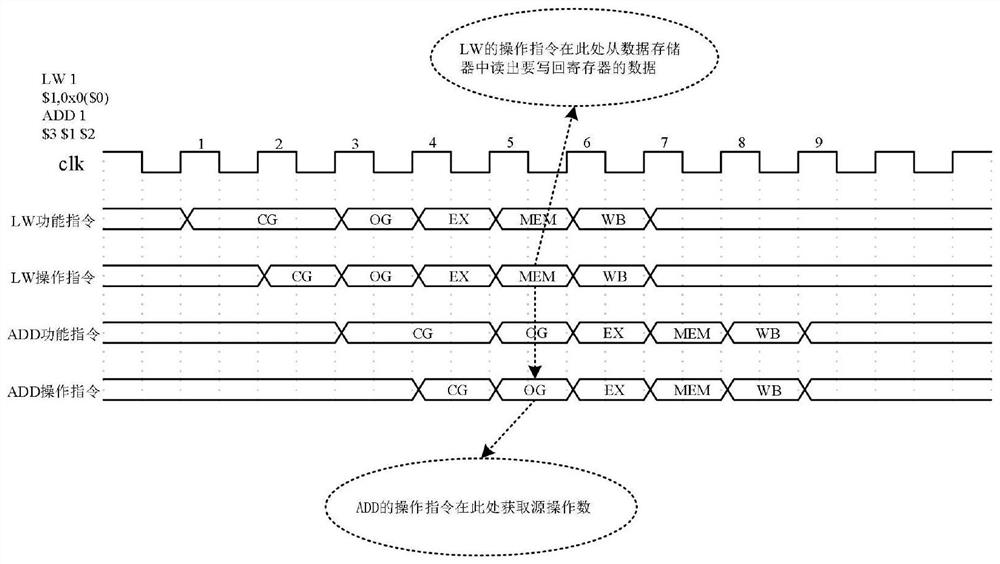

[0021] The technical solutions in this embodiment will be clearly and completely described below with reference to the accompanying drawings in this embodiment. Obviously, the described embodiments are only a part of the embodiments of this embodiment, but not all of the embodiments.

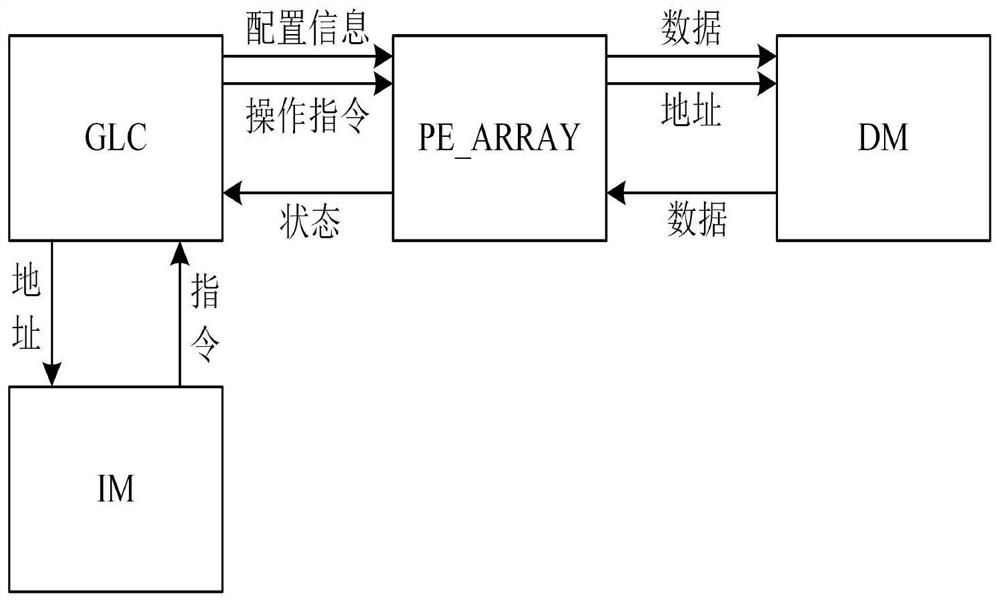

[0022] refer to Figure 1-3 , the array processor under the dual-mode instruction set architecture can avoid the load_use risky pause, including the array processor body, which includes the global controller GLC, the processing element array PE_ARRAY, the instruction memory IM, the data memory DM, the instruction memory IM and the The global controller GLC is connected, the global controller GLC is connected with the processing element array PE_ARRAY, and the processing element array PE_ARRAY is connected with the data memory DM.

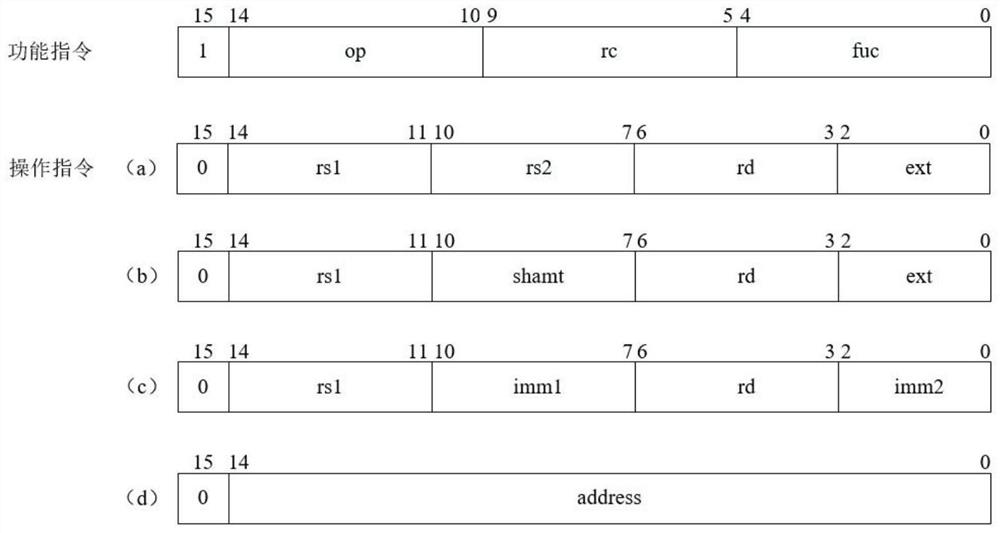

[0023] Among them, "dual mode" means that the instructions in the instruction set are divided into functional instructions for realizing control flow and operation in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More