Flash memory test method, programmable logic device, storage medium and system

A flash memory storage and testing method technology, applied in static memory, instruments, biological neural network models, etc., can solve the problem of lack of error bit rate, raw bit error rate and mean time between failures and other automated testing technologies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

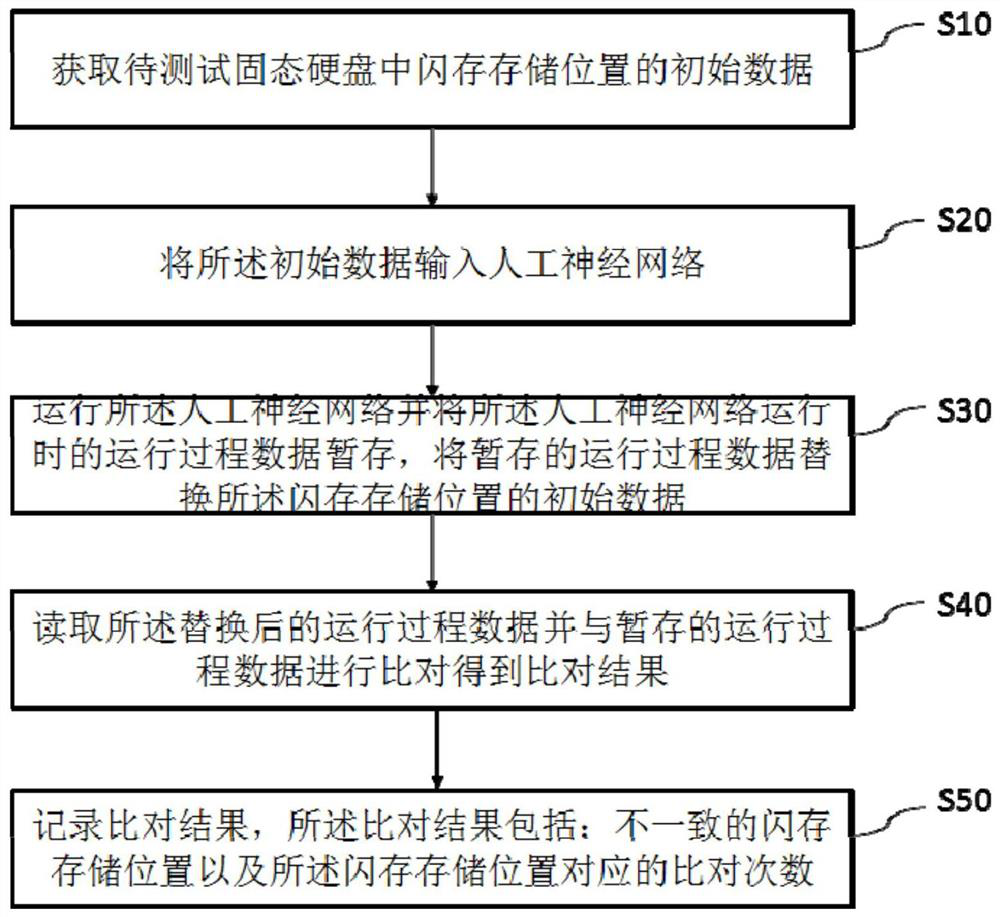

[0034] This embodiment provides a flash memory testing method, such as figure 1 shown, including the following steps:

[0035] S10. Obtain initial data of the flash memory storage location in the solid-state drive to be tested;

[0036] S20, inputting the initial data into an artificial neural network;

[0037] S30, running the artificial neural network and temporarily storing the running process data when the artificial neural network is running, and replacing the initial data of the flash memory storage location with the temporarily stored running process data;

[0038] S40, read the operating process data after the replacement and compare with the temporarily stored operating process data to obtain a comparison result;

[0039] S50. Record a comparison result, where the comparison result includes: inconsistent flash memory storage locations and the number of comparisons corresponding to the flash memory storage locations.

[0040] In this embodiment, if the comparison re...

Embodiment 2

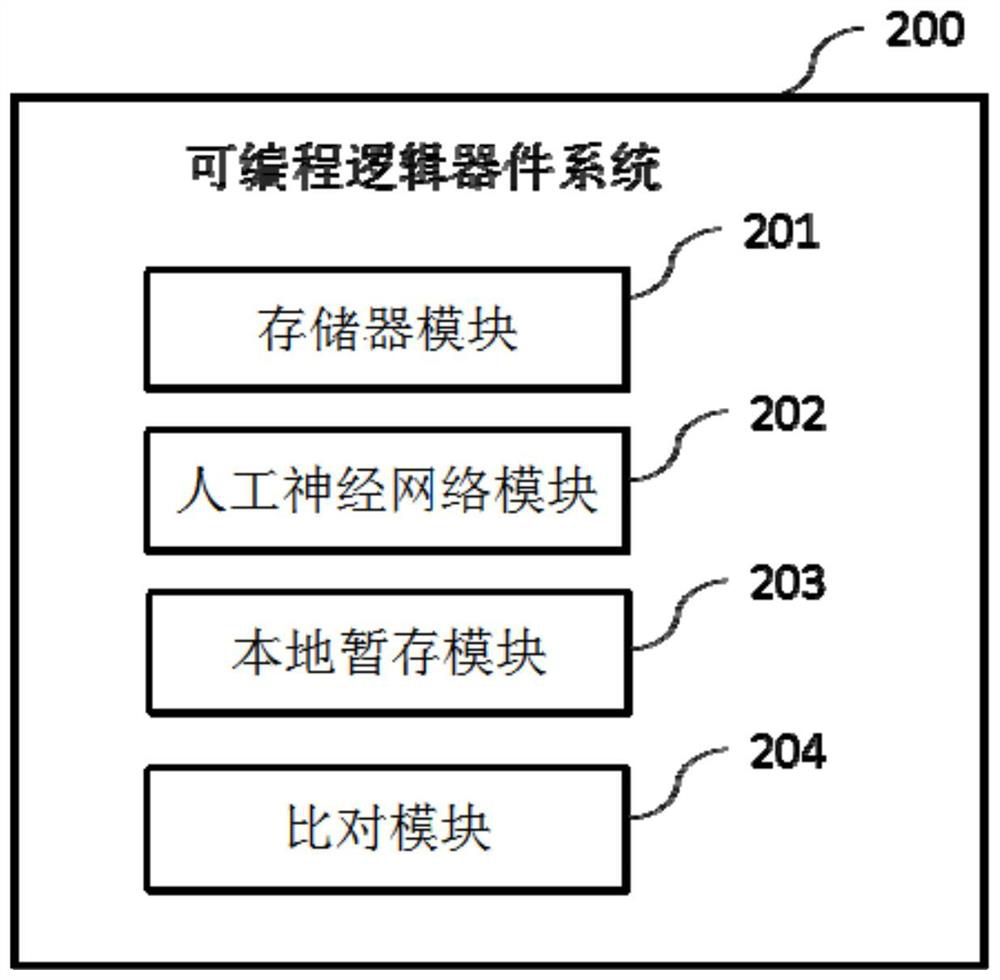

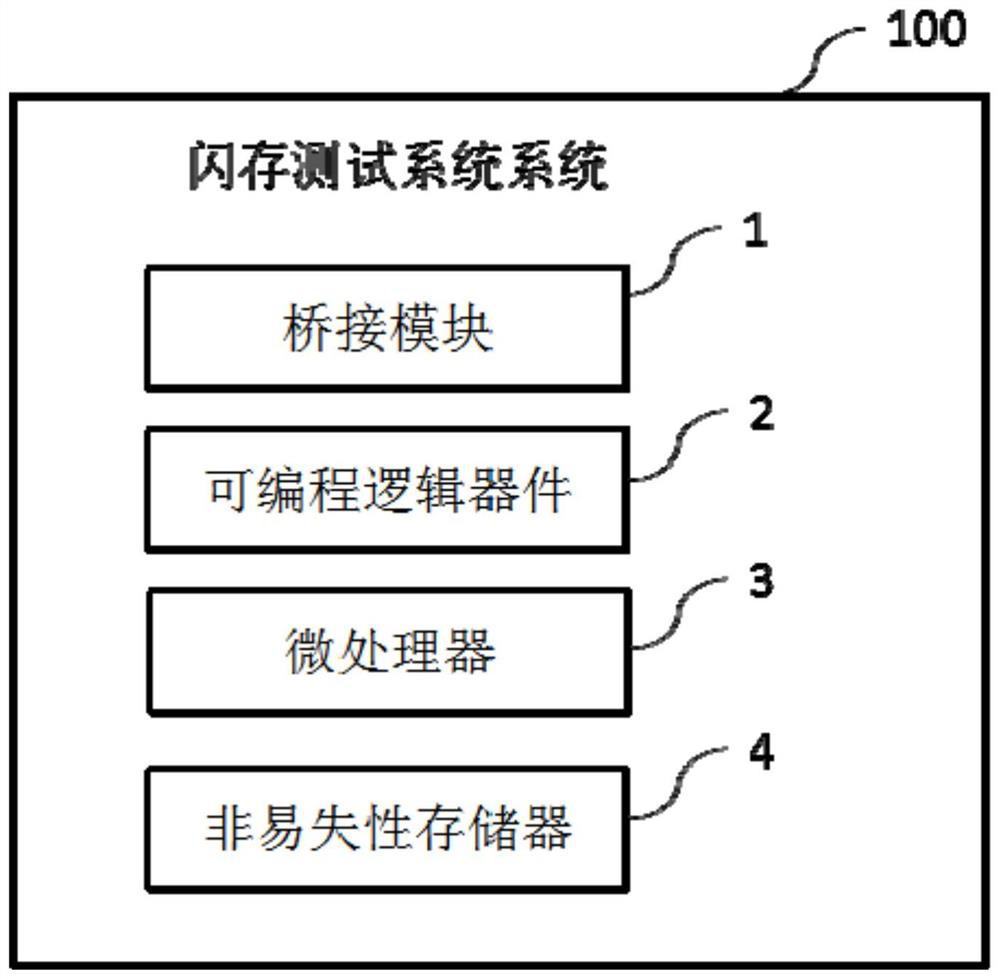

[0046] This embodiment provides a programmable logic device 2 that is configured to implement the flash memory testing method in Embodiment 1.

[0047] In this embodiment, as figure 2 As shown, the programmable logic device is connected to the bridge module 1, and the programmable logic device 2 is configured to include:

[0048] The FIFO module 201 is used to receive the read-write data converted by the bridge module 1, and output the read-write data according to the first-in, first-out mode;

[0049] The artificial neural network module 202 is used to connect multiple FIFO modules 201, input the output data of the FIFO module 201 into the artificial neural network module 202 and run the artificial neural network, and then pass the operation process data of the artificial neural network through the FIFO module. 201 and the bridging module 1 replace the data of the flash memory storage location in the solid-state disk to be tested, read the replaced data of the flash memory ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More