Method for improving readability of register model modeling code and storage medium

A model modeling and register technology, which is applied in the direction of instruments, machine execution devices, calculations, etc., can solve problems such as unintuitive, difficult to understand, reduce the efficiency of chip design and verification process, and achieve the effect of saving time and improving work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

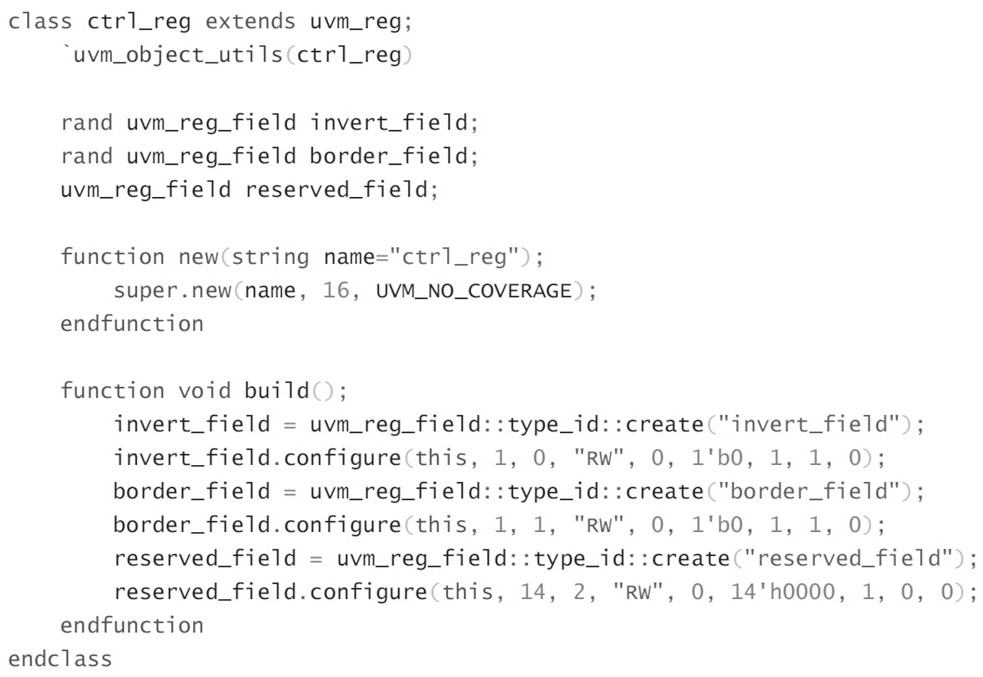

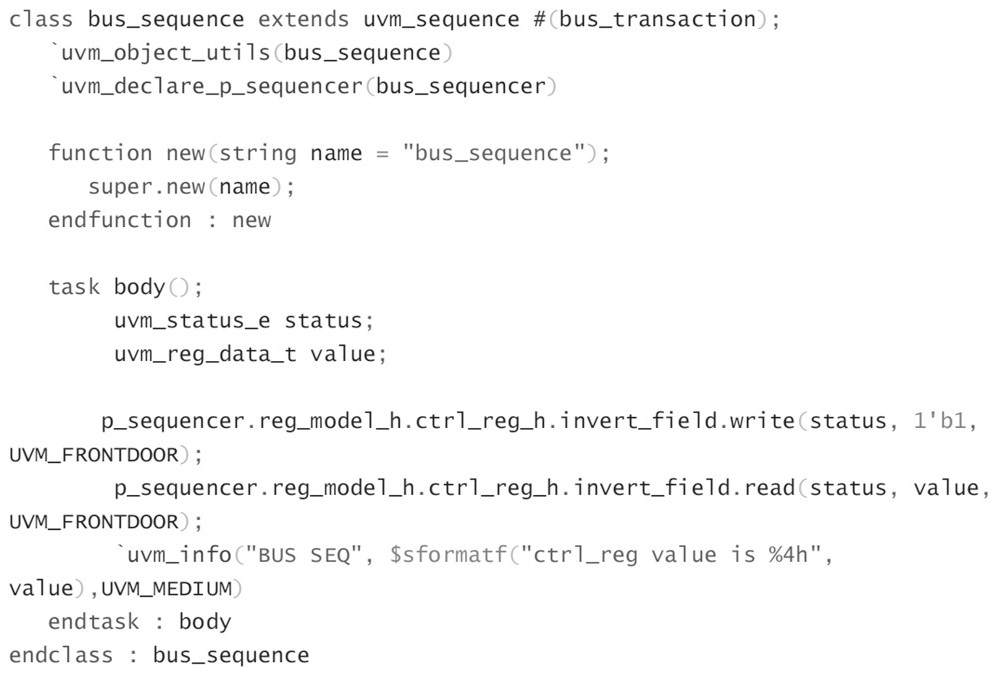

[0034] The preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings to further illustrate the present invention.

[0035] First, combine Figure 4~6 The method for improving code readability for modeling a register model according to an embodiment of the present invention is described, which is used for chip verification and has a wide range of application scenarios.

[0036] like Figure 4~5 As shown, the method for improving the readability of a code for modeling a register model according to an embodiment of the present invention includes the following steps:

[0037] In S1, as in Figure 4 As shown, create a UVM register model, derive the field base class uvm_reg_field of the UVM register model, and generate a subclass my_reg_enum_field.

[0038] In S2, as in Figure 4 As shown, extend or add a series of interface methods in the subclass my_reg_enum_field to support method calls of enumeration type val...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More