Semiconductor integrated circuit device capable of inhibiting noise and supplying power potential

A technology of integrated circuits and semiconductors, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficult supply and high voltage, and achieve the effect of suppressing the increase of chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

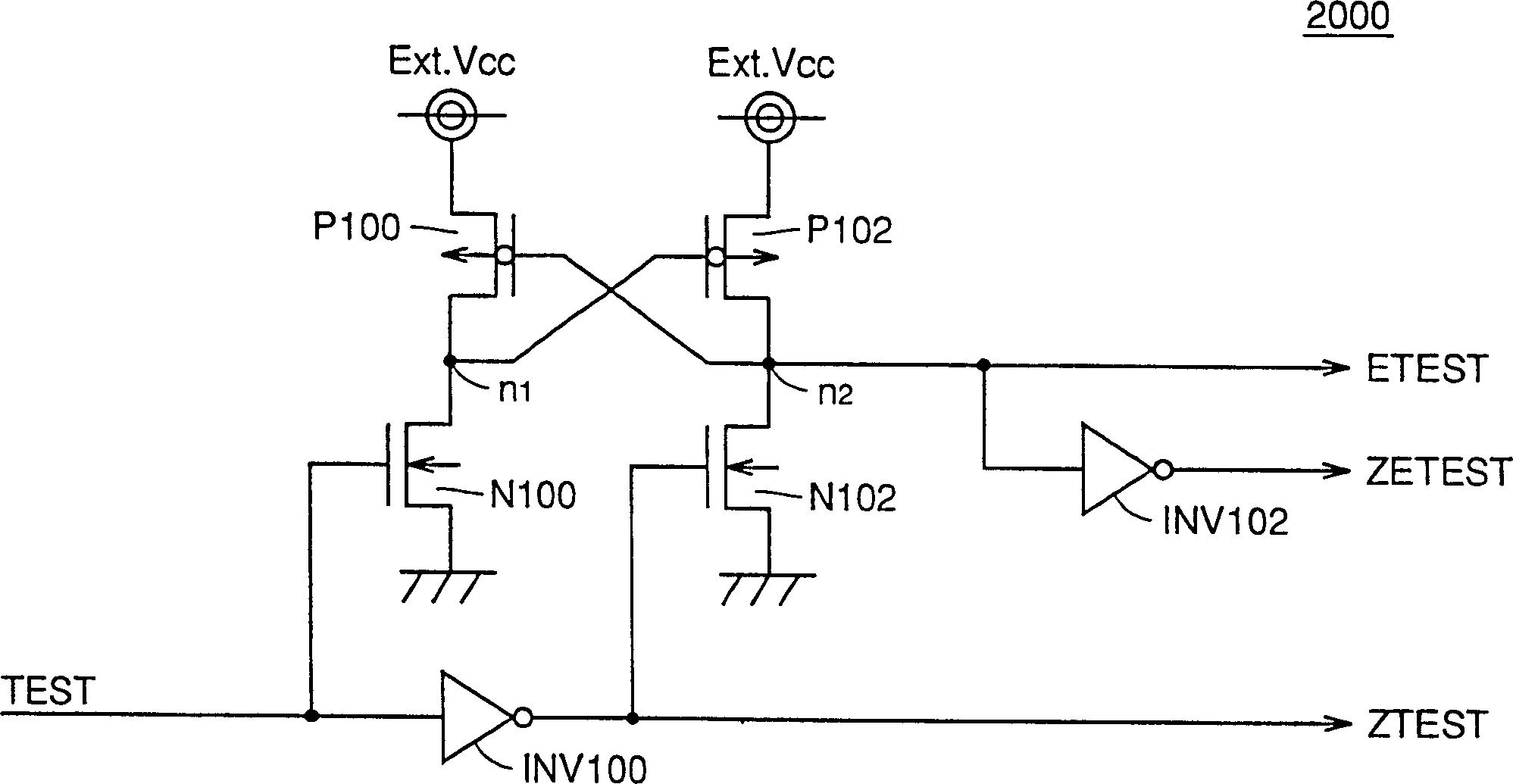

[0097] FIG. 6 is a circuit diagram showing the configuration of a coupling circuit 2102 mounted in the semiconductor memory device according to Embodiment 2 of the present invention.

[0098] The structure of the other parts of the semiconductor storage device of the second embodiment is the same as that of the semiconductor storage device of the first embodiment, and therefore description thereof will not be repeated.

[0099] Referring to FIG. 6, the coupling circuit 2102 has P-channel MOS transistors P212 and P214 connected in series between the terminal 118 and the internal power supply node ns1 (and ns2), and a gate potential coupled between the terminal 118 and the gate of the transistor P212. The P-channel MOS transistor 210 controlled by the signal TEST and the N-channel MOS transistor N210 coupled between the ground potential GND and the gate potential of the transistor P212 is controlled by the signal ETEST. The gate potential of the transistor P214 provided on the i...

Embodiment 3

[0112] FIG. 7 is a circuit diagram showing the configuration of a coupling circuit 2104 mounted in the semiconductor memory device according to Embodiment 3 of the present invention.

[0113] The structure of the other parts of the semiconductor storage device of the third embodiment is the same as that of the semiconductor storage device of the first embodiment, and therefore description thereof will not be repeated.

[0114] Referring to FIG. 7, the coupling circuit 2104 has N-channel MOS transistors N112 and N114 connected in series between the terminal 118 and the internal power supply node ns1 (and ns2), and a gate potential coupled between the terminal 118 and the gate of the transistor N112. An N-channel MOS transistor N110 controlled by a signal ZTEST, and a P-channel MOS transistor P110 whose gate potential is controlled by a signal ZETEST is coupled between the external power supply potential Ext. Vcc and the gate of the transistor N112. The gate potential of the tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More