Output buffering device and method

An output device, output buffer technology, applied in pulse technology, logic circuit connection/interface layout, electrical components, etc., can solve problems such as increased noise and distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

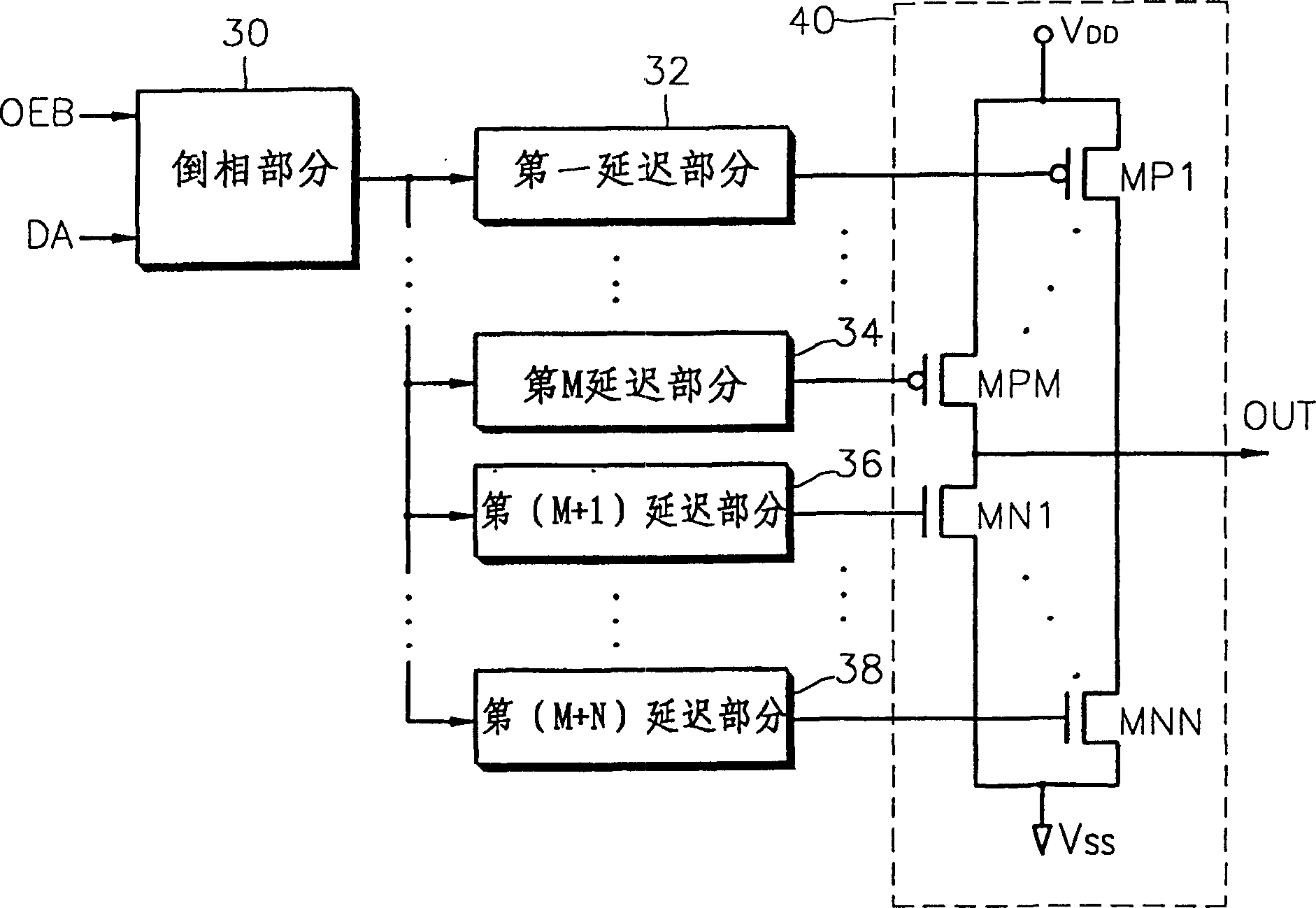

[0033] Depend on figure 2 It can be seen that the output buffer constituted by a preferred embodiment of the present invention includes an inverting part 30, first to M delay parts 32 to 34, (M+1) to (M+N) delay parts 36 to 38 , and a data output part 40 composed of first to Mth pull-up transistors MP1 to MPM and first to Nth pull-down transistors MN1 to MNN.

[0034] figure 2The inverting part 30 shown in inverts the input data DA and outputs it to the first to Mth delay parts 32 to 34 and the (M+1) to (M+N) delay parts 36 to 38 (wherein M and N each is a positive integer equal to or greater than 2). The inverting part 30 works under the action of the output enable signal OEB to invert the input data DA. The first to M delay sections 32 to 34 and the (M+1) to (M+N) delay sections 36 to 38 delay the inverted input data for M+N different delay times every T / ( M+N) times are sent to the data output section 40 one by one (where T is the time required for the level change of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More