Configuration memory implementation for lut-based reconfigurable logic architectures

A technology for reconfiguration and memory cells, applied in the field of address decoders, which can solve problems such as affecting the quality of terminal equipment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Therefore, first some currently known related solutions will be described in more detail. Embodiments according to the present invention will then be described in more detail. The configuration memory architecture and its implementation are largely determined by the programming method chosen for any RL device. In current RL devices, three basic programming (configuration) methods can be identified. They are:

[0033] 1. Serial configuration

[0034] 2. Parallel configuration

[0035] 3. Serial-parallel configuration.

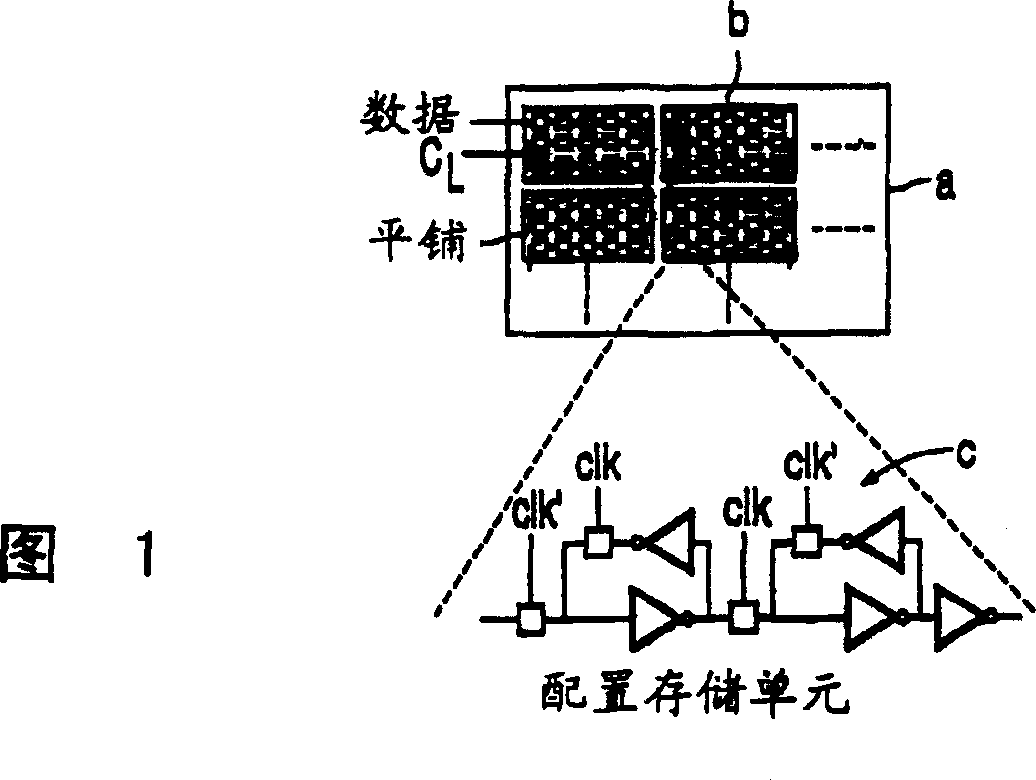

[0036] Figure 1 schematically shows a reconfigurable device, which is reconfigured in a serial configuration method. According to this method, the programming of the RL device is performed serially. To achieve this, configuration memory cells c of all tiles b of device a are connected in a single long scan chain. Data bits in such a scan chain are shifted with successive clock pulses. The advantage of this scheme is that only two pins are needed t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More