Method for making device with transistors of different types

A transistor and type of technology, applied in the direction of transistors, semiconductor devices, electric solid-state devices, etc., to achieve the effects of improving gate depletion, increasing production time, and high electron mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

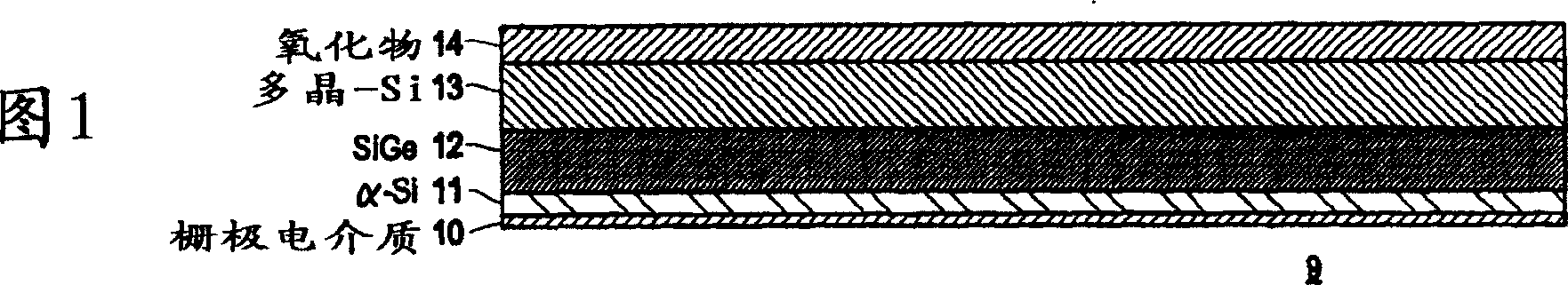

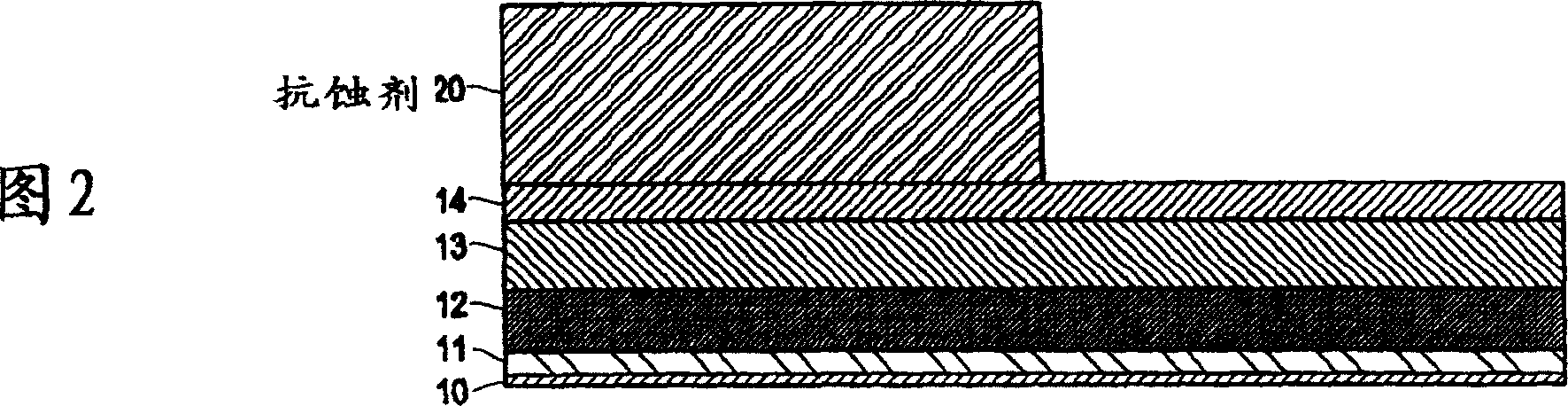

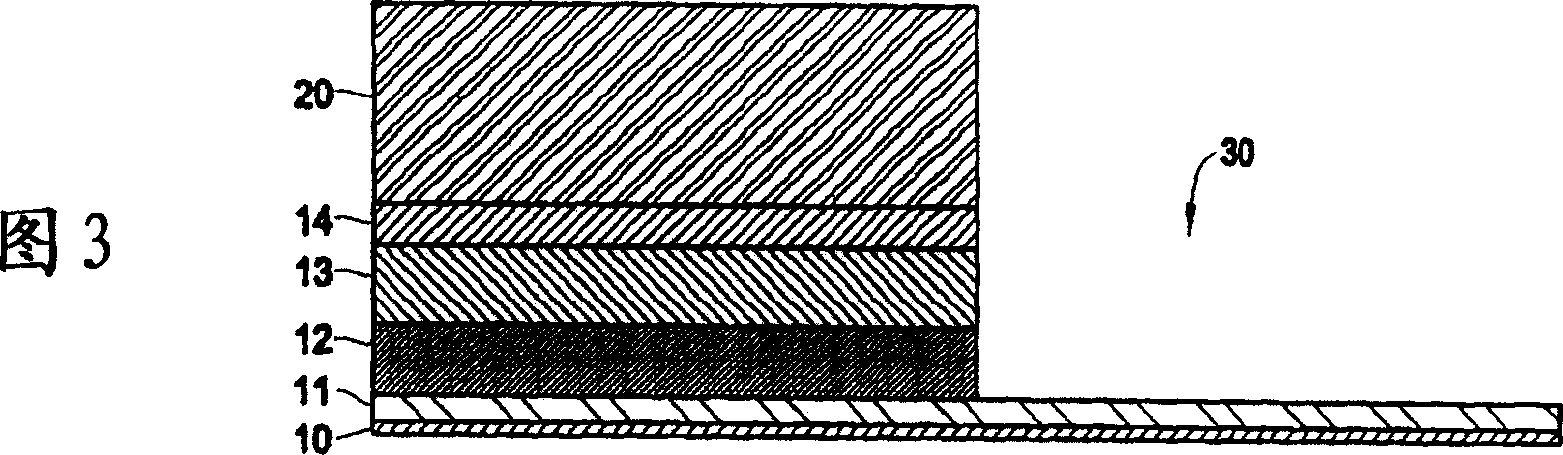

[0025] As described above, the present invention provides a process in which gate oxides can be formed simultaneously for all transistors of different materials and in which all gate conductors of transistors can be patterned simultaneously. This is shown in more detail in the partial cross-sectional schematic view of the integrated circuit shown in Figures 1-10. More specifically, FIG. 1 illustrates growth of a gate dielectric, which may be an oxide, oxynitride, or high-k dielectric (any compatible type), on a base substrate 9, which may be bulk silicon or silicon-on-insulator. A gate dielectric 10 is formed in the upper portion of the substrate 9 . Then an amorphous silicon layer 11 , a silicon germanium layer 12 and a polysilicon layer 13 are sequentially deposited on the gate dielectric 10 . The present invention may use any conventional deposition process such as any form of chemical vapor deposition (CVD) or physical vapor deposition (PVD) or any other known deposition ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More