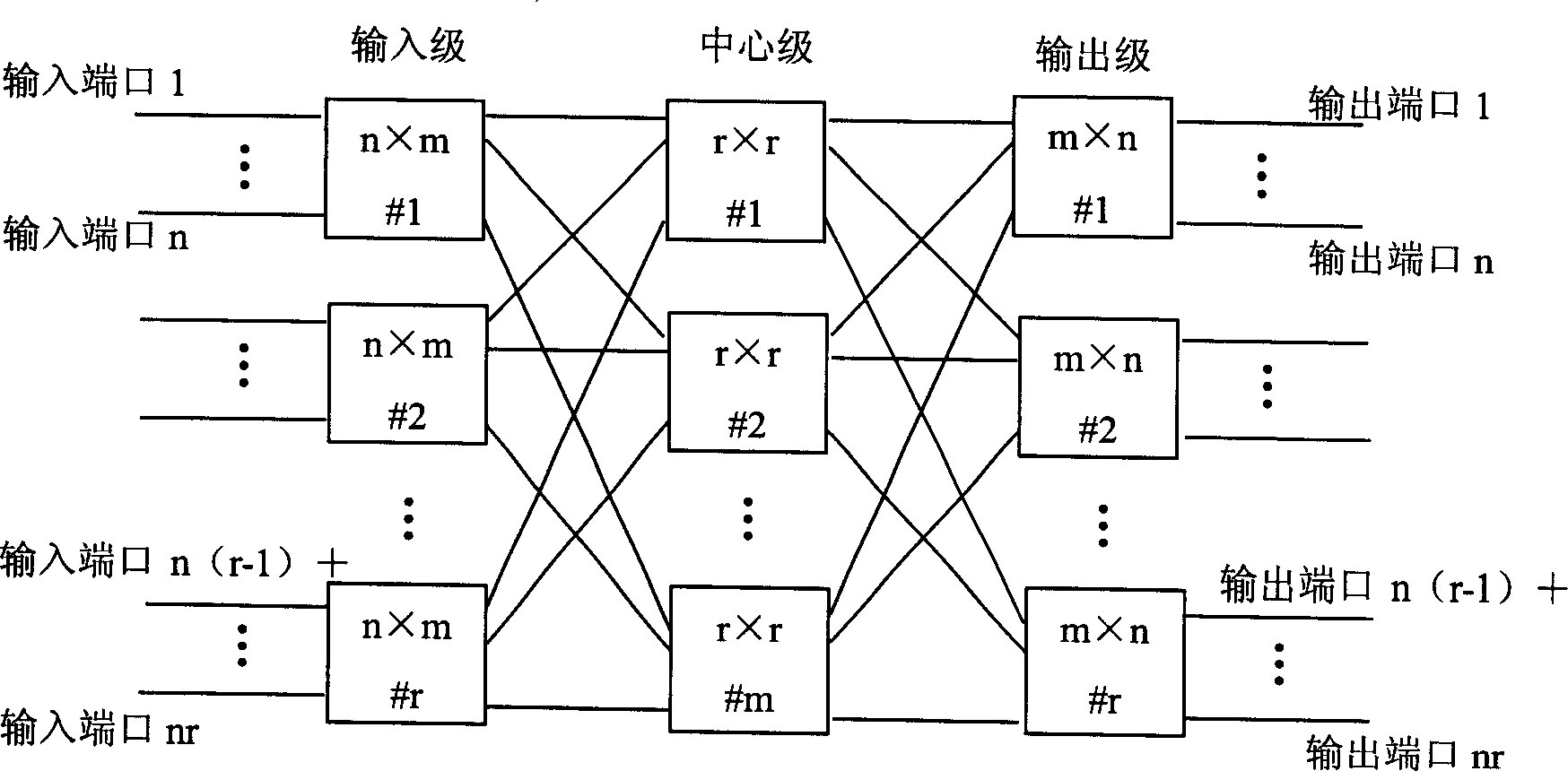

Non-blocking expansion method of three-level Clouse matrix

An expansion method and non-blocking technology, which is applied in the direction of digital transmission system, selection device of multiplexing system, electrical components, etc., can solve the problem that non-blocking cannot be realized

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

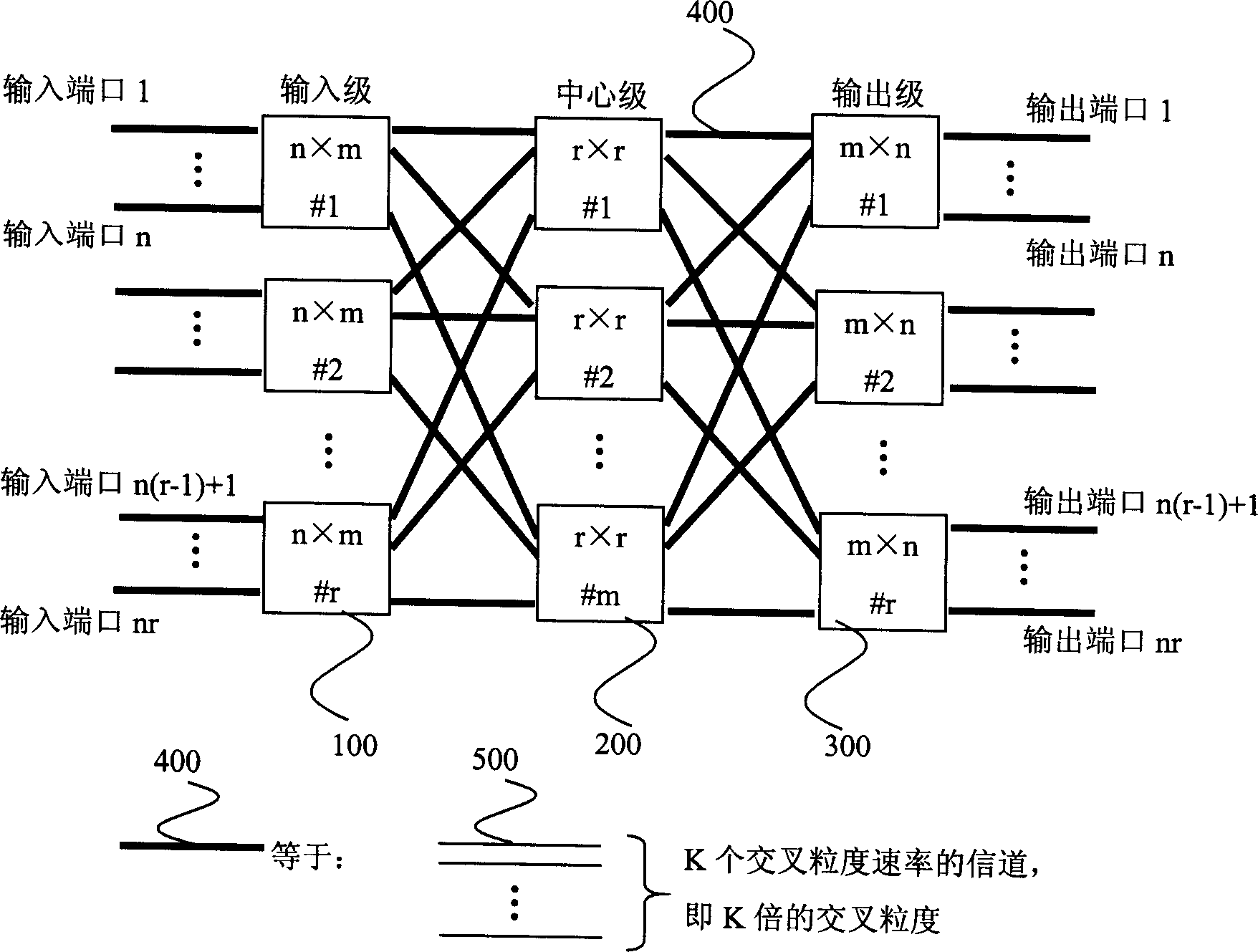

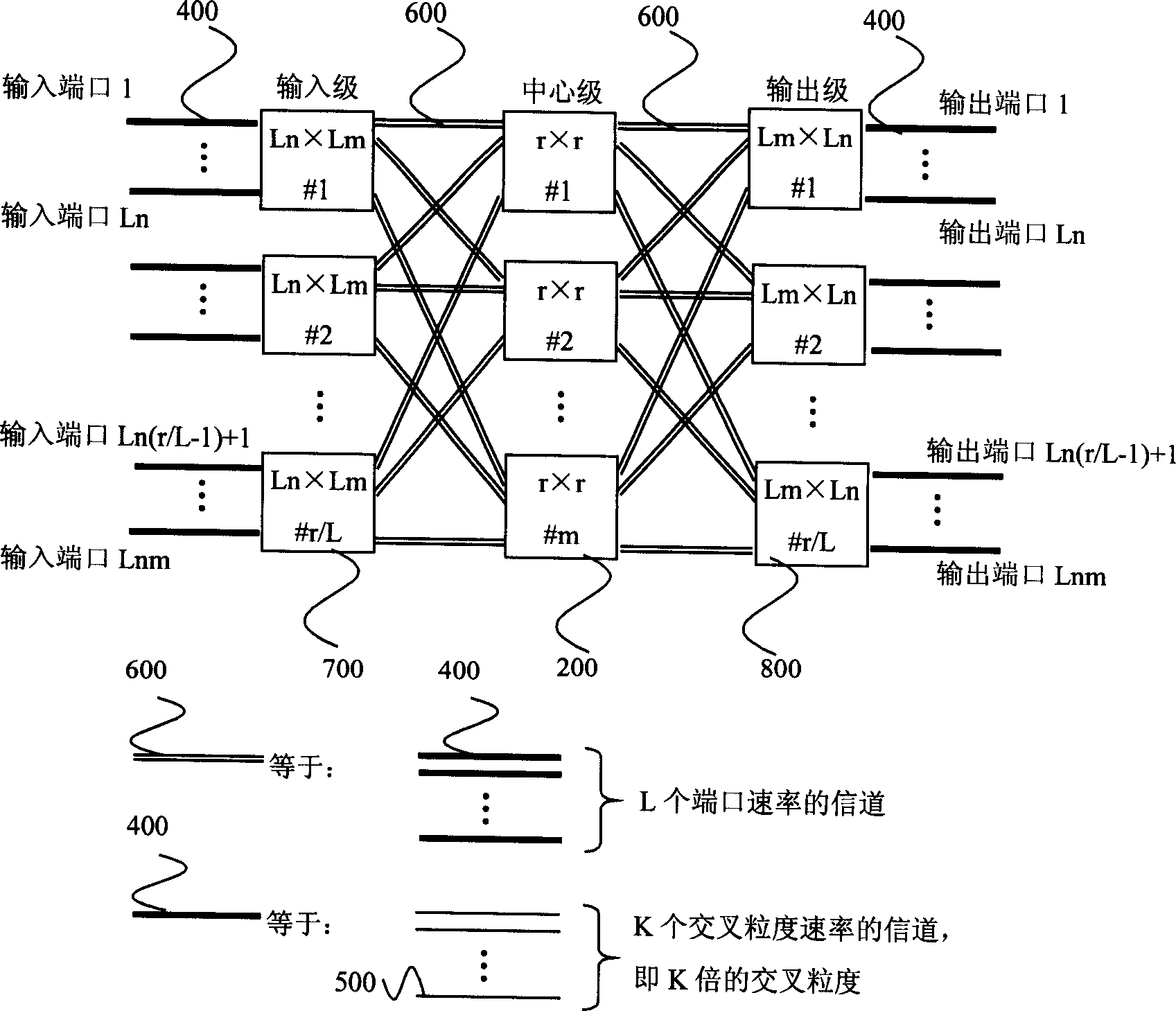

[0036] Combine below Figure 5 to Figure 10 The illustrated examples further illustrate the method of the invention. It is worth mentioning that these examples are only for illustrating the present invention, rather than limiting the present invention.

[0037] Figure 5 It is the first embodiment of the first method of the present invention. Among them, 64 input-level unit cross-matrix modules (110) 8×16, 16 intermediate-level unit cross-matrix modules (210) 64×64, and 64 output-level unit cross-matrix modules (310) 16×8 chips are used to establish three-stage Clos (Clos) matrix (the above numbers refer to the number of ports, the port speed of the chip used in the figure is 622M, and the crossover granularity is VC3 or VC4). The data rate per port is 622Mb / s (778Mb / s if 8B / 10B encoding is used). There is one 622Mb / s channel connected between each input / output chip and each chip of the intermediate stage, as shown by channel 410 in the figure. Each 622Mb / s channel uses T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More