Arithmetic device and encryption/decryption device

A technology of encryptor and decryptor, which is applied to encryption devices with shift registers/memory, countermeasures to attack encryption mechanisms, instruments, etc., and can solve problems such as increasing the power consumption of calculator 100

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

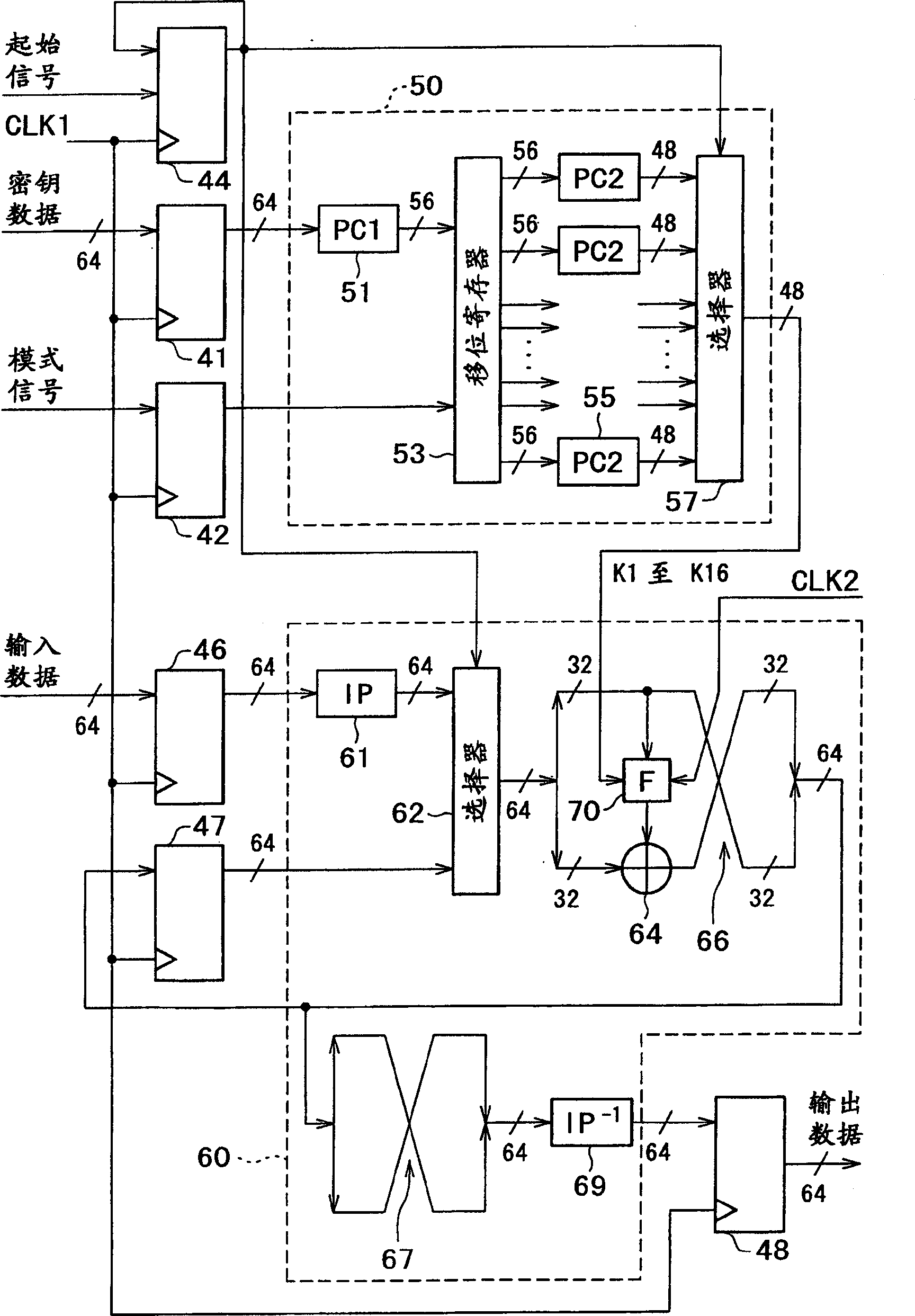

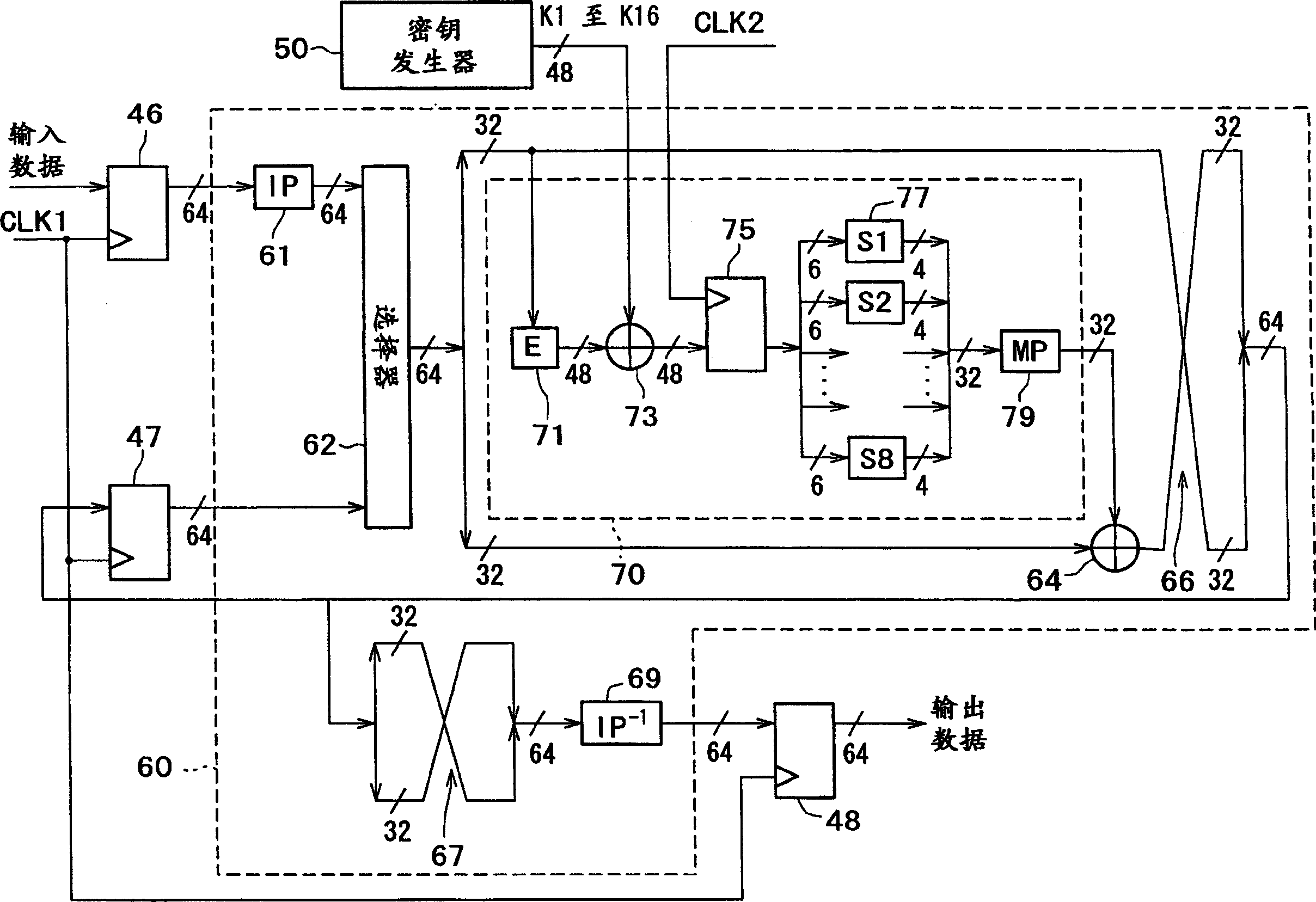

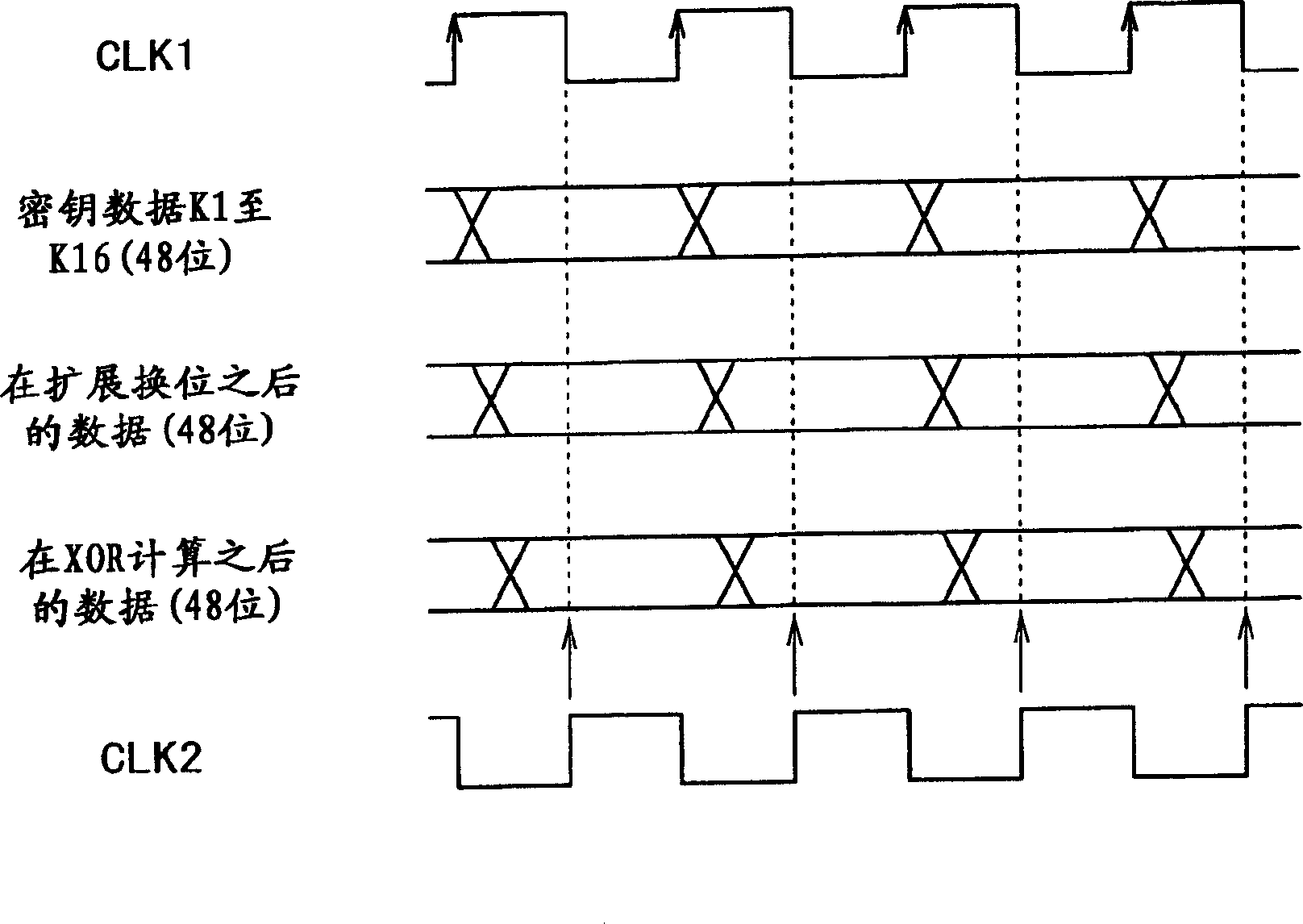

[0020] [Example of computing device: Figure 1-3 ]

[0021] figure 1 with 2 An embodiment representing a computing device of the present invention is shown configured as an encryption / decryption computing device, wherein, figure 2 show figure 1 Details of conversion circuitry 70 within calculator 60 are shown.

[0022] The encryption algorithm adopted in the encryption / decryption computing device of this embodiment conforms to the DES encryption algorithm.

[0023] Key data (secret key) and input data (plain text data or encrypted text data) each consist of 64 bits, and are latched in latch circuits 41 and 46 according to clock CLK1, respectively.

[0024] Also, a mode signal representing encryption or decryption is latched in the latch circuit 42 based on the clock CLK1. Furthermore, the clock CLK1 is counted by the 16-stage counter 44 from the start signal time point.

[0025] The key data output from the latch circuit 41, the mode signal output from the latch circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More