VLSI realizing method of synchronous flowing arithmetic coder

An arithmetic encoder and implementation method technology, applied in the field of VLSI design, can solve the problems of not giving key circuits and CX table operations, not considering the optimization of the critical path of the arithmetic encoder pipeline, key circuit implementation and auxiliary steps, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further described in detail below in conjunction with the accompanying drawings and the embodiments given by the inventor.

[0023] A brief description of the process of the arithmetic encoder of JPEG2000:

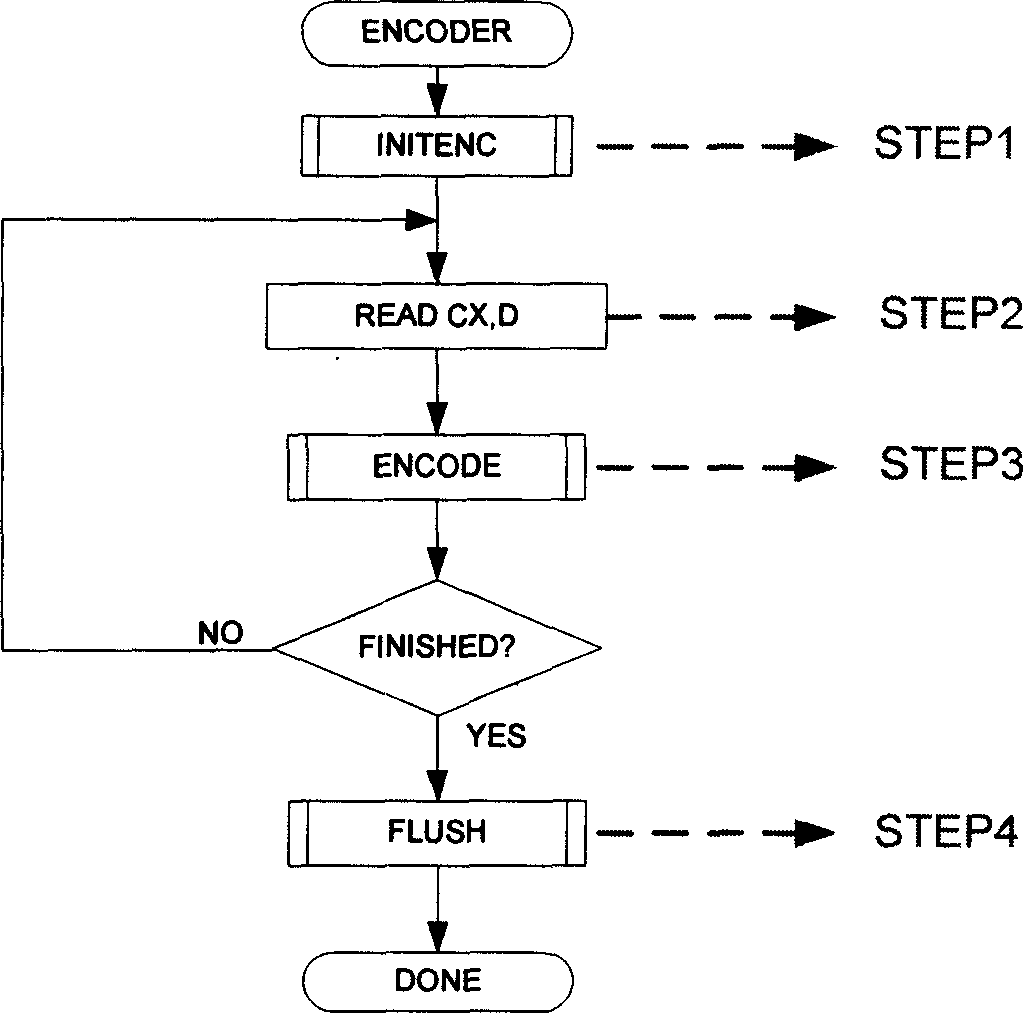

[0024] step1: INITENC: the register called when initializing the encoding

[0025] step2: read in CX (context label1), D (0, 1)

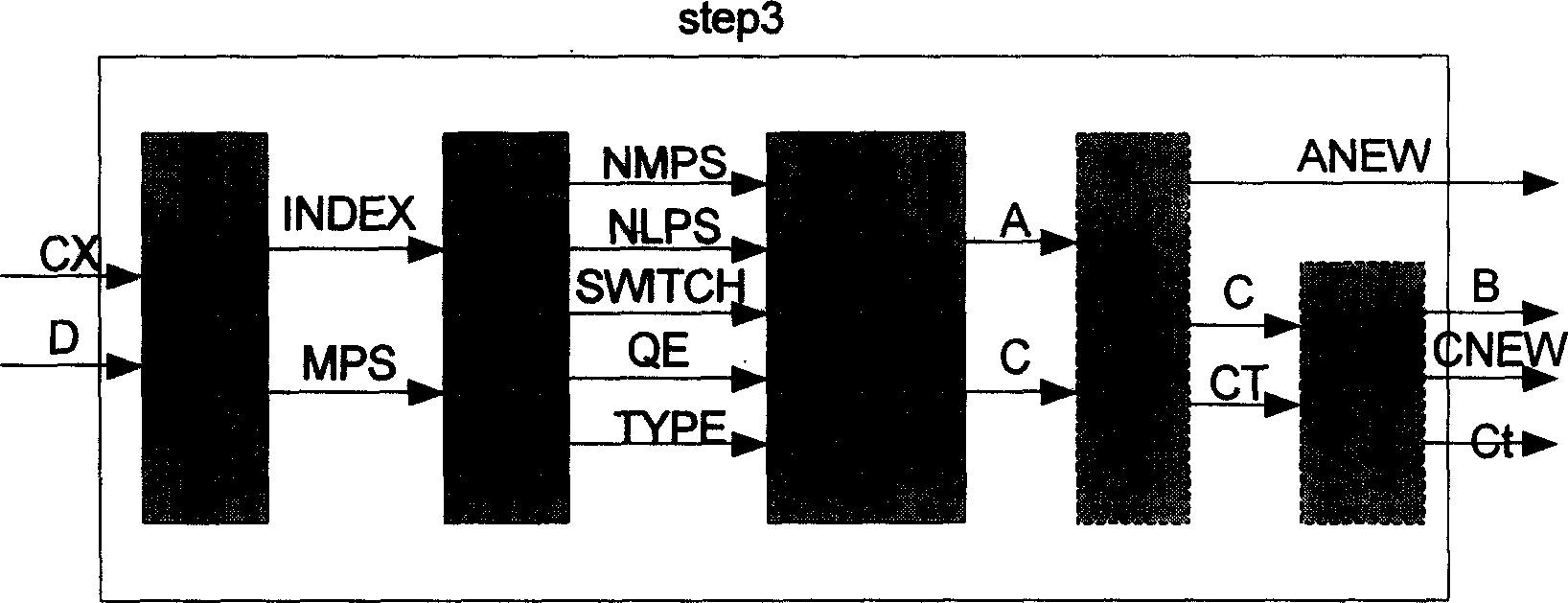

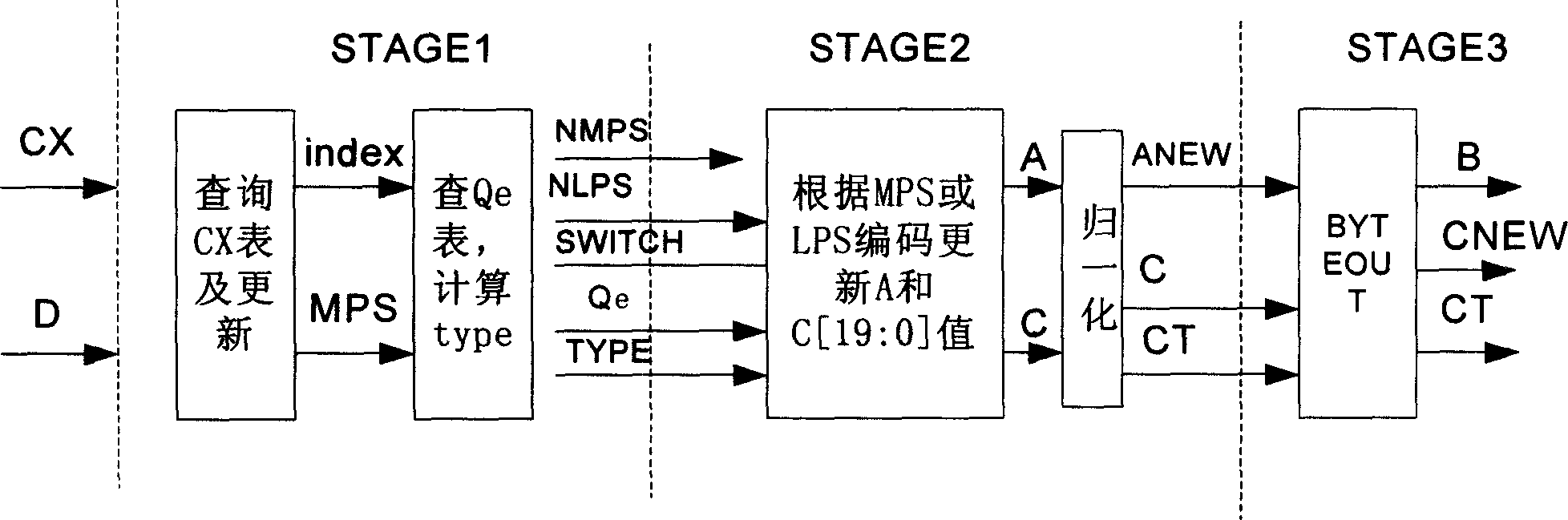

[0026] step3: Encoding (ENCODE), RENORME needs to be introduced in the encoding.

[0027] CODEMPS Conditions:

[0028] ((D=0)&(MPS(CX)=0))||((D=1)&(MPS(CX)=1))

[0029] CODELPS conditions:

[0030] ((D=1)&(MpS(CX)=0))||((D=0)&(MPS(CX)=1))

[0031] step4: FLUSH, output the data in REGC and cache after encoding.

[0032] The process of step3 is as follows figure 2 As shown, when A=0X8000H, and when CT is 0, the coded stream is output to the buffer (byteout). It can be seen that a complete encoding process requires at least 4 clock cycles. If normalization is required...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More