Method for manufacturing semiconductor chip

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, manufacturing tools, etc., can solve problems such as damage to semiconductor wafers, cracking and breakage of semiconductor chips, and deformation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

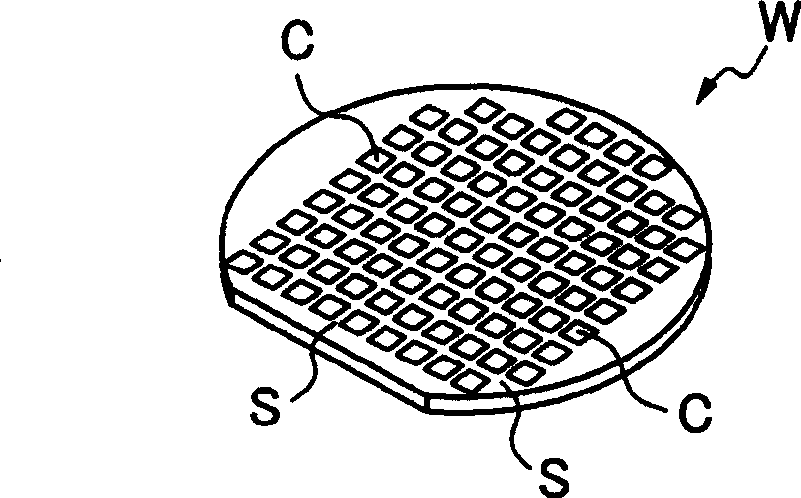

[0024] As a preferred mode for implementing the present invention, the following describes the figure 1 The shown method is a method in which the back surface of a semiconductor wafer W is ground, and channels S are cut (diced) vertically and horizontally to manufacture individual semiconductor chips C.

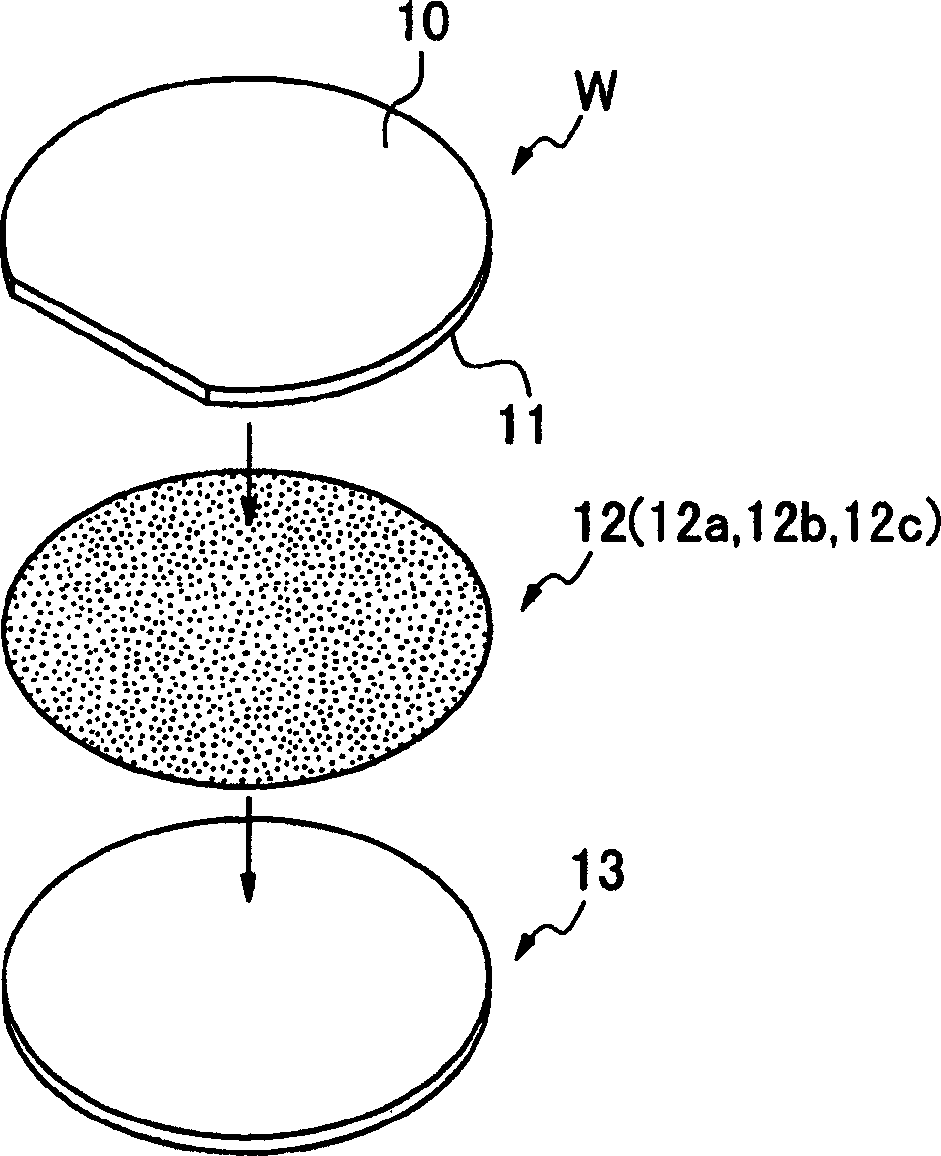

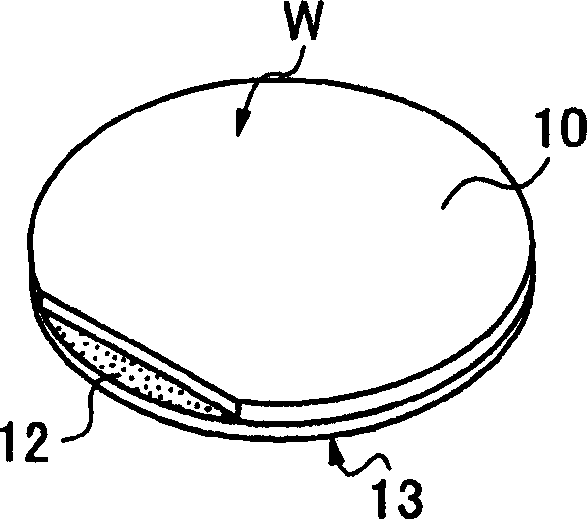

[0025] exist figure 1 In the shown semiconductor wafer W, circuits are formed on the surface of the regions divided by the channels S. As shown in FIG. Such as figure 2 As shown, in the state where the semiconductor wafer W is turned over so that the back surface 10 faces upward, the surface of the semiconductor wafer W is pasted on the support plate 13 through the adhesive sheet 12, as shown in FIG. image 3 It is shown as one (support plate integration process). That is, the surface 11 of the semiconductor wafer W is pasted on the adhesive sheet 12 .

[0026] The adhesive sheet 12 has a property of reducing the adhesive force by excitation, and is, for example, an ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More