Circuit and method for encoding data and data recorder

A data and circuit technology, applied in the field of product coding and adding, can solve the problems of increased memory power consumption, loss of real-time recording operation, expensive memory, etc., and achieve the effect of reducing the operating clock frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

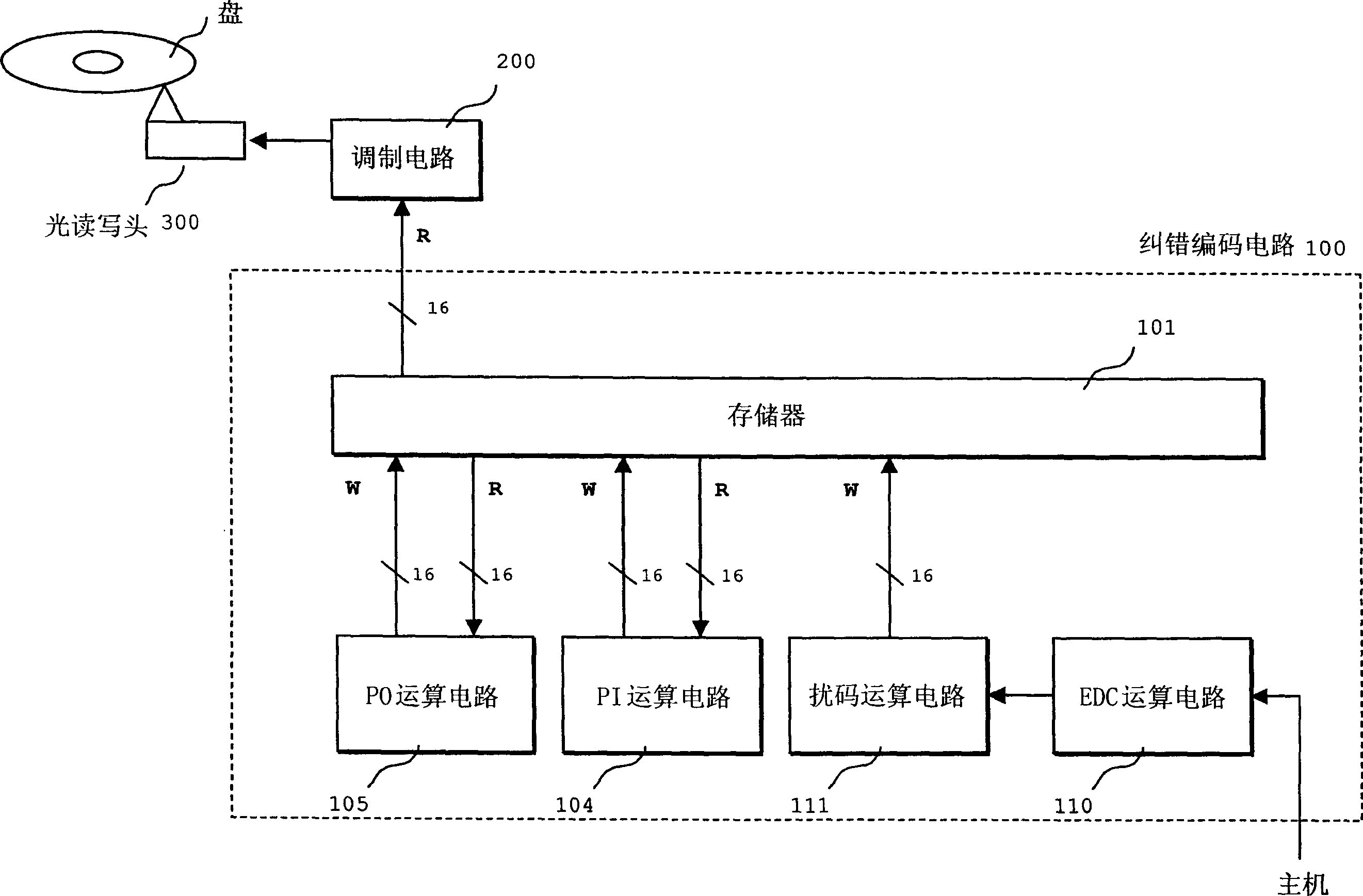

[0056] figure 1 It is an installation diagram of the disc recorder of the first embodiment. which with Figure 7 Similar parts are denoted by the same reference numerals.

[0057] The memory 101 includes SDRAM or the like. The PI operation circuit 104 calculates an error correction code in the PI direction (row direction), and adds it to the scrambled data. The PO operation circuit 105 calculates an error correction code in the PO direction (column direction), and adds it to the scrambled data. The EDC operation unit 110 calculates an error detection code and adds the error correction code to the data. The scramble operation circuit 111 scrambles the data to which the error detection code has been added. The modulation circuit 200 performs predetermined modulation on input data to generate a recording signal. An optical head 300 uses a laser beam corresponding to a recording signal input from the modulation circuit 200 to write data into the optical disc.

[0058] Acco...

Embodiment 2

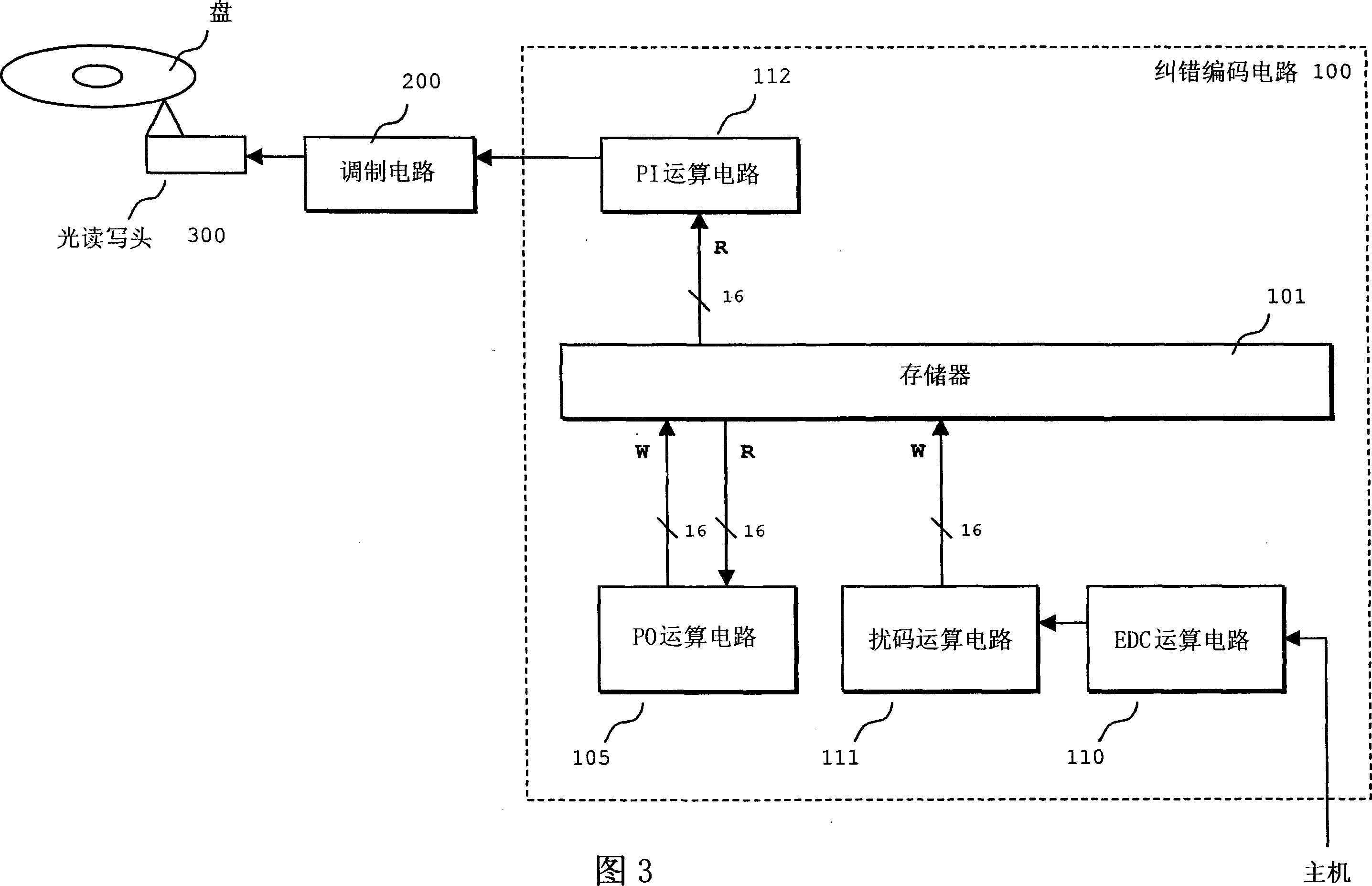

[0065] By replacing the PI operation circuit 104 with a PI operation circuit 112 as described below, it is possible to further reduce the number of accesses to the memory 101 .

[0066] Figure 3 is a diagram of a setup for this situation. In this setting example, the procedure of PI and PO encoding and the operation of accessing the memory 101 are different from Embodiment 1. In other words, in this setting example, the processing of the PO operation circuit 105 is performed first, and then the PI operation circuit 112 adds the PI code of the line data, after which the data is directly output to the modulation circuit 200 .

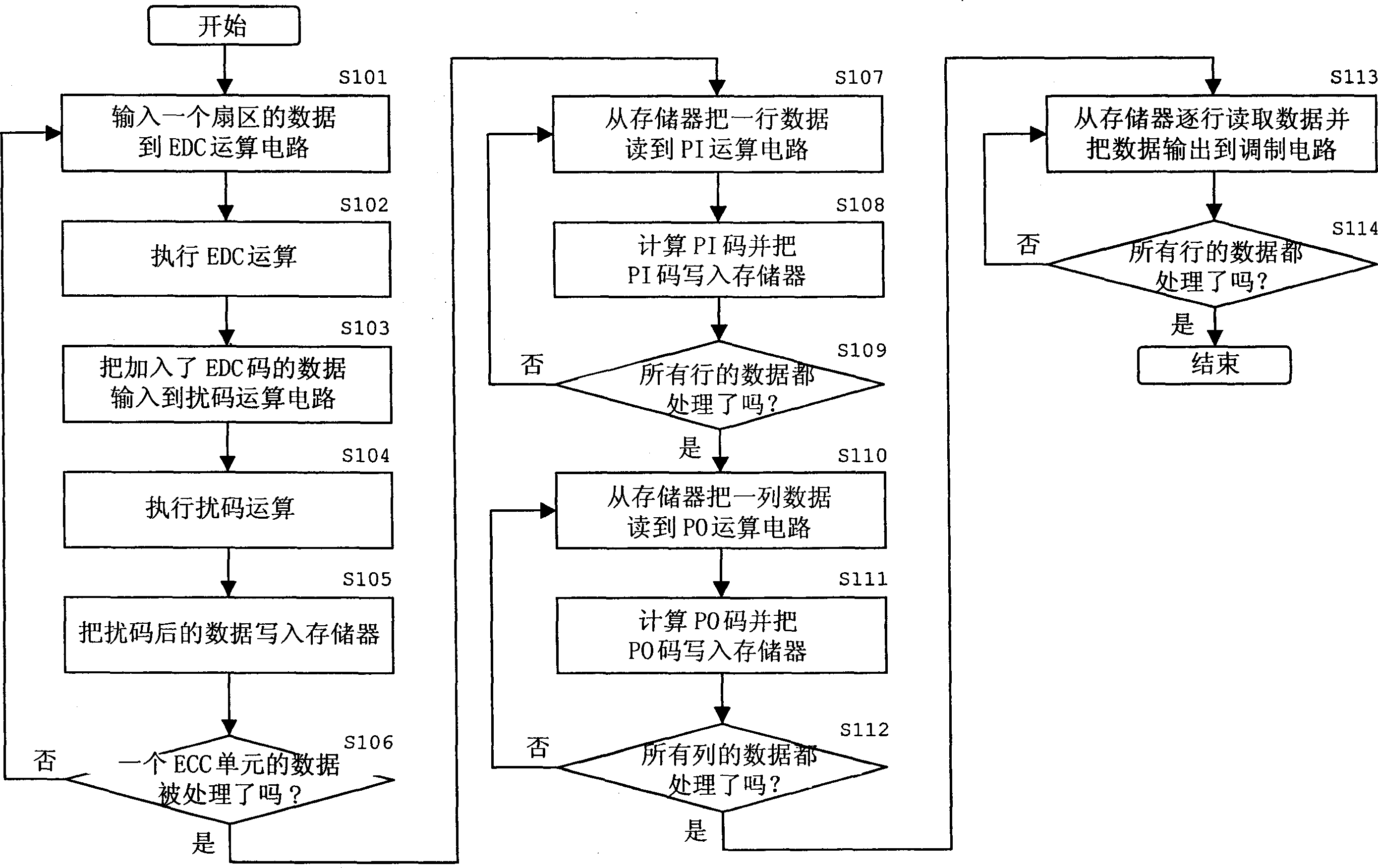

[0067] Figure 4 A flowchart showing the data error correction encoding process for one ECC unit. Steps S101 to S106 are the same as in Embodiment 1.

[0068] In the process of steps S101 to S106, after the data of an ECC unit is written into the memory 101, the data of a column is first read from the memory 101 to the PO operation circuit 105 (S120), ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More