Method for implementing five-level tolerant flowing structure in integer unit of microprocessor

A pipeline structure and microprocessor technology, applied in the computer field, to achieve the effects of improving execution efficiency, improving error correction efficiency, and good fault tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

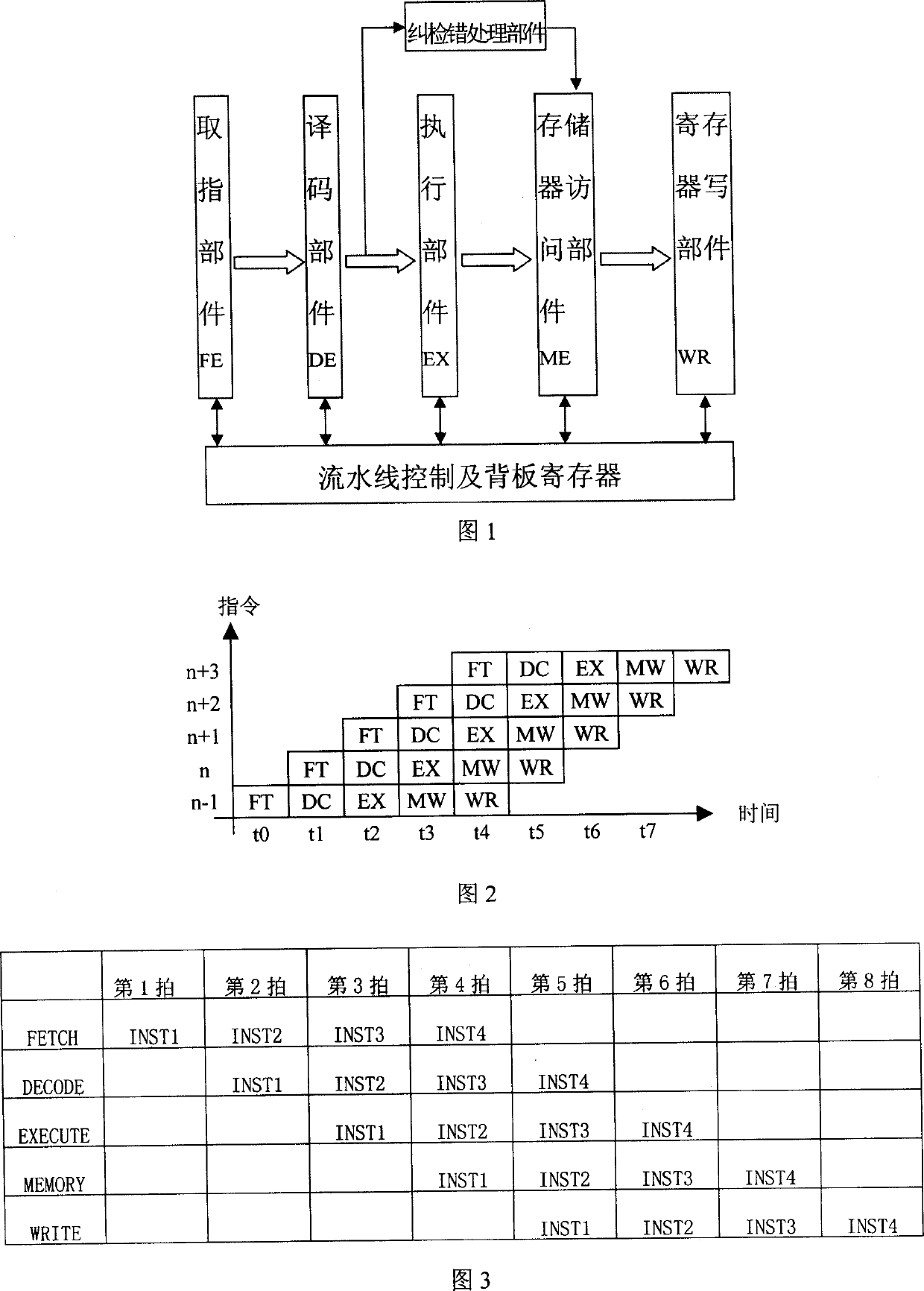

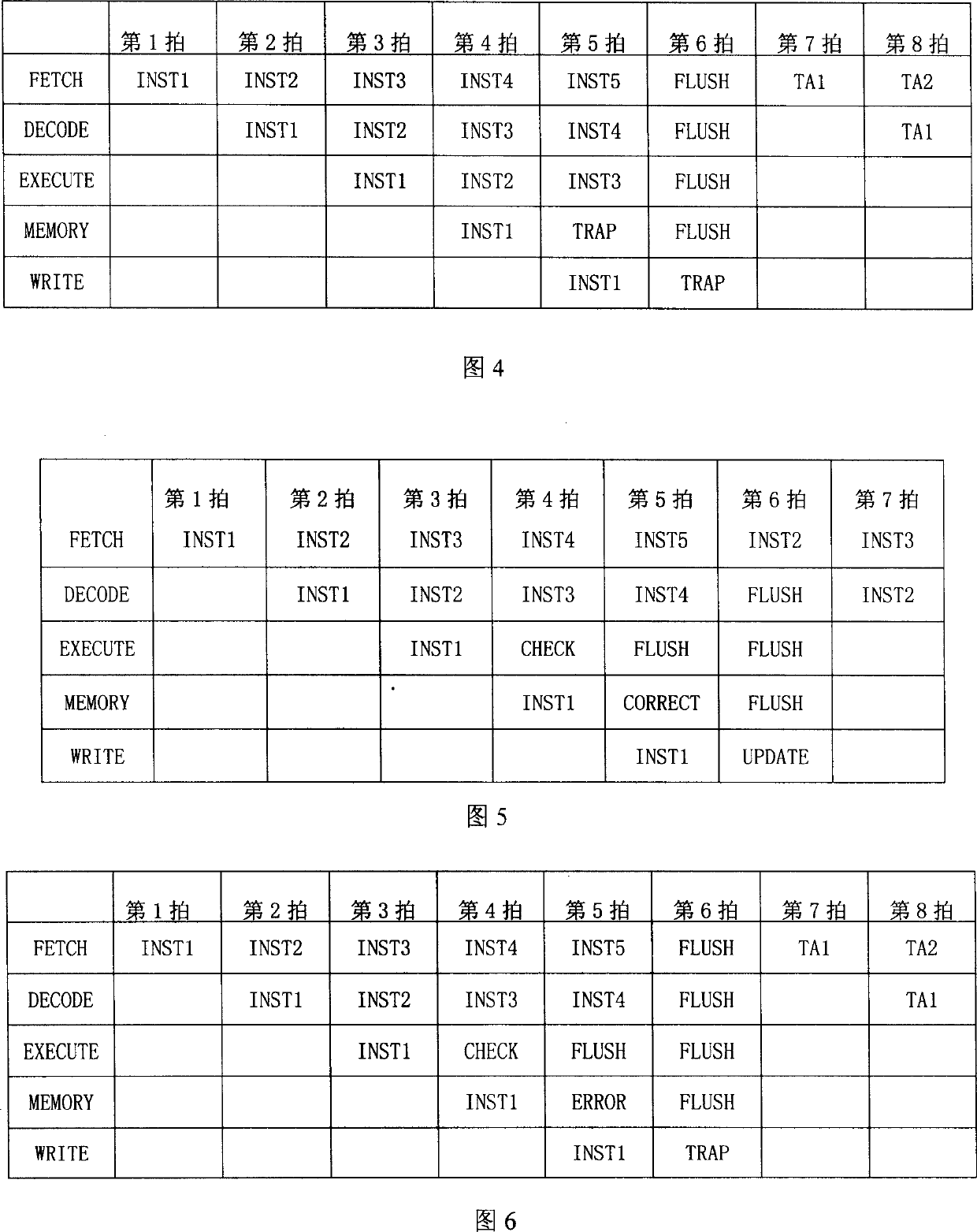

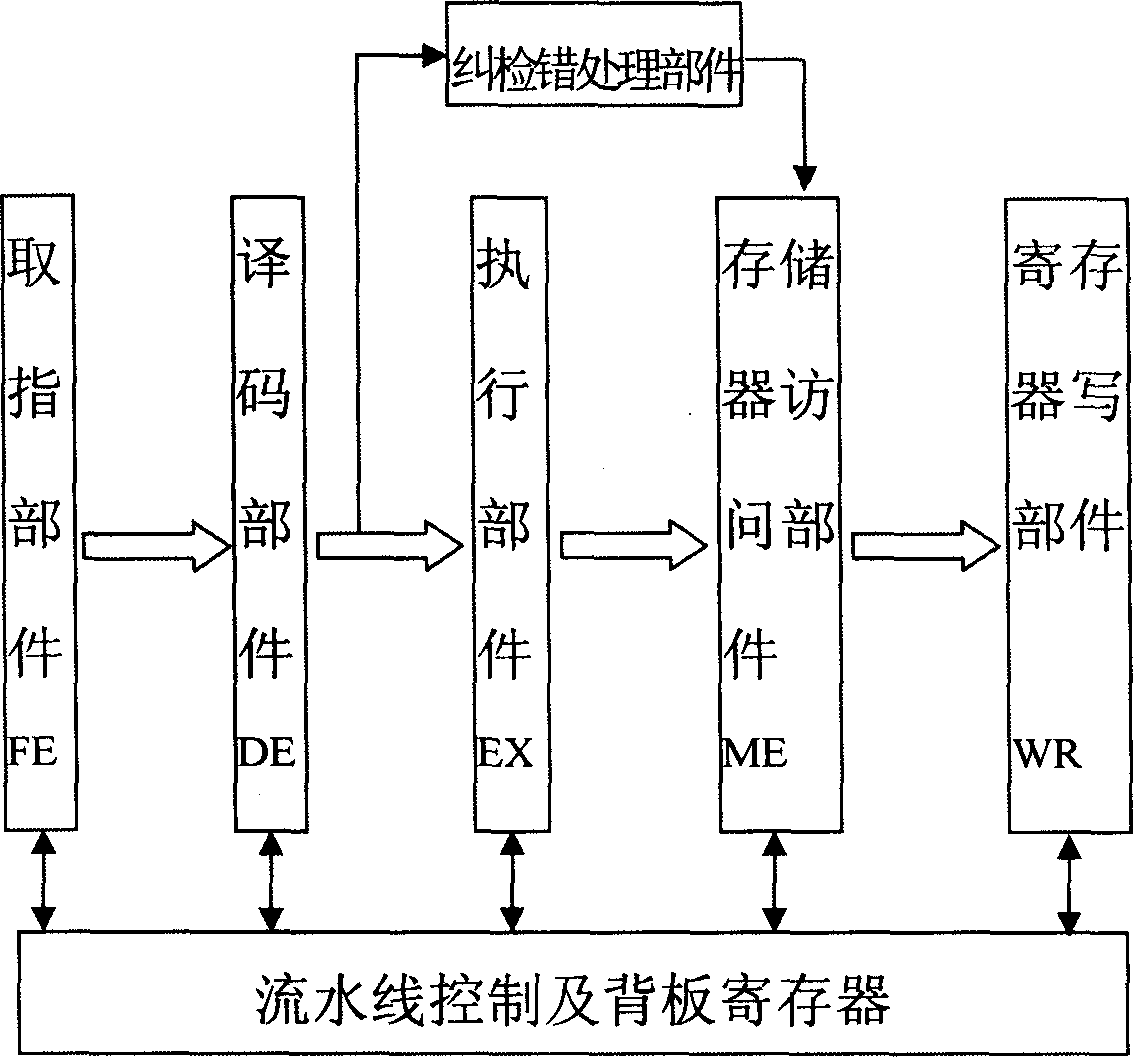

[0032] In the SPARC V8 compatible microprocessor LSFT32, a five-level fault-tolerant pipeline structure is used to process instructions. The hardware circuit structure of its control logic is shown in Figure 1. The pipeline structure consists of fetching components, decoding components, execution components, storage The access unit and the register writing unit are composed, and all the units of the above-mentioned pipeline structure are connected in sequence, and are connected with the first-line control and the backplane register; the output of the decoding unit and the storage access unit are also connected with an error correction processing unit, It is used to complete the error detection and correction of the source operand, and to establish corresponding control information. Each instruction is completed through five levels of processing under the control of the pipeline control and the backplane register; when the data in the register is correct, each The beat completes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com