Realization of rapid coding-decoding circuit with run-length

A run-length, codec technology, applied in the field of fast run-length codec circuit implementation, can solve the problems of increasing pipeline delay and large circuit implementation scale, and achieves the effects of reducing power consumption, reducing implementation scale, and reducing pipeline delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

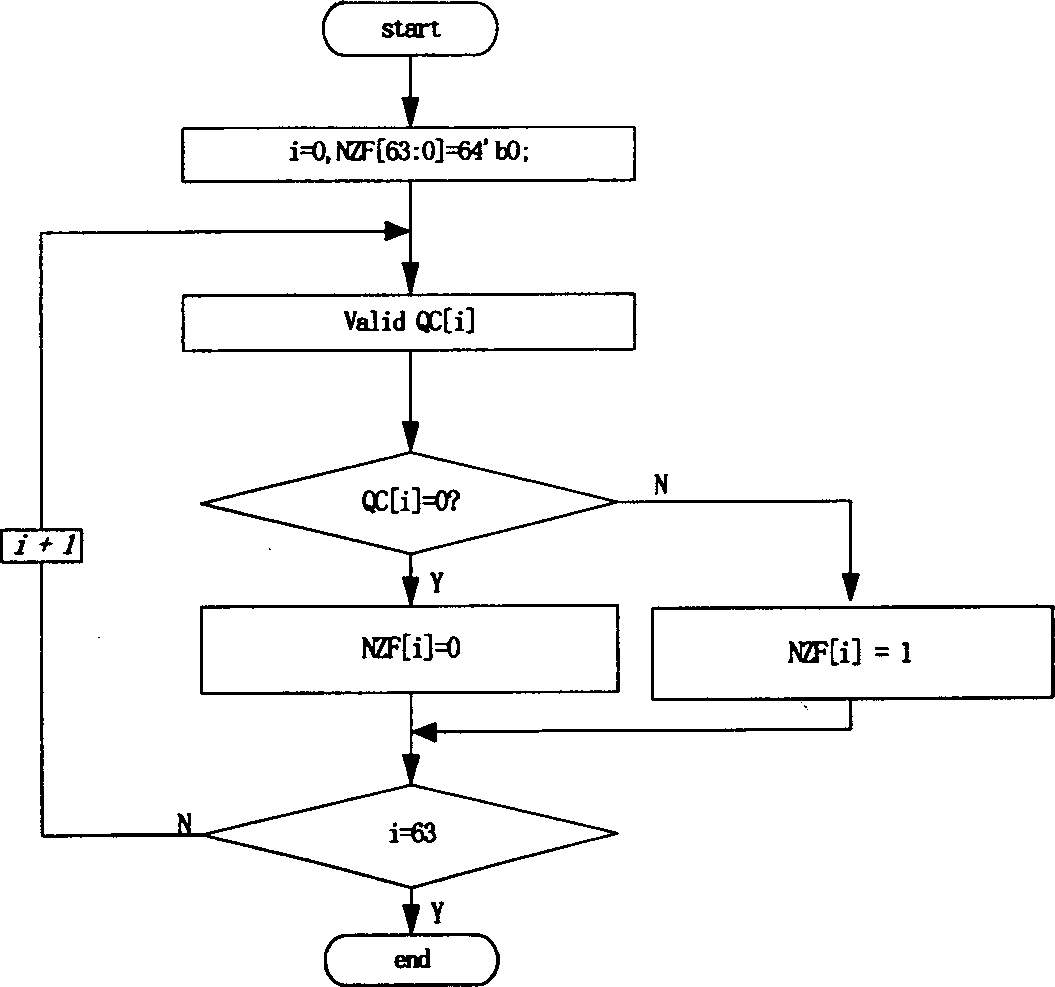

[0024] figure 1 It is a flow chart of setting the 64-bit non-zero flag bit register vector during 8×8 block processing (Block Processing). Before the quantization of the current block starts, the initial value of NZF[63:0] is 0. After the quantization starts, once the hardware circuit detects that the current quantization coefficient QC[i] is not zero, it will set the corresponding non-zero flag register position to 1, and when the quantizer outputs the last quantization coefficient NZF[63] of the current block, at the same time, the current A non-zero marker for a block completes.

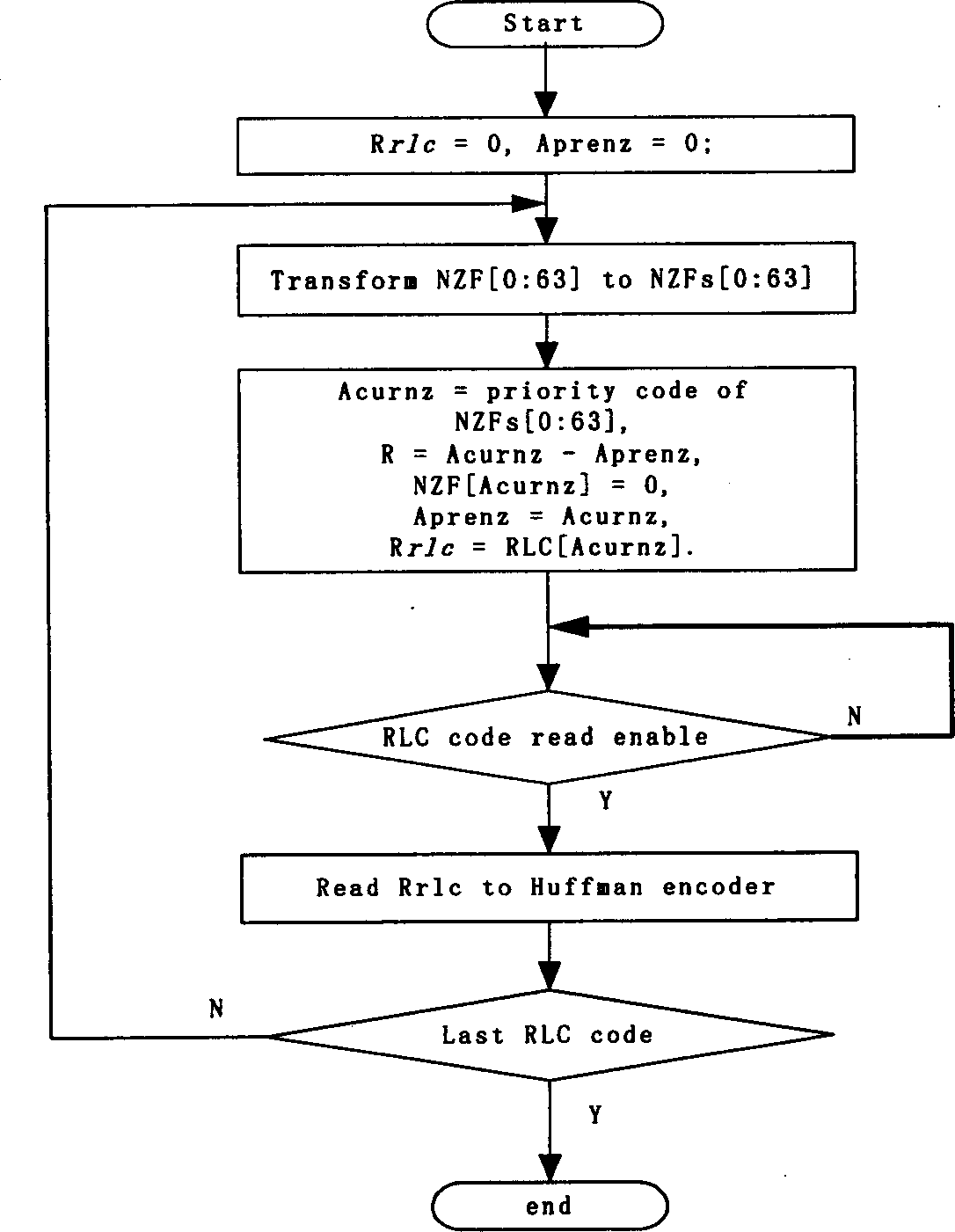

[0025] figure 2 It is a real-time RLC encoding flow chart of run-length encoding during 8×8 block processing (Block Processing). When the actual circuit works, the RLC encoding of a non-zero coefficient is completed in two clock cycles. The first cycle is the prefetch coding cycle, and the second cycle is the RLC code readout cycle, but it is also the prefetch code cycle of the next non-zero ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More