Method and apparatus for improved MOS gating to reduce miller capacitance and switching losses

A switch and electrode technology, applied in the field of metal oxide semiconductor field effect transistors, can solve the problem of reducing the channel width and achieve the effect of less switching time and switching loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

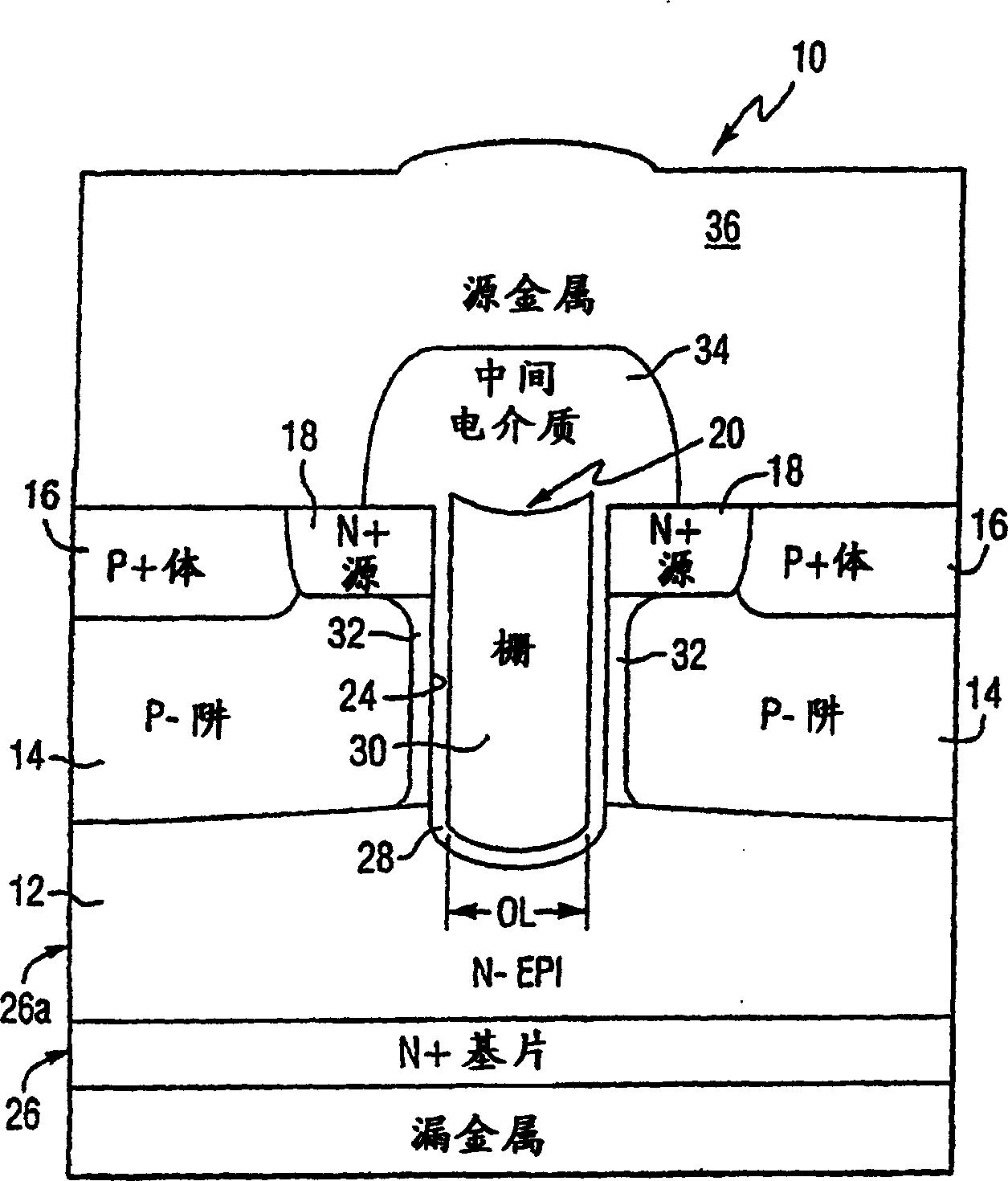

[0025] Referring now to the accompanying drawings in particular figure 1 , which shows a schematic cross-sectional view of a prior art trench-gated MOSFET device. MOSFET device 10 includes drain region 12 , well region 14 , body region 16 , source region 18 , gate region 20 and channel 24 , all of which are formed on substrate 26 .

[0026] More specifically, the N+ type substrate 26 includes an upper layer 26a in which the N- drain region 12 is formed. The P-type well region 14 is located above the drain region 12 . A heavily doped P+ body region 16 is defined within an upper surface (not indicated) of upper layer 26 a and a portion of well region 14 . A heavily doped N+ source region 18 is formed on the upper surface of upper layer 26 a and within a portion of well region 14 and adjacent to channel 24 . The sidewalls and bottom (not shown) of trench 24 are lined with a dielectric material 28, such as oxide. Gate region 20 is formed of conductive material 30, such as dope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More