Access buffer storaging method

A cache and buffer technology, which is applied in the direction of synchronous signal speed/phase control, etc., can solve the problems of reducing the complexity of the logic circuit design of the first-in-first-out buffer, the uncertainty of the delay error of the first-in-first-out buffer, etc., and achieve the reduction of delay changes range, effect of guaranteed constancy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

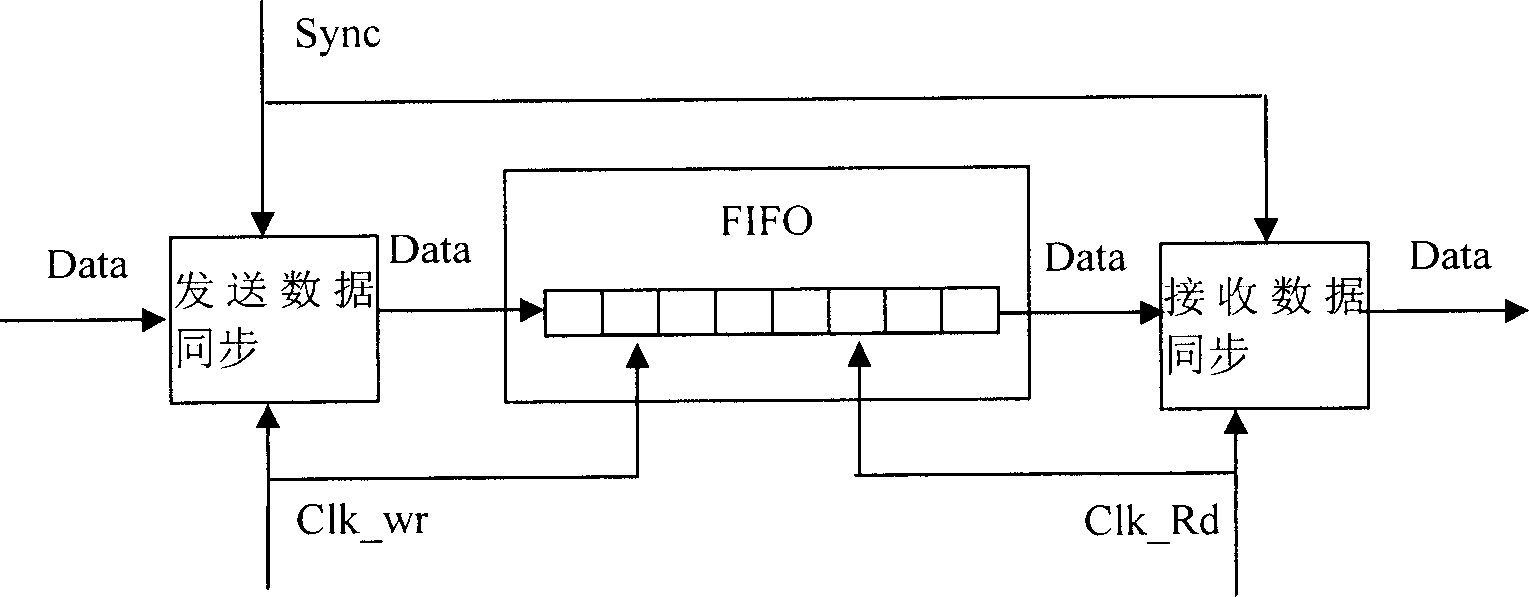

[0032] The present invention will be described in further detail below in conjunction with the accompanying drawings.

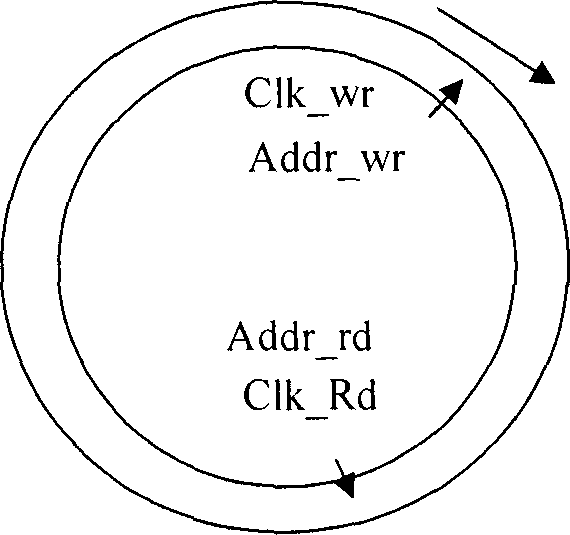

[0033] The technical solution of the present invention is based on the premise that both the read clock and the write clock are locked on the same clock source, and the frequencies of the sending and receiving clocks are the same, but there is a certain range of phase jitter.

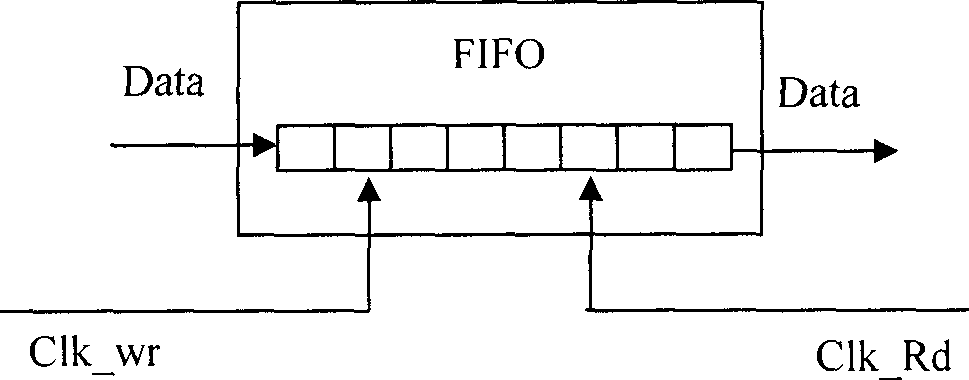

[0034] Such as Figure 4As shown, the present invention at first arranges n cache units on the FIFO buffer, n=[x]+2, wherein [x] represents that the relative jitter range of the read-write clock is rounded up, and the relative jitter range of the read-write clock is equal to or greater than The multiple of the clock cycle is the unit; set the write clock flag signal and the read clock flag signal respectively, the cycle of the write clock flag signal is n times the write clock cycle, and the cycle of the read clock flag signal is n times the read clock cycle; All cache units are writt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More