Method and system for inspecting semiconductor defect

A technology for semiconductor and defect testing, applied in the field of defect detection, which can solve problems such as inability to clearly know location information and reduced production capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the above and other objects, features and advantages of the present invention more comprehensible, preferred embodiments are listed below and described in detail with accompanying drawings.

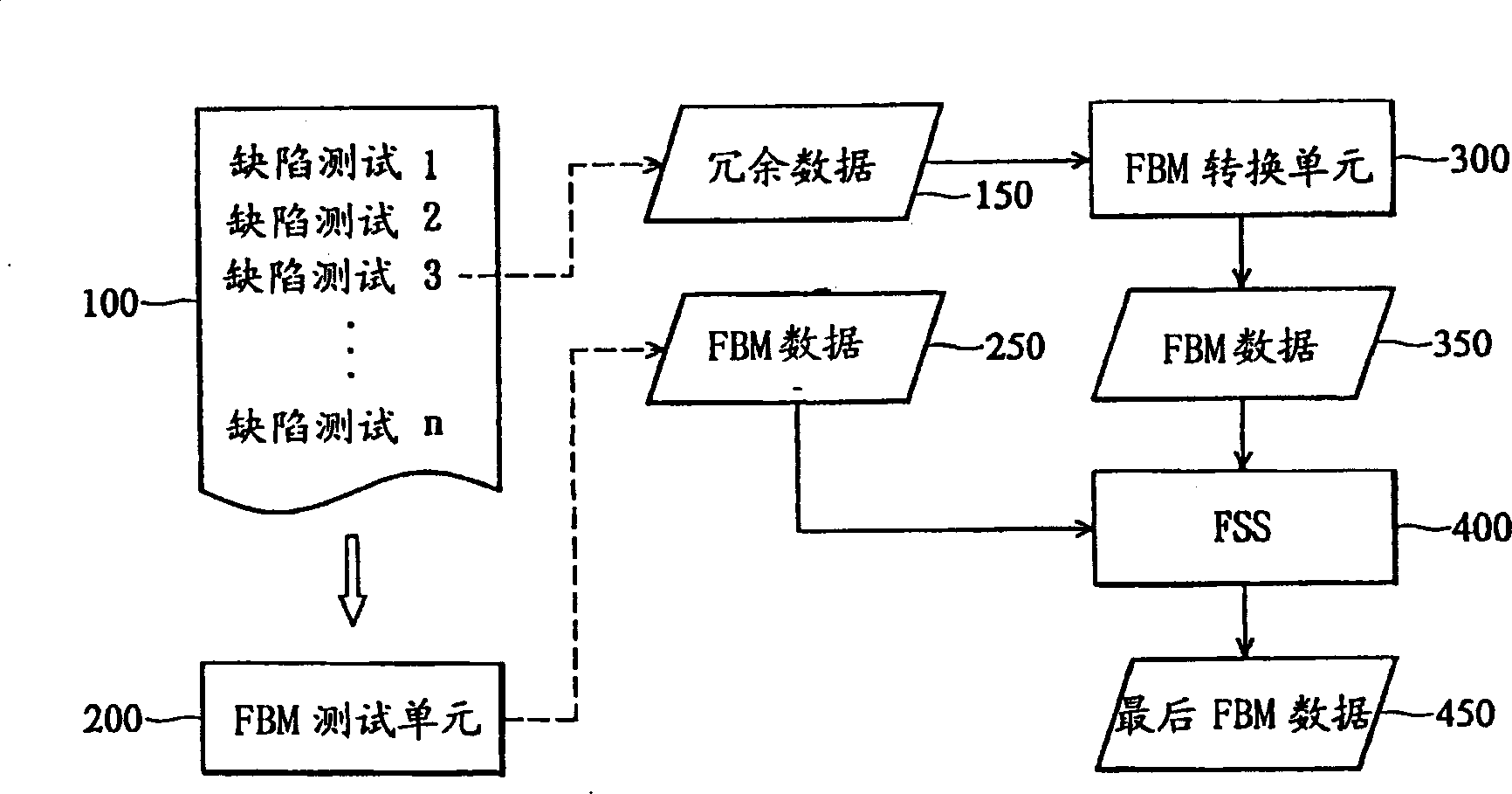

[0025] The embodiment of the present invention discloses a defect detection method and system using bad bitmap (FBM).

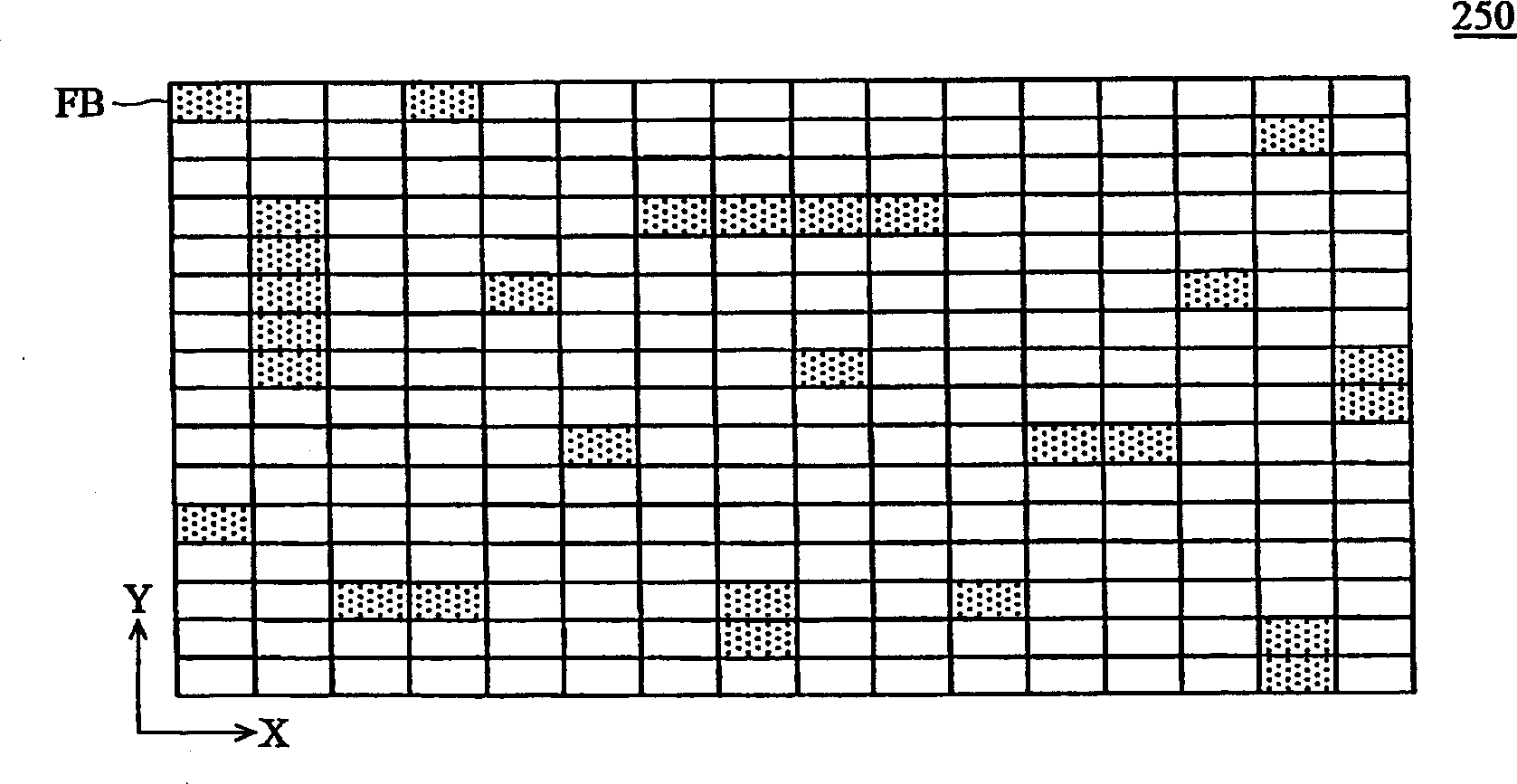

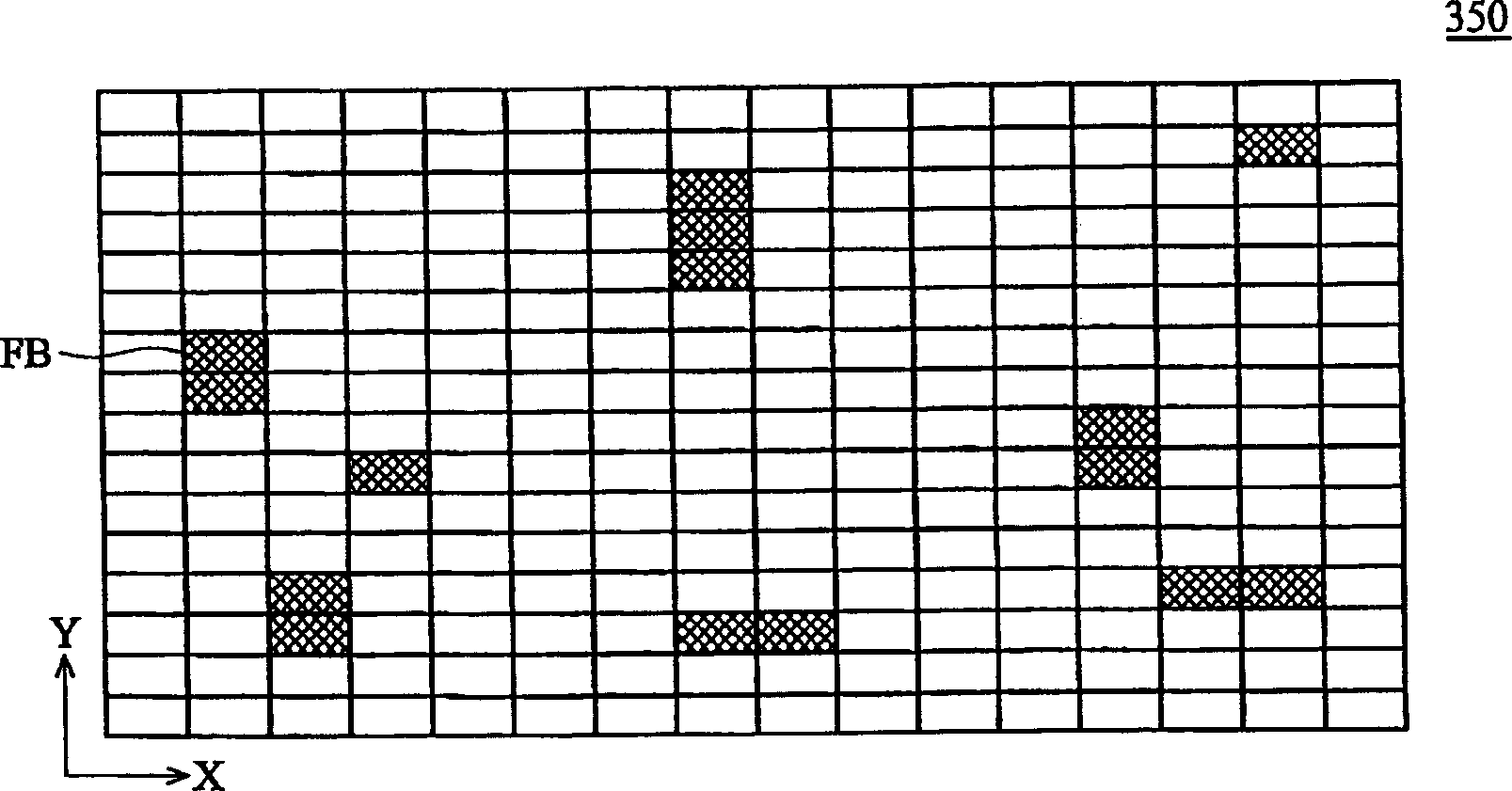

[0026] When performing the FBM test, it records all the bad bits of the chip and forms a bad bit map in the form of a matrix. As mentioned above, performing two FBM tests can find out the position information of the defective bits corresponding to the defect tests performed between the two FBM tests. The position information of the bad bits generated by the test is identified and analyzed, and the chip cannot be selected arbitrarily. Based on this point, the embodiment of the present invention stores redundancy information (ie, defect information) generated during each defect test, and then converts the redundancy information into data compatible...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com