Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses

A multi-layer structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, waveguides, etc., can solve the problems of electrical performance deterioration and harmfulness of multi-layer structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

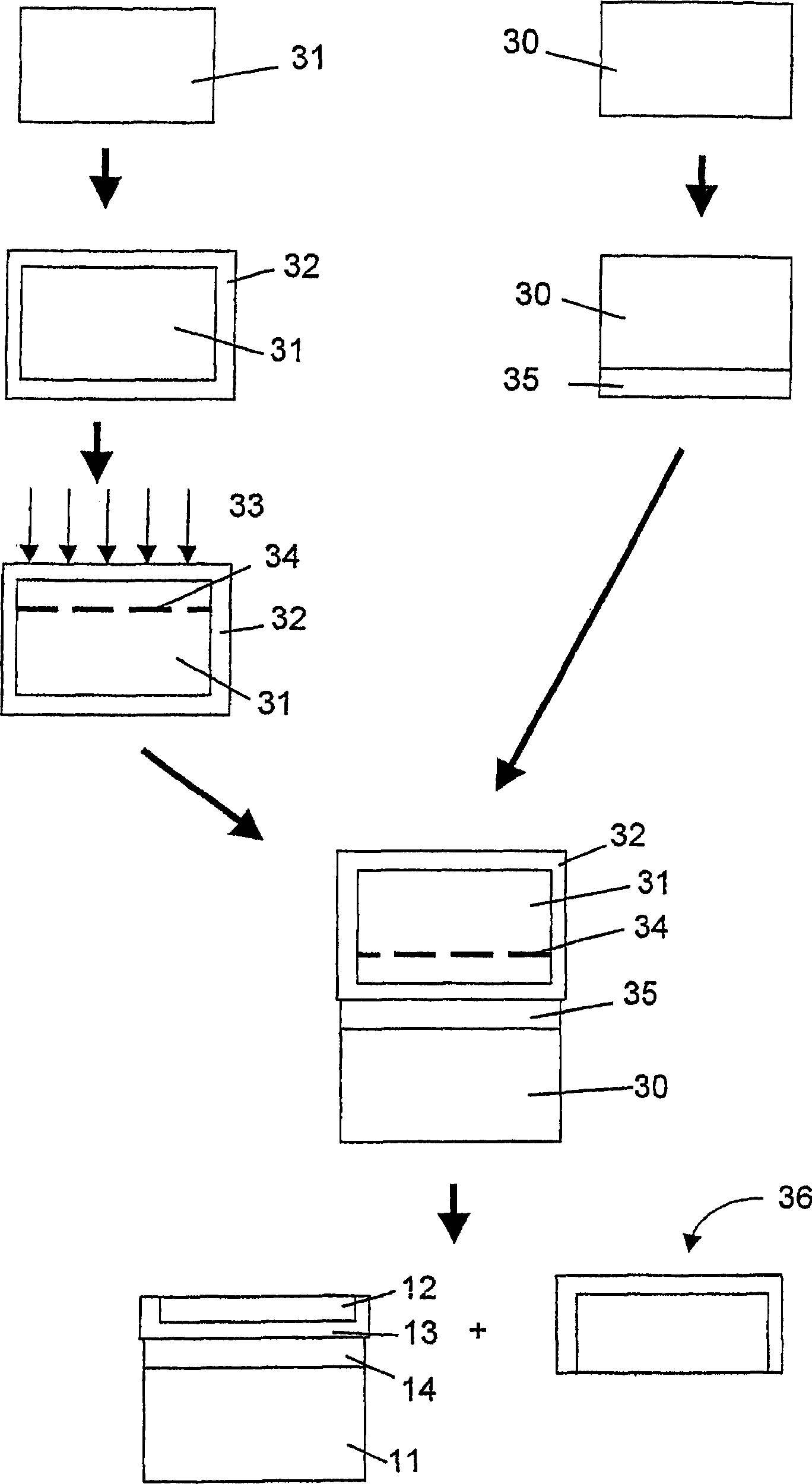

[0070] - Preparation of structures.

[0071] - Selective etching of the active layer 12 of the structure, which in the case of SOI may stop at the insulating layer 13 of buried oxide.

[0072] - Deposition of the entire conductive metal layer on the structure on top of the buried oxide.

[0073] - Selective dry etching of deposited metal to form detection patterns, in this case conductive parallel metal lines forming a coplanar waveguide (CPW), between which there is a central metal line.

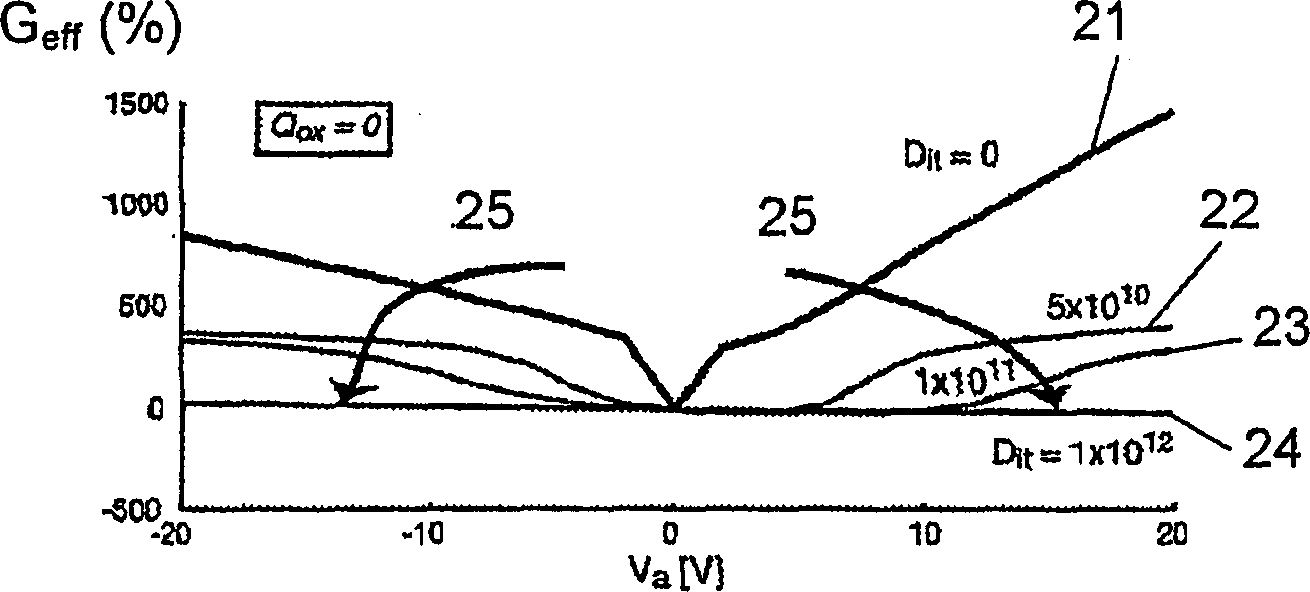

[0074] - Application of an electrical signal on the central wire. The signal consists of a superposition of low-amplitude continuous and alternating voltages. This combined voltage is applied to the wires and the following parameters can be determined:

[0075] - Amplitude V of the continuous component A ,

[0076] - frequency f of the alternating component.

[0077] The superimposition of continuous and alternating voltage components during the measurement shows that the low-conducti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More