Circuit struction of reverse order / circulation address generater

A circuit structure and generator technology, applied in the field of computer architecture, can solve problems affecting system operation speed, large system power consumption, etc., achieve the effect of reducing AT2 and improving execution efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

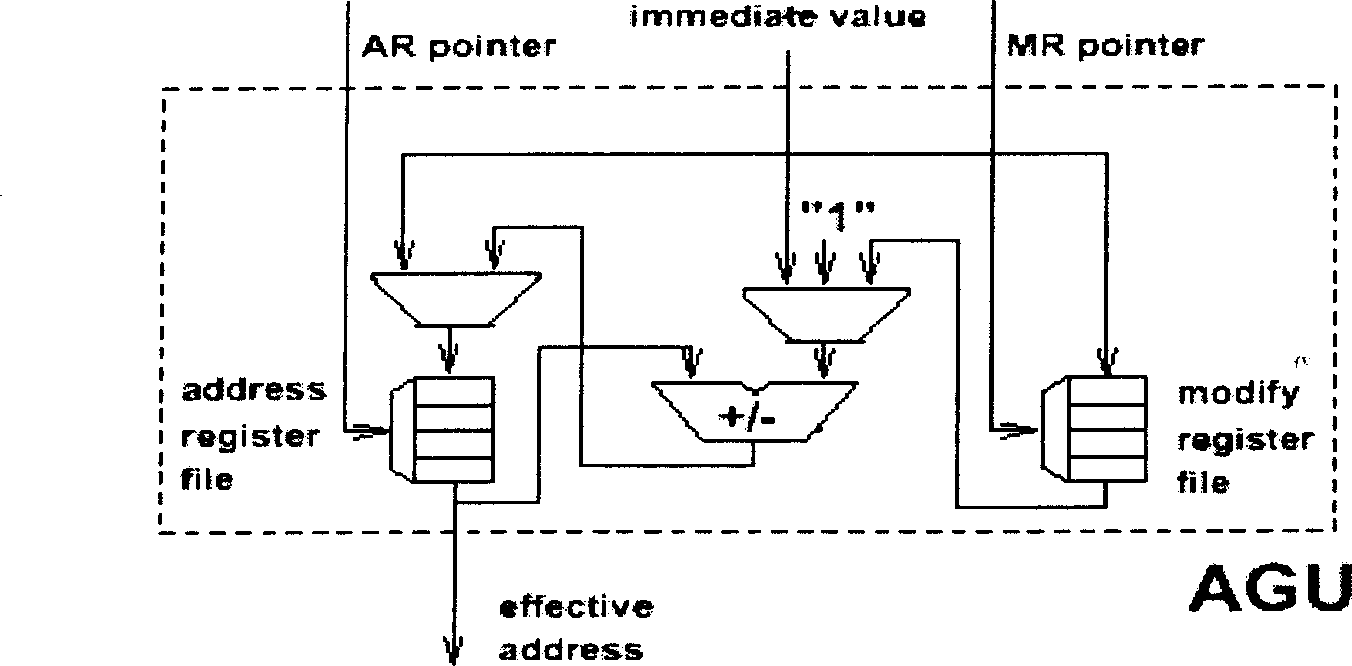

[0056] SMDSP high-performance digital signal processor, 24-bit address line, which supports sequential, reverse and circular addressing. The address generator within the SMDSP uses a Figure 4 The circuit structure of the reverse / circular address generator, including:

[0057] A five-terminal input selector. The five-terminal input selector determines the data of the five-input strobe according to the addressing type control signal type. The 5 data to be strobed are from top to bottom: "step" (when type indicates circular addressing, select it); "immediaat_value" (when type indicates immediate addressing, select it); "MR" (when type indicates base address indexing addressing, select it); "1" (when type indicates sequential addressing, select it); "L / 2" (when type indicates reverse order When addressing, strobe it). The output of the five-input selector is connected to one input of the adder and the inverse adder.

[0058] an adder. Except for the reverse addressing mode,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More