Clock generation circuit, and communication device

A clock generation circuit and additional circuit technology, applied in the direction of generating/distributing signals, electrical components, pulse position modulation, etc., can solve the problems of wireless communication influence, misoperation of surrounding circuit electronic equipment, etc., and achieve the effect of reducing useless radiation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

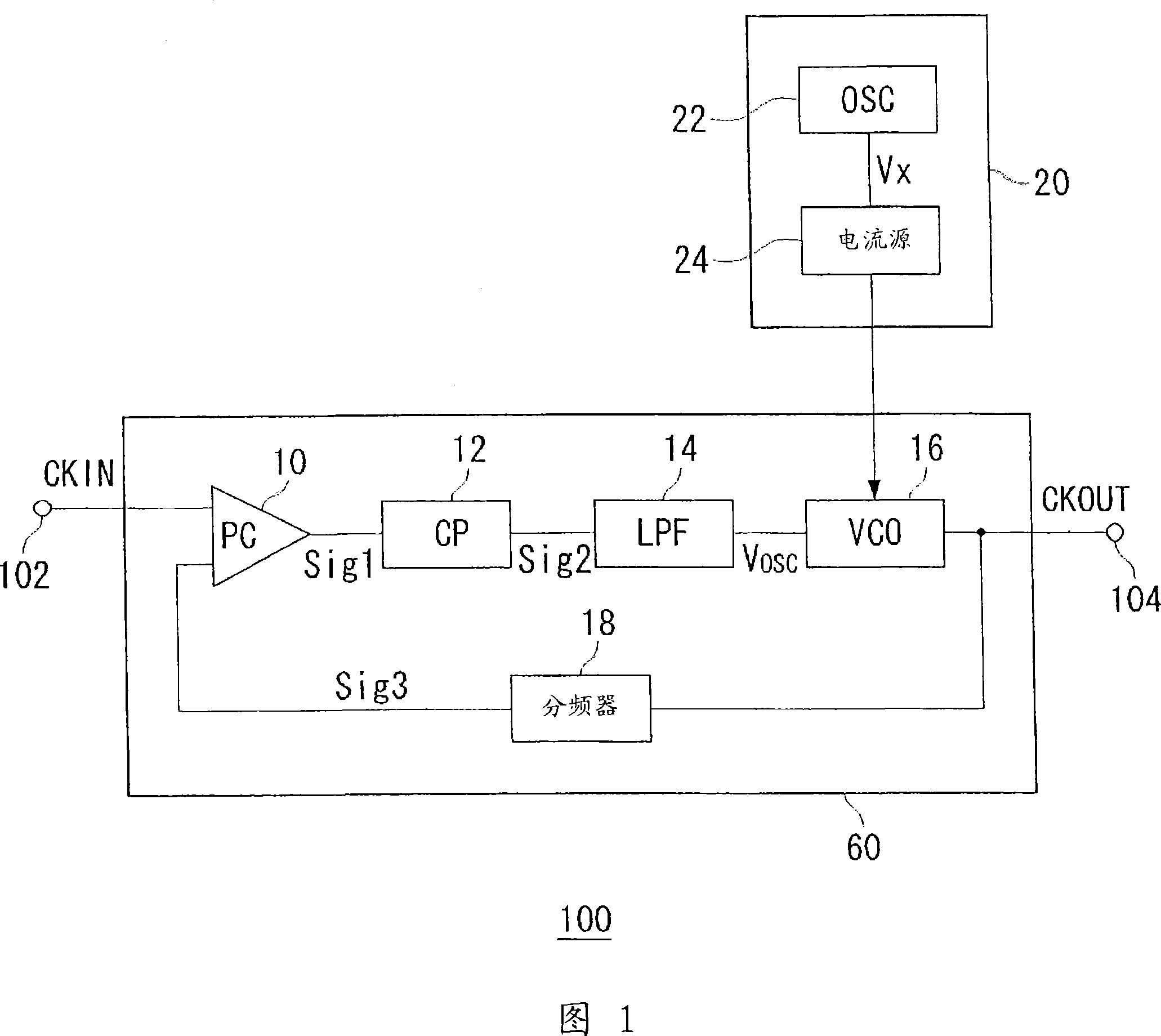

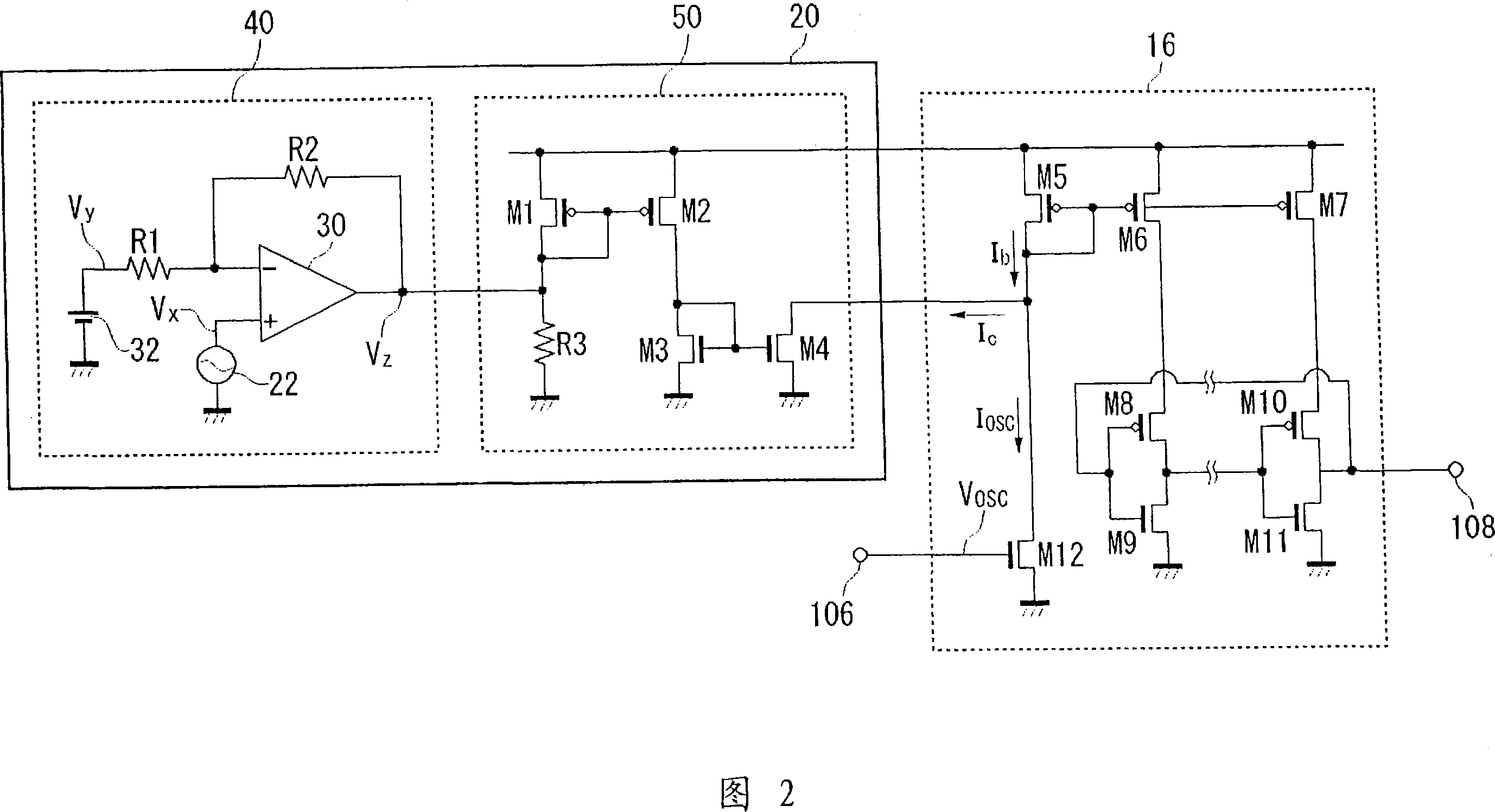

[0048] FIG. 1 shows the configuration of a clock generating circuit 100 in the first embodiment of the present invention.

[0049] The clock generation circuit 100 includes an input terminal 102 and an output terminal 104 . The signals input or output to the respective terminals are respectively referred to as an input clock signal CKIN and an output clock signal CKOUT. The frequencies of the input clock signal CKIN and the output clock signal CKOUT are referred to as input clock frequency fIN and output clock frequency fOUT, respectively.

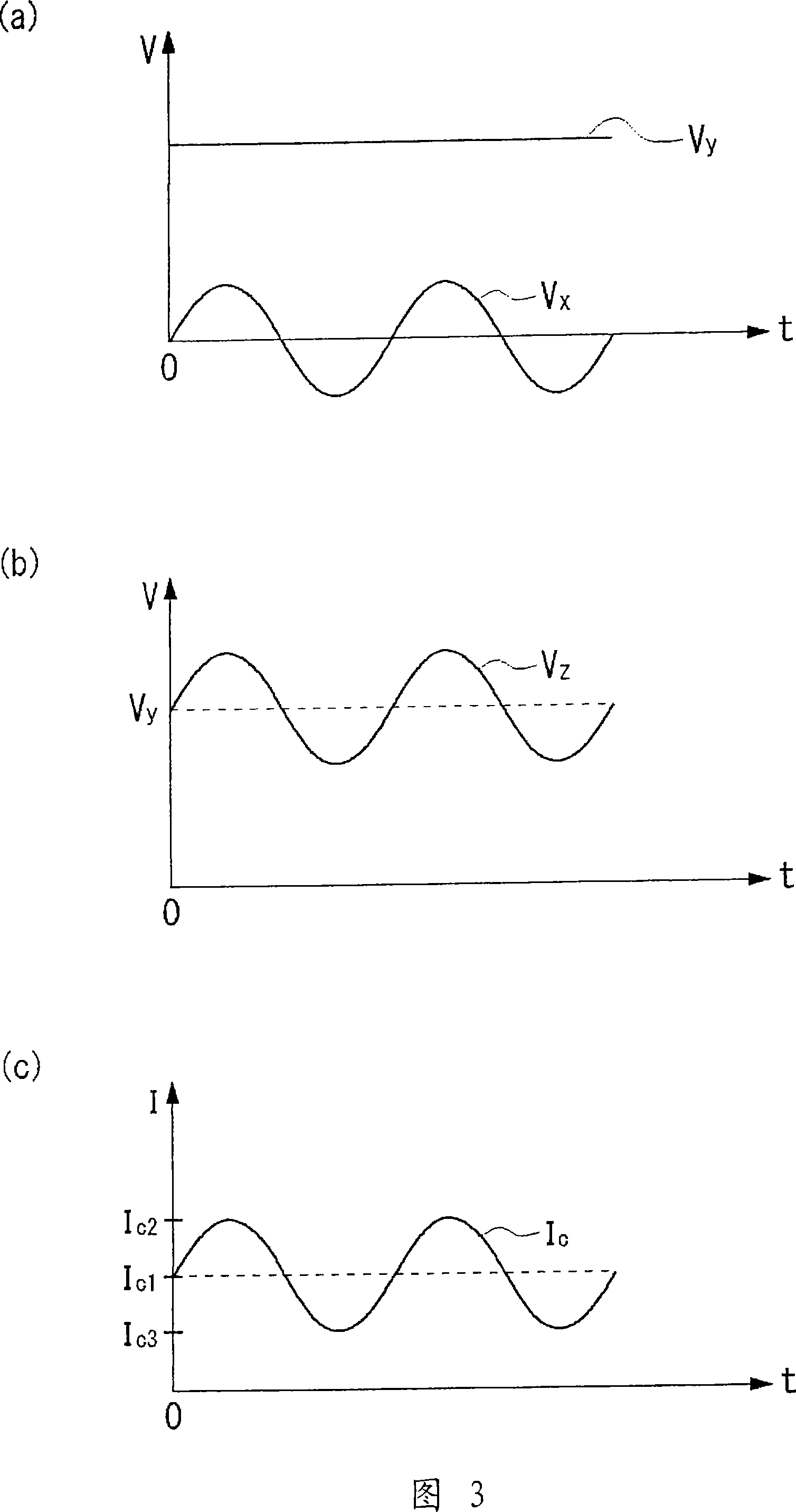

[0050] This clock generating circuit 100 includes a PLL circuit 60 and a jitter adding circuit 20 .

[0051] The PLL circuit 60 includes a phase comparator 10 , a charge pump circuit 12 , a low-pass filter 14 , a voltage controlled oscillator 16 , and a frequency divider 18 . The clock generation circuit 100 multiplies the input clock signal CKIN by the frequency division ratio N set by the frequency divider 18 and outputs the clock sign...

no. 2 Embodiment approach

[0082] FIG. 6 is a block diagram showing the configuration of a clock generation circuit 100 according to the second embodiment of the present invention. In FIG. 6 , constituent elements that are the same as or equivalent to those already shown are assigned the same reference numerals, and appropriate descriptions thereof are omitted.

[0083] In the clock generating circuit 100 of the first embodiment, spectrum spreading is performed by varying the bias current of the voltage controlled oscillator 16, but in the clock generating circuit 100 related to the second embodiment shown in FIG. 6 , by Spectrum spreading is performed by adding dither to the oscillation control signal Vosc input to the voltage controlled oscillator 16 .

[0084] The clock generating circuit 100 of the present embodiment includes a jitter adding circuit 20 in the subsequent stage of the low-pass filter 14 . The dither adding circuit 20 includes an adder 70 and an oscillator 72 . The oscillator 72 outp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More