Time-delay locking loop

A technology of delay locked loop and locked loop, applied in the direction of electrical components, automatic power control, etc., can solve the problems affecting the response characteristics and indicators of the system, and achieve the effect of improving the fast response characteristics, suppressing the impact, and shortening the response time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

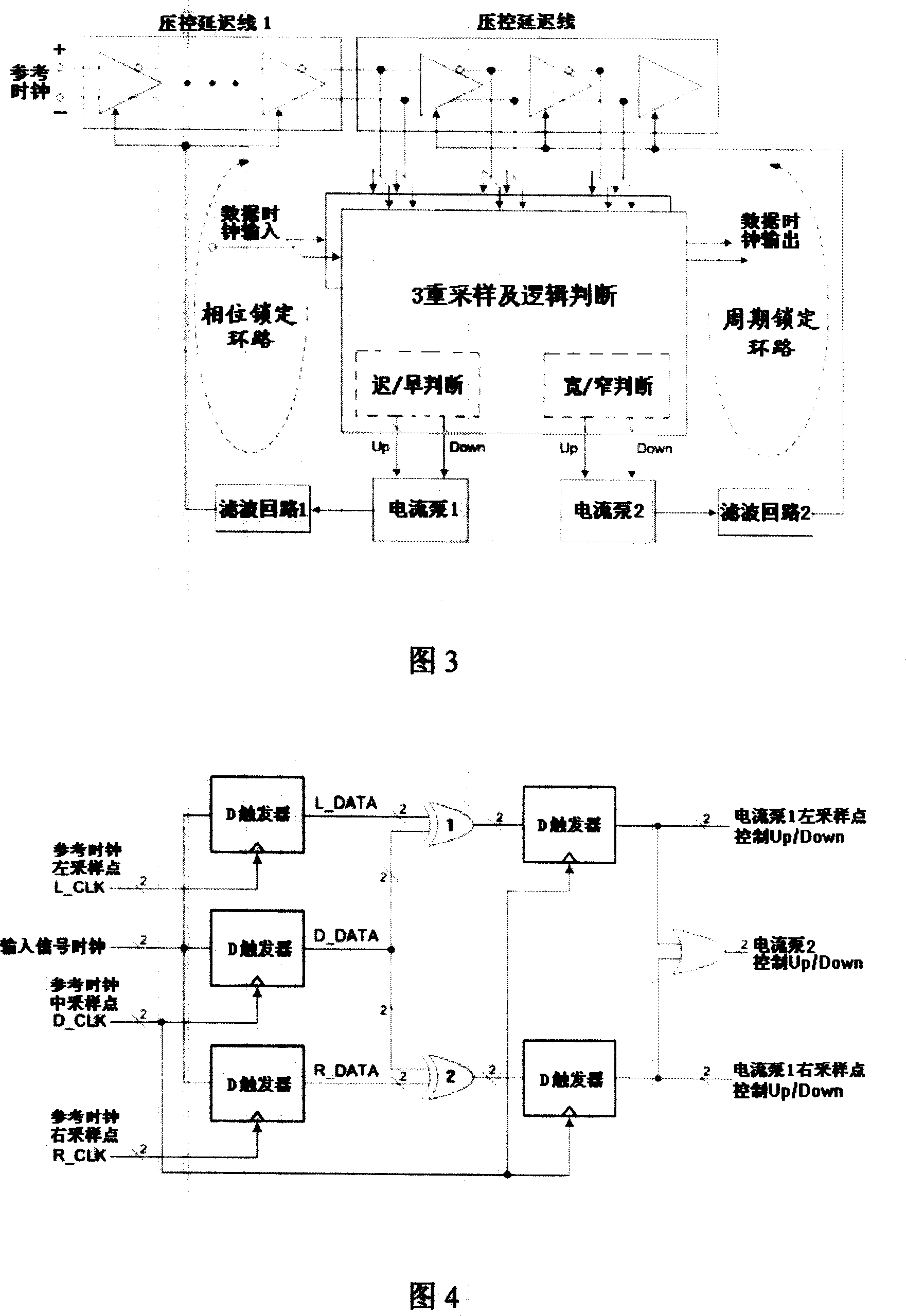

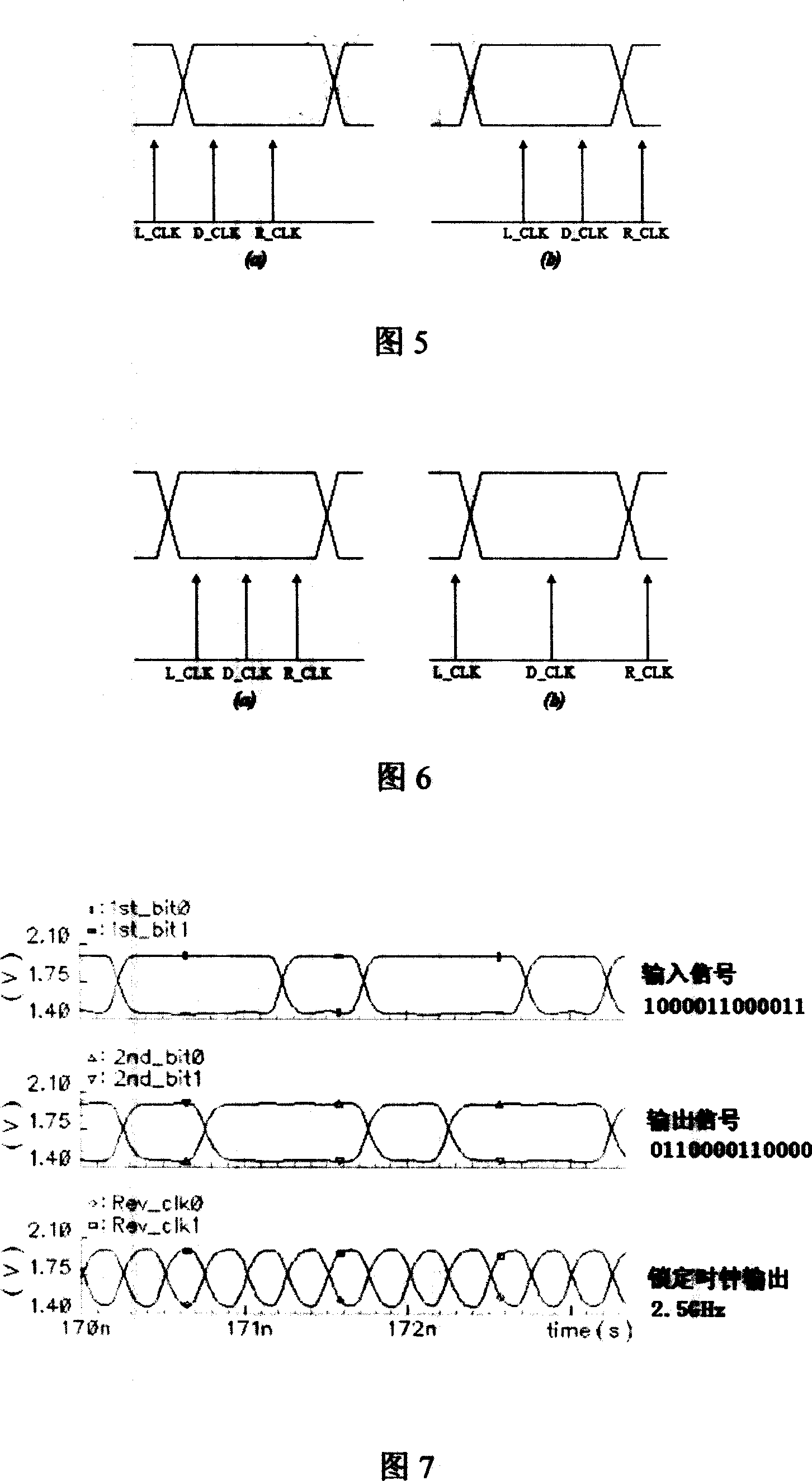

[0018] The technical solution adopted in the present invention is a fully differential double-loop delay-locked loop structure, through triple signal sampling and logic judgment circuits, voltage control delay lines (Voltage Controlled Delay Lines) and differential current pump (Differential Charge Pump) Guarantees signal integrity.

[0019] The specific method is to insert an independent double-loop (signal phase-locked loop and signal period-locked loop) sampling loop structure in the signal path, and use the triple signal sampling method to separately perform signal phase (sooner or later logic judgment) on the clock / data signal Sampling / detection and signal period (narrow-width logic judgment) sampling / detection, if there is a deviation in the judgment, the phase and spacing between the 3 re-sampling points are changed through the voltage control delay line, and the signal phase and period are re-sampled separately until Finally lock the signal phase and period.

[0020] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More