Patents

Literature

47 results about "Ternary signal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In telecommunication, a ternary signal is a signal that can assume, at any given instant, one of three states or significant conditions, such as power level, phase position, pulse duration, or frequency.

Optical transmitter system and method

InactiveUS6337756B1Compensation for dispersionDegrades receiver sensitivityTransmission monitoringElectromagnetic transmittersEngineeringOptical transmitter

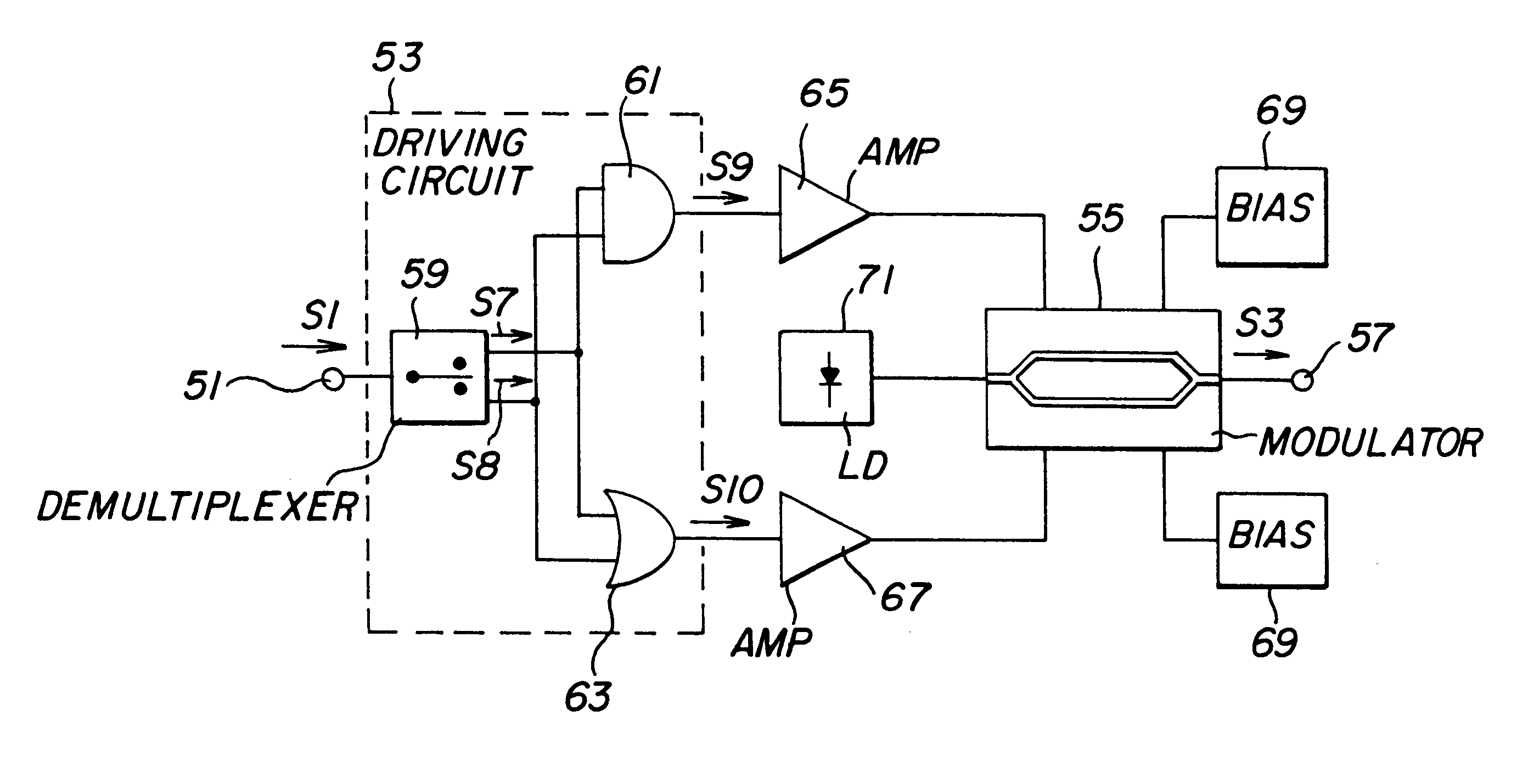

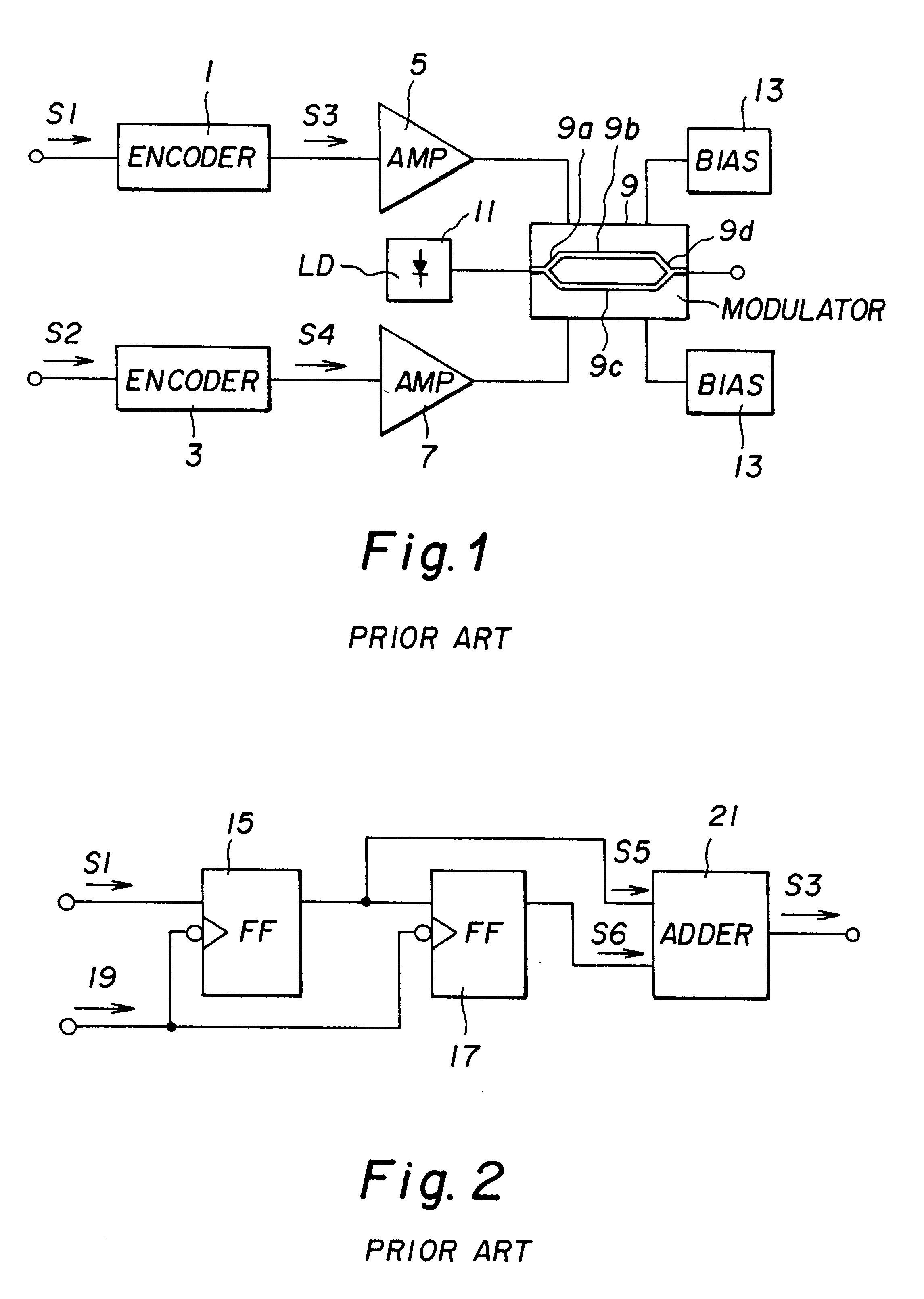

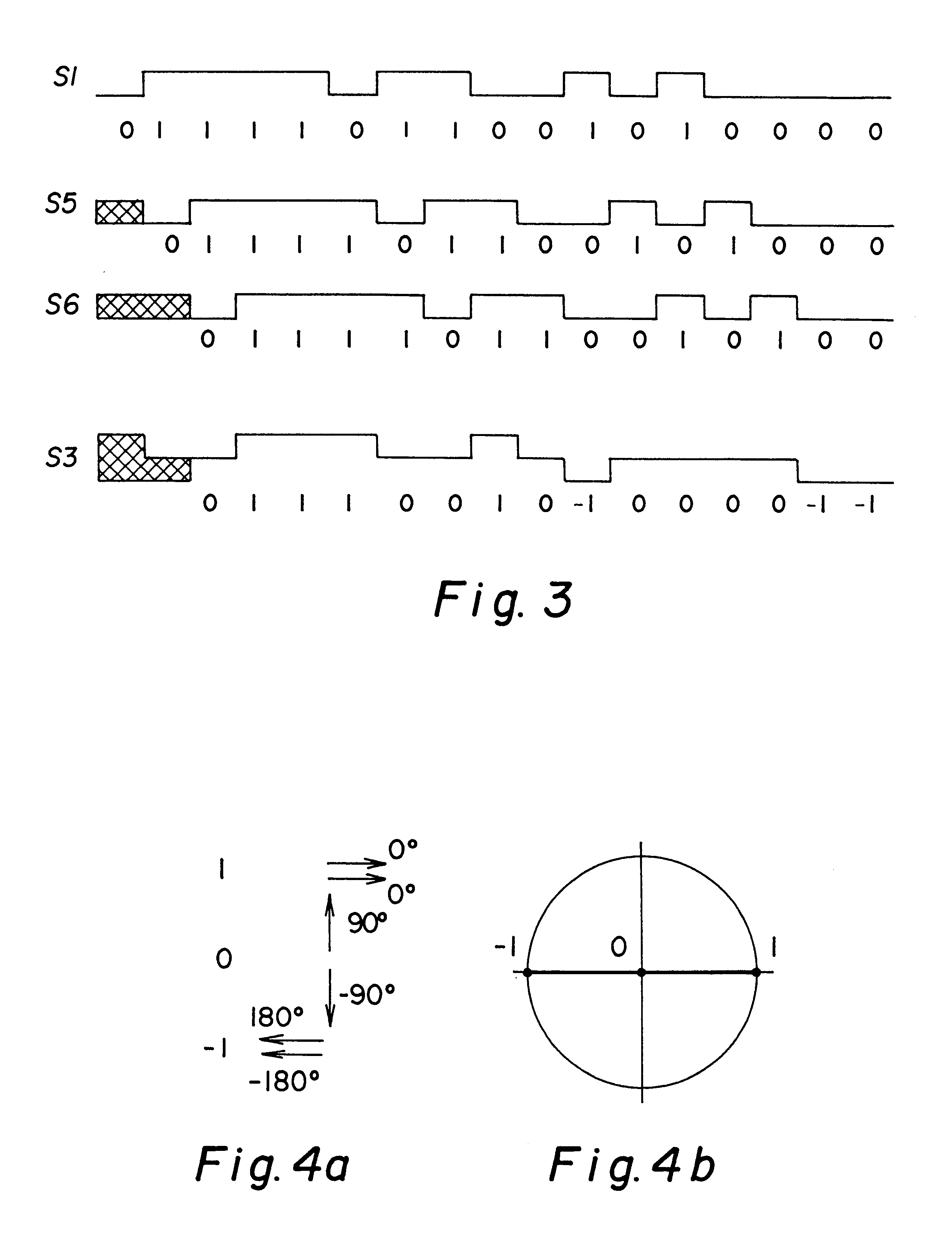

The present invention relates to an optical duobinary transmitter system and method using optical intensity modulation. The system comprises an input terminal (51) arranged to receive a first binary signal, a driving circuit (53) connected to the input terminal and arranged to convert the first binary signal into a second and a third binary signal, a double electrode optical modulator (55) connected to the driving circuit in such a way that its upper and lower electrode may be driven by said second and third binary signal, respectively, said modulator being further arranged to modulate the amplitude and phase of an optical carrier according to the binary driving signals so as to provide an optical duobinary signal corresponding to said first binary signal and with a predetermined negative modulation chirp parameter, and an output terminal (57) connected to the optical modulator and arranged to feed an optical transmission line with the modulated optical duobinary signal. The modulator may alternatively be arranged to be driven by quasi-ternary signals.

Owner:TELEFON AB LM ERICSSON (PUBL)

RZ-AMI optical transmitter module

InactiveUS20050078965A1Electromagnetic transmittersElectromagnetic receiversAudio power amplifierOptical transmitter

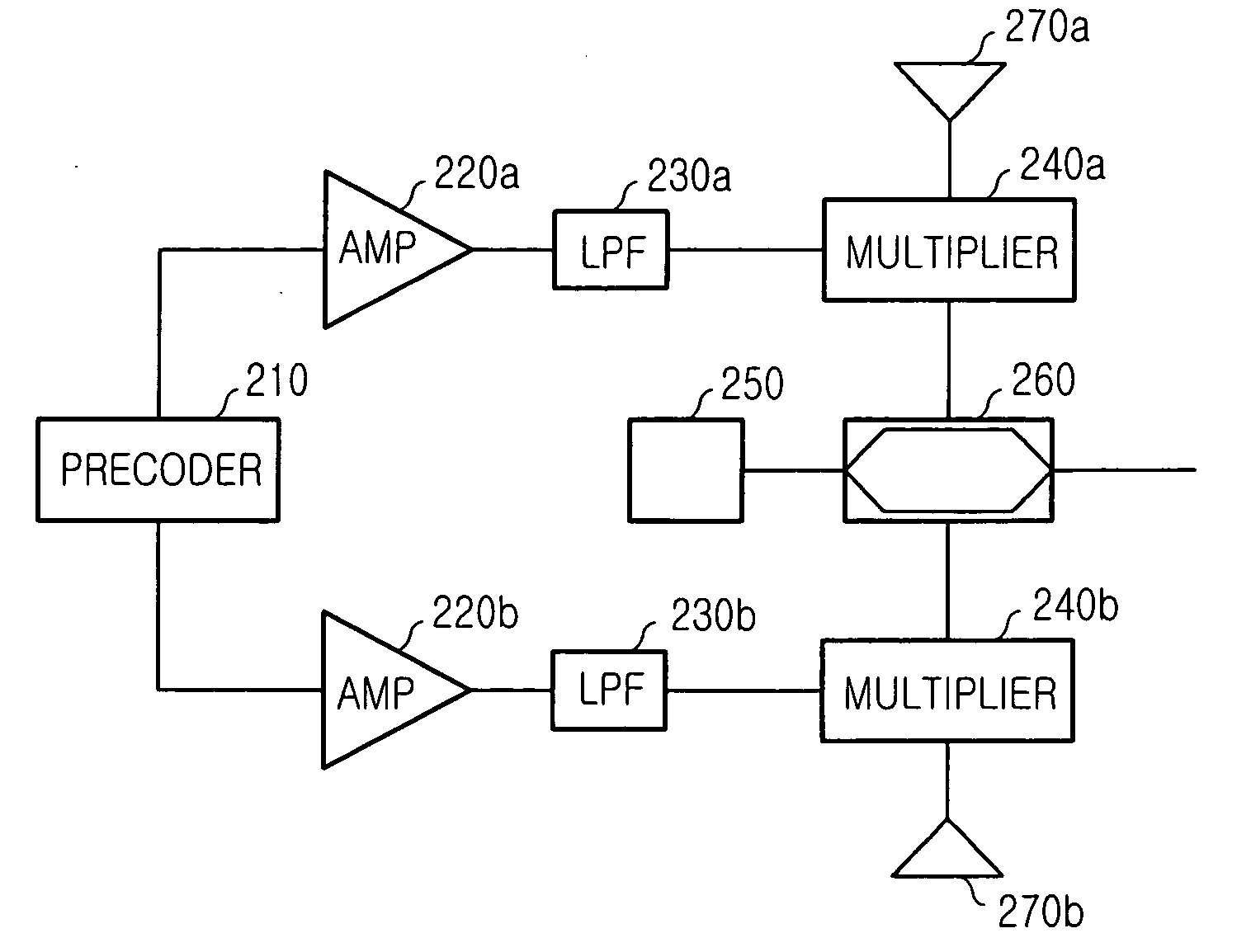

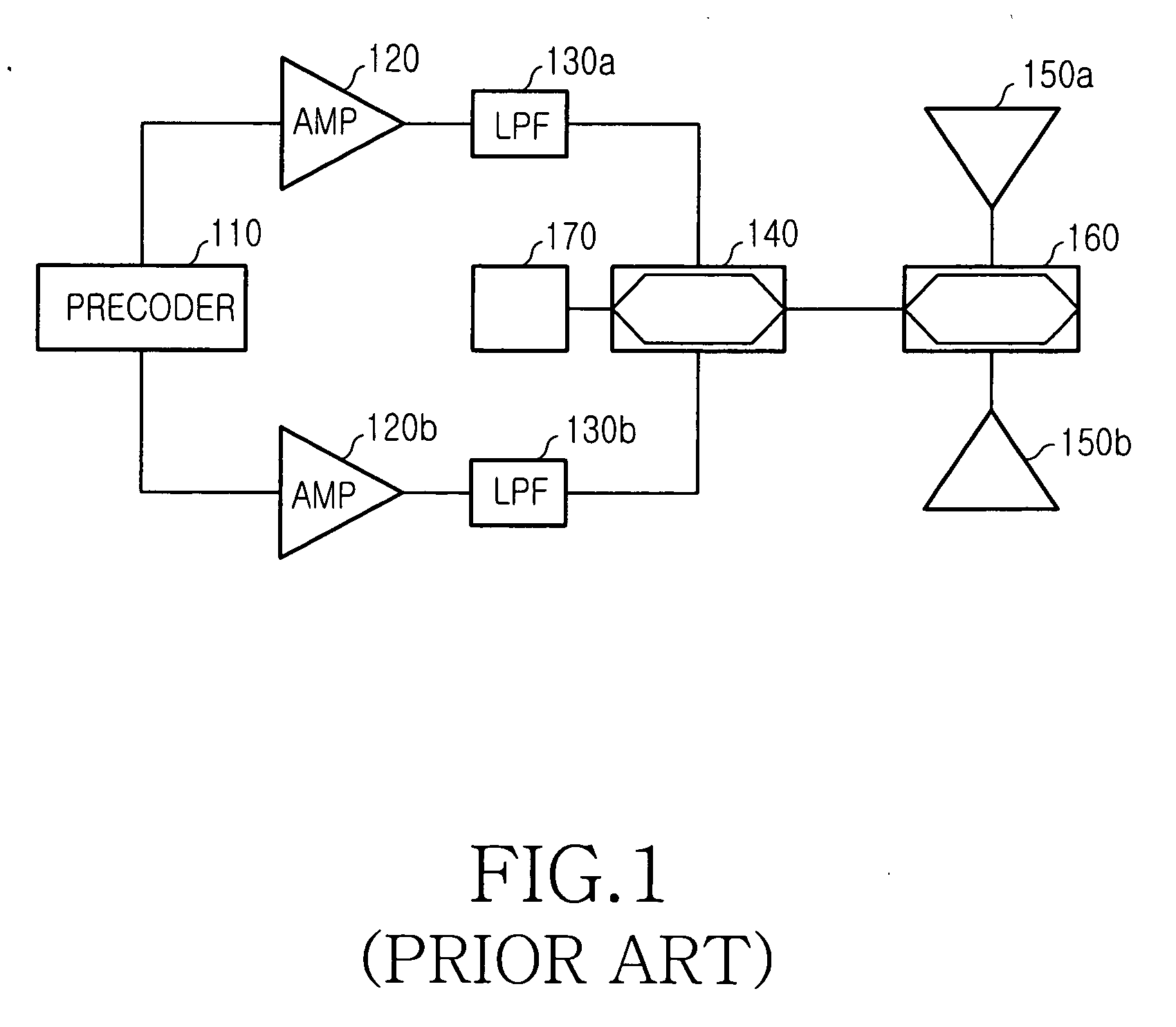

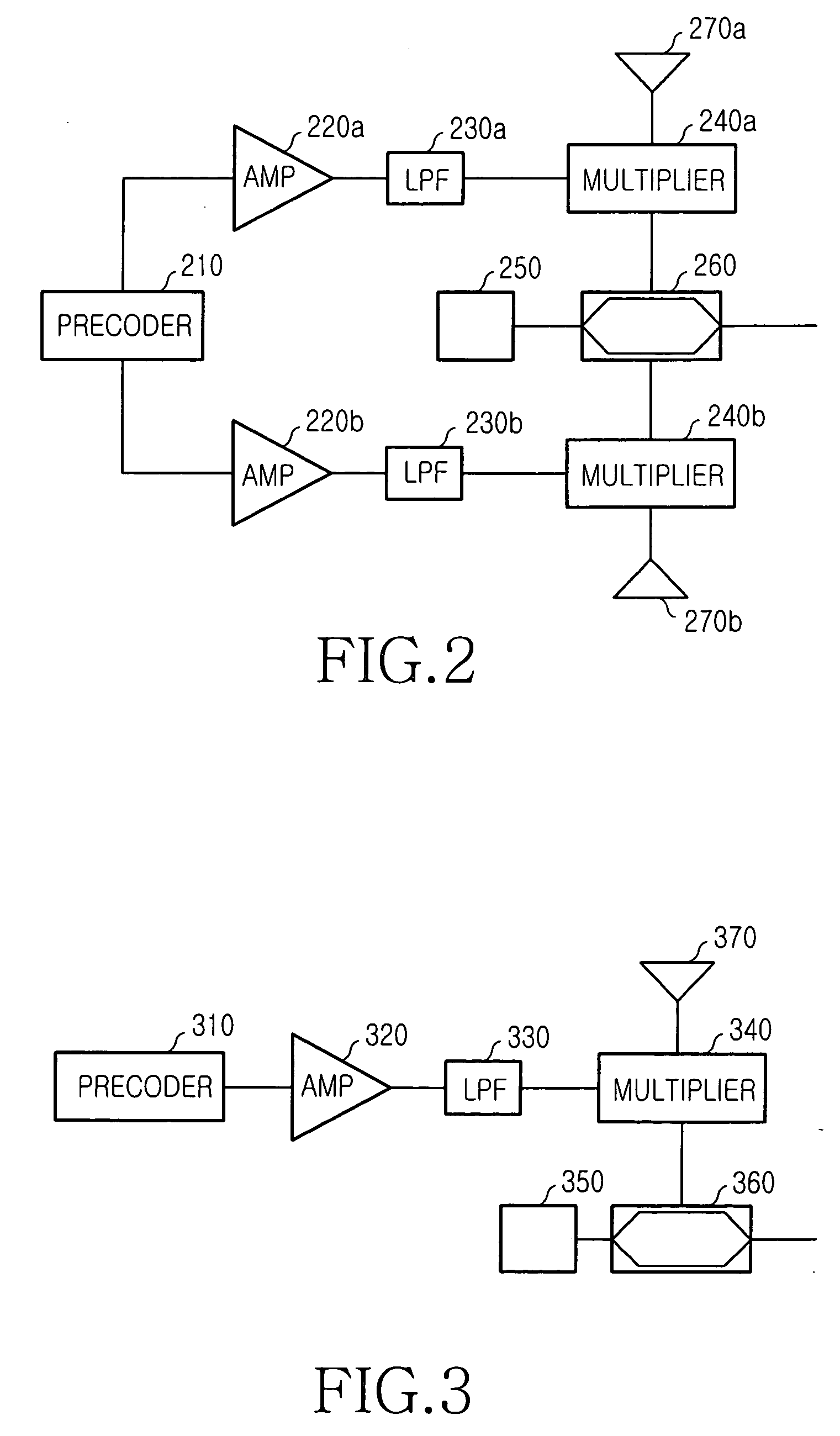

Disclosed is an optical transmitter module comprising: a precoder to generate an encoded binary signal from an electric signal; an amplifier to amplify the binary signal; a converter to convert the amplified encoded binary signal into a limited ternary signal; a frequency generator to generate a sine wave having a predetermined frequency; a multiplier to multiply the ternary signal using the sine wave; a light source to generate a coherent CW light having a constant intensity; and a Mach-Zehnder modulator to modulate the CW light according to the ternary signal from the multiplier.

Owner:SAMSUNG ELECTRONICS CO LTD

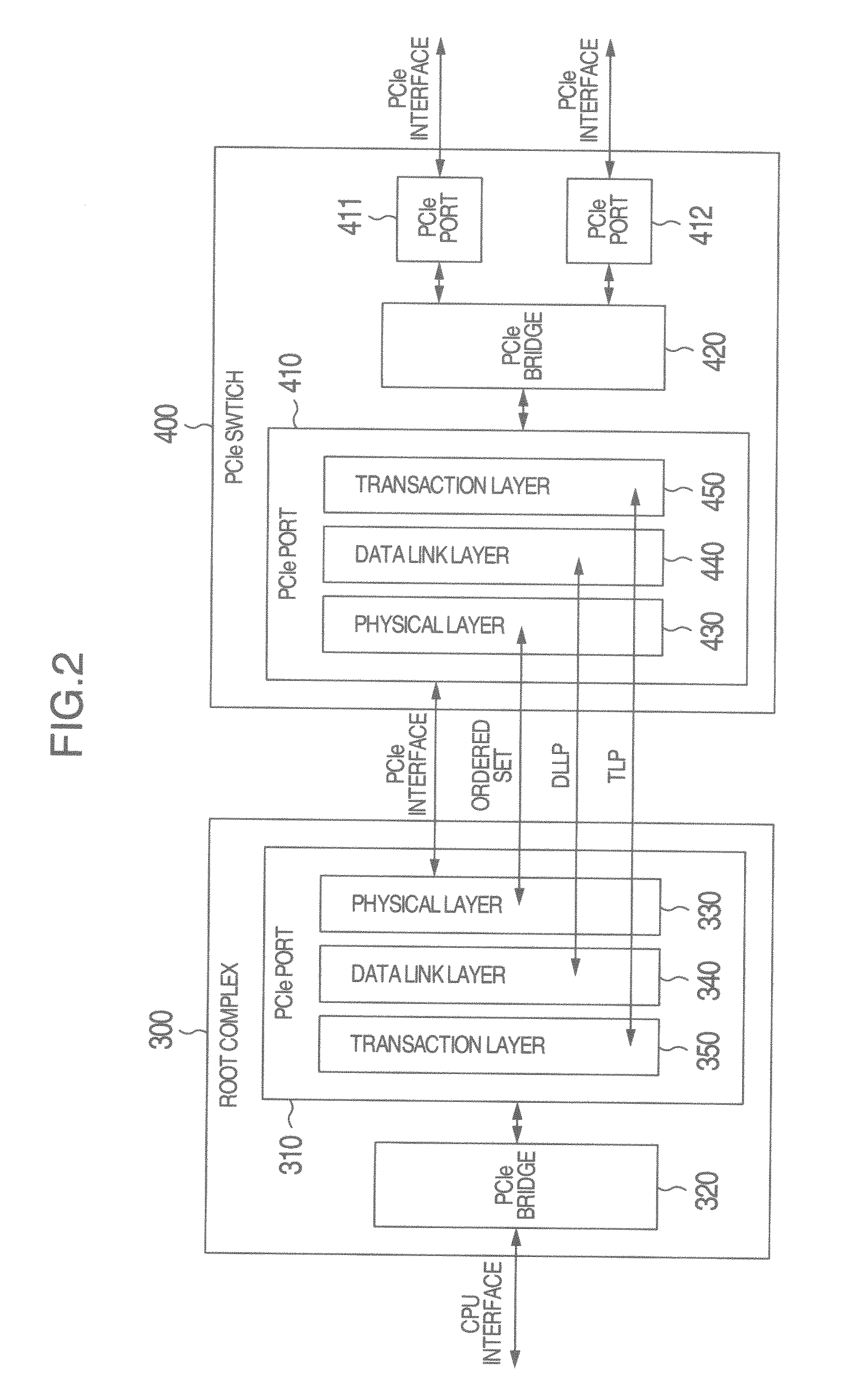

Computer system and method for signal transmitting

InactiveUS20120191887A1Avoid misuseAvoid it happening againElectric digital data processingControl signalComputerized system

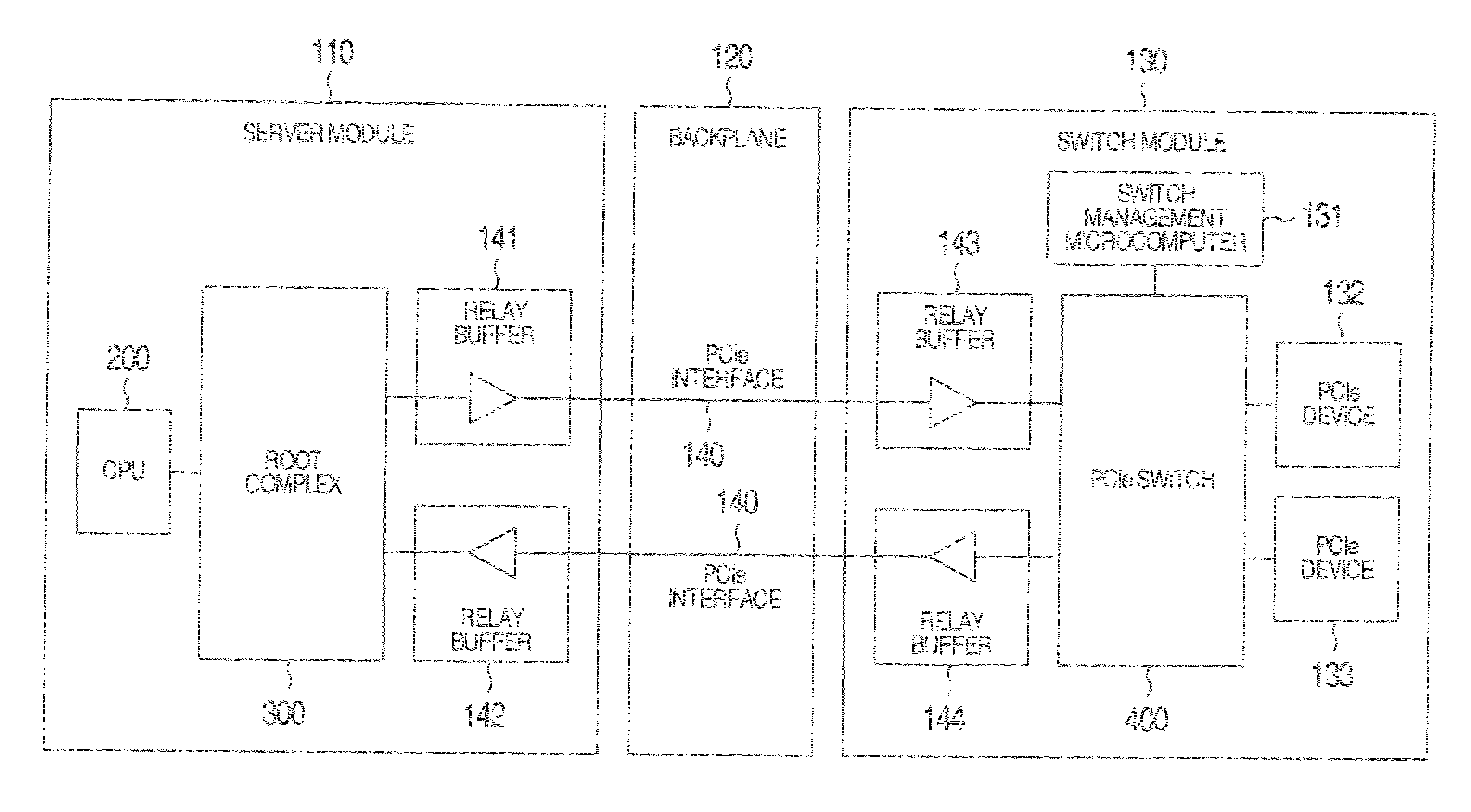

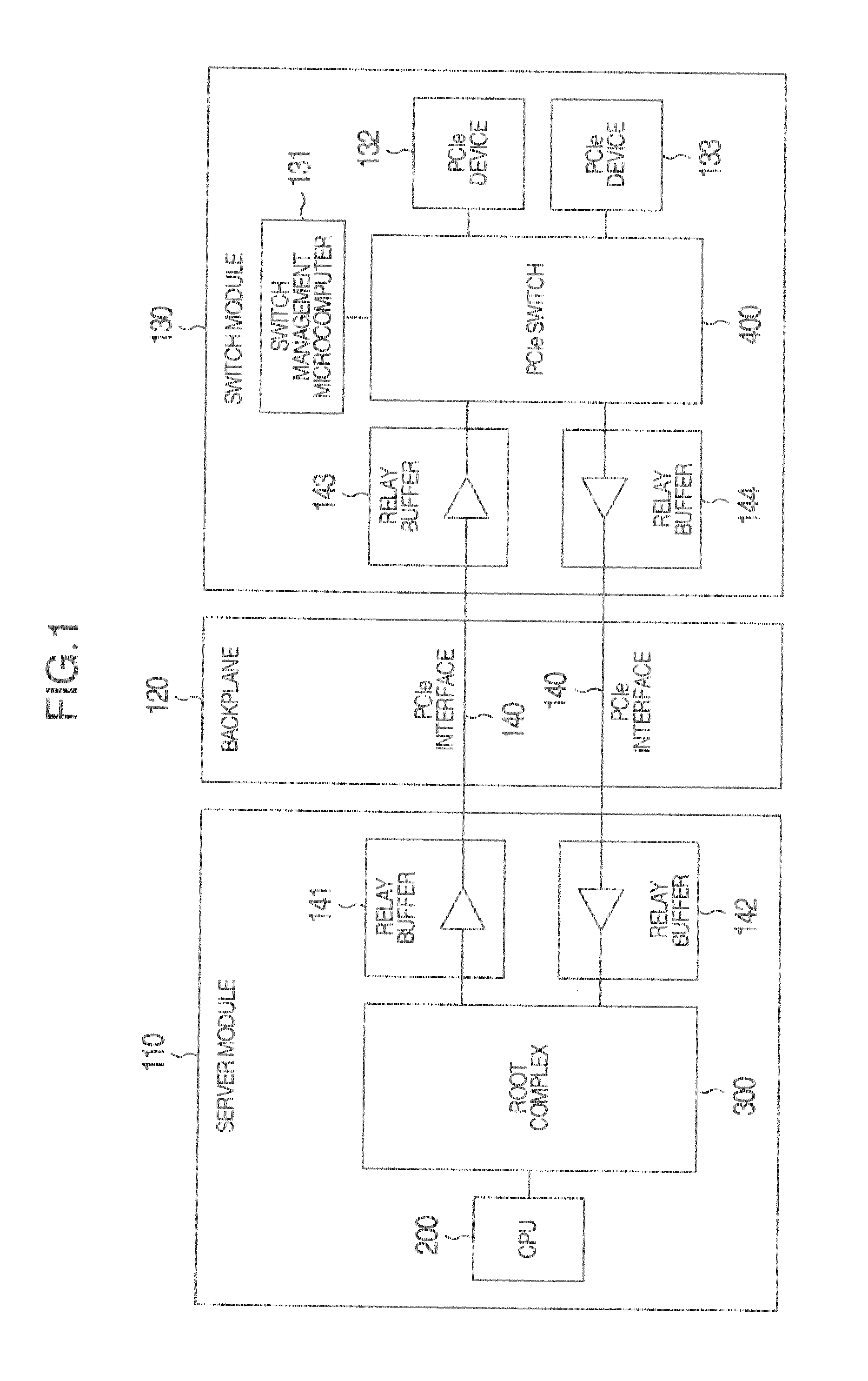

In order to suppress occurrence of a random pattern signal is suppressed without the use of a sideband signal in a long distance data transmission exceeding that defined in a PCIe interface specification, provided is a computer system, including a first component having a transmitting unit which transmits a control signal, a second component having a receiving unit which receives the control signal, a transmission path which connects the first component and the second component along which a signal is transmitted and received, wherein: in case of the transmitting unit of the first component transmits a ternary signal with three states of 0 / 1 / Idle to the receiving unit of the second component, the transmitting unit of the first component substitutes a combination of signals representing 0 / 1 for a signal representing the Idle state, and transmits the substituted signals instead of the ternary signal to the receiving unit of the second component.

Owner:HITACHI LTD

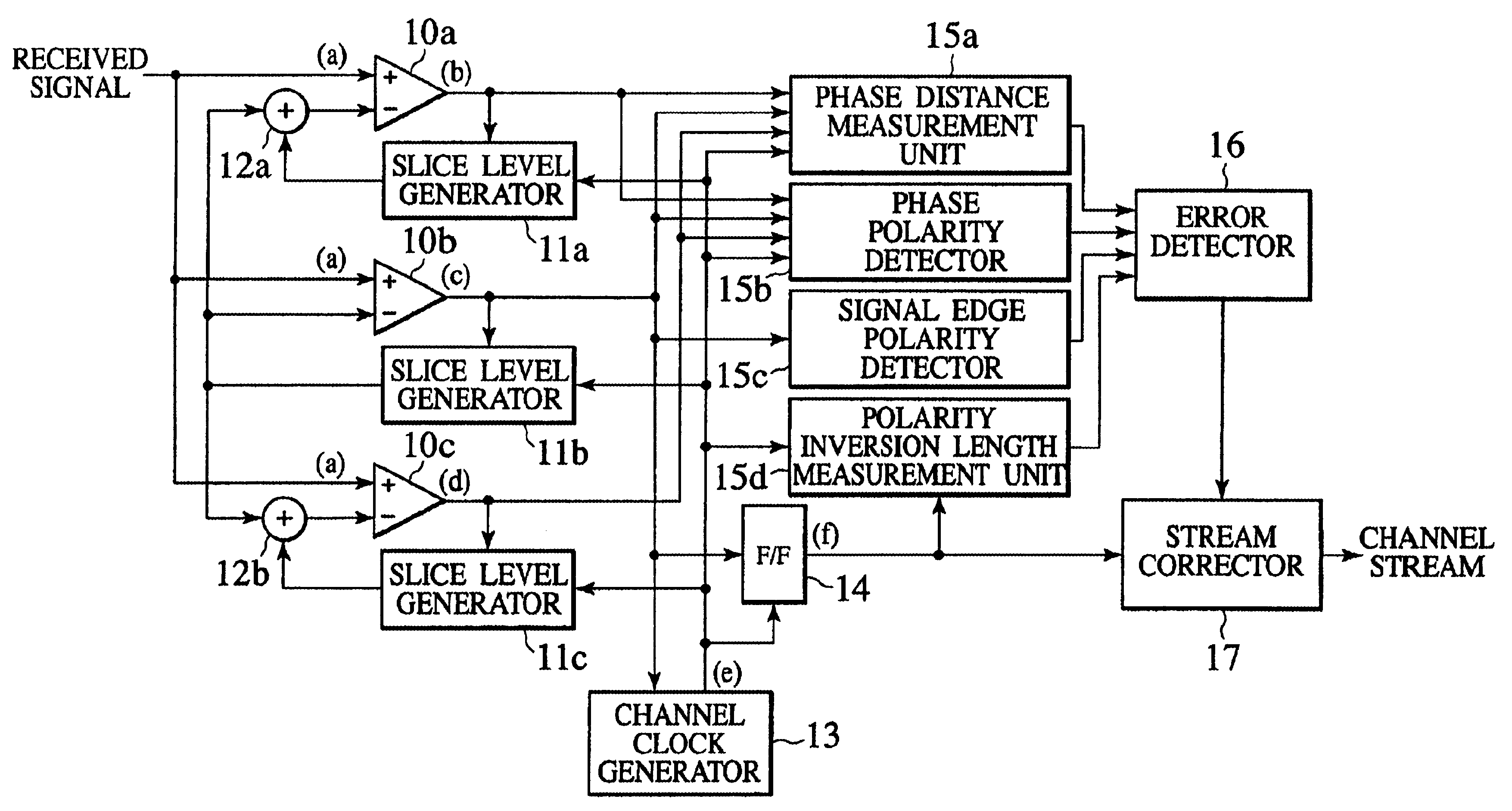

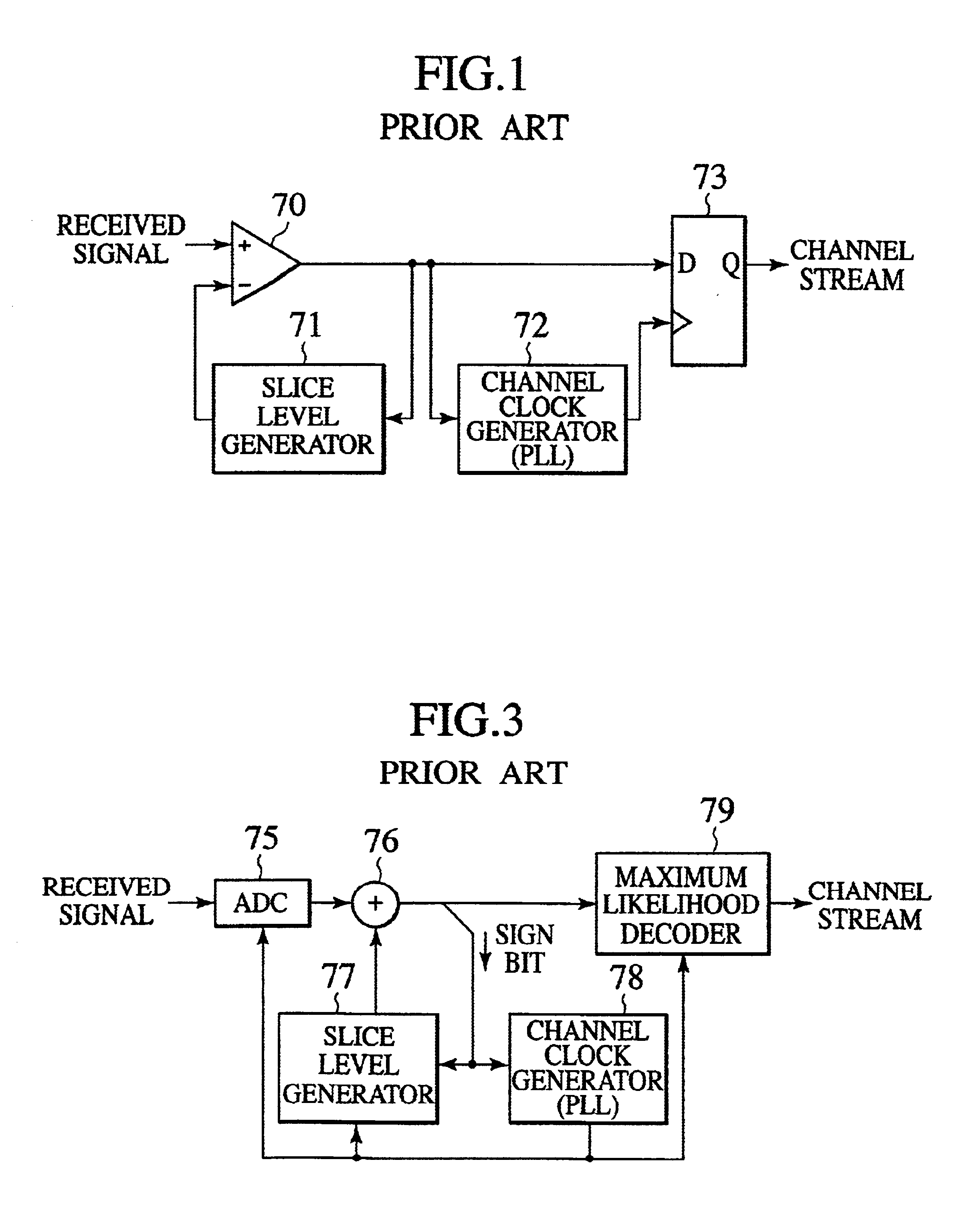

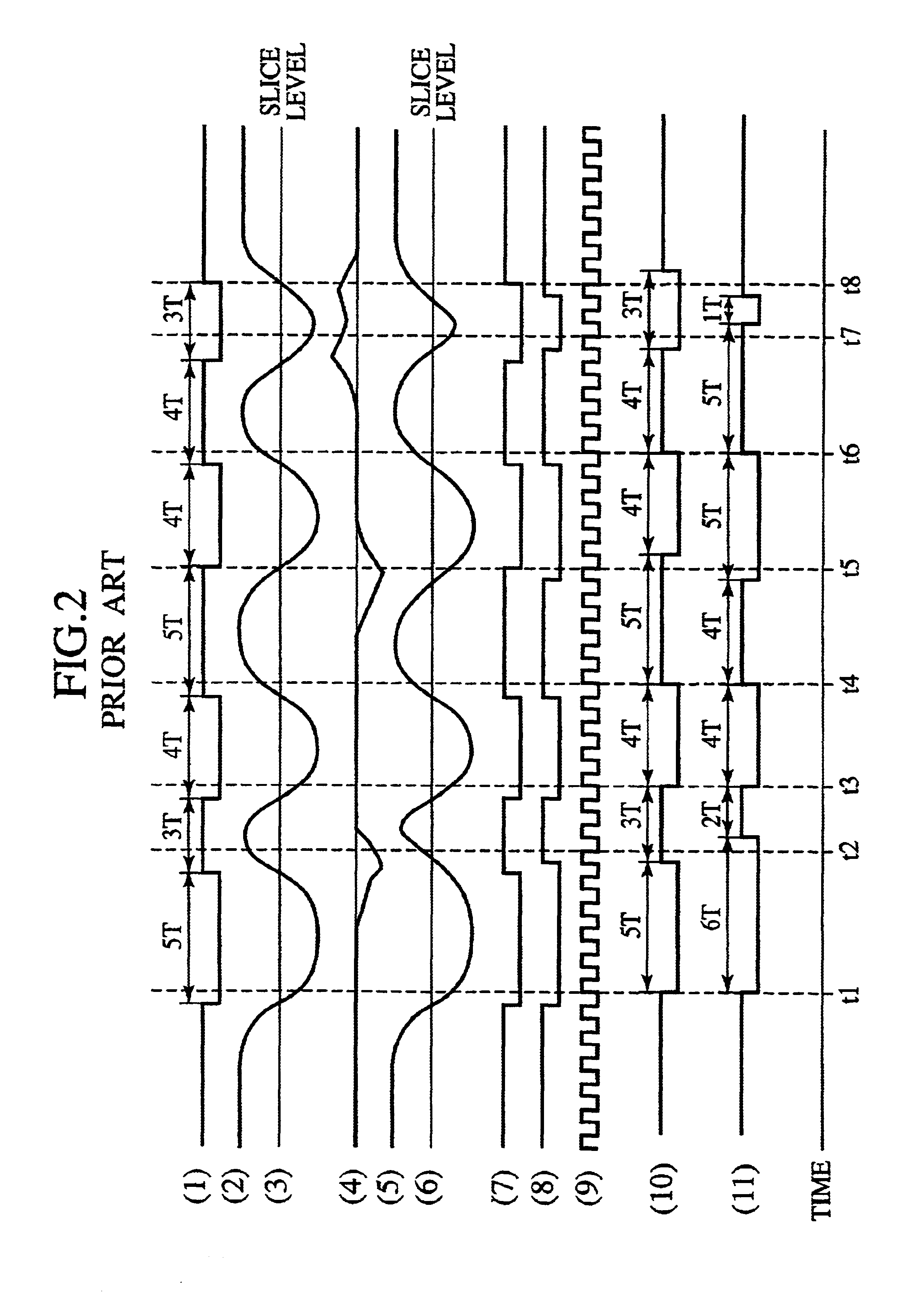

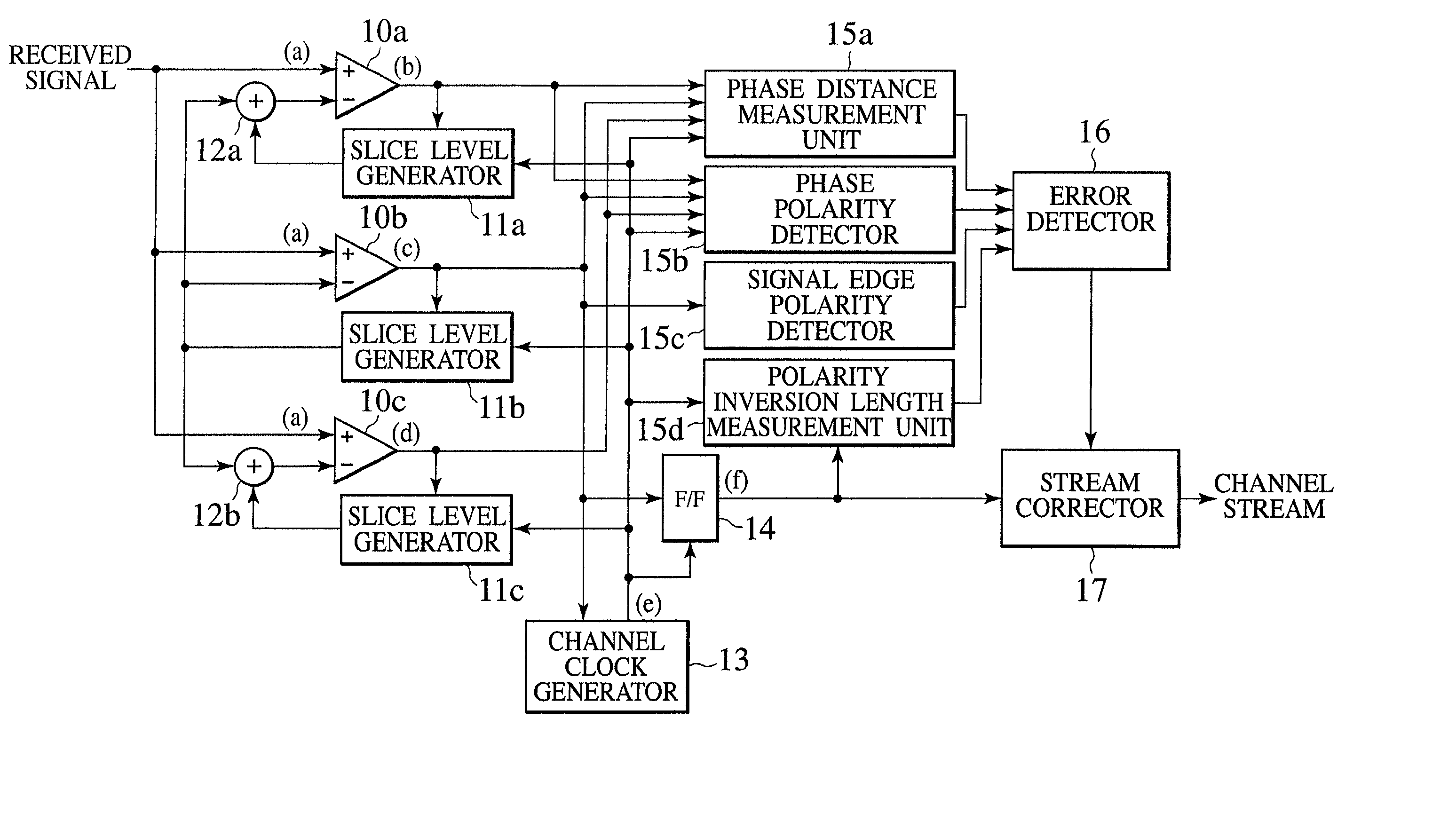

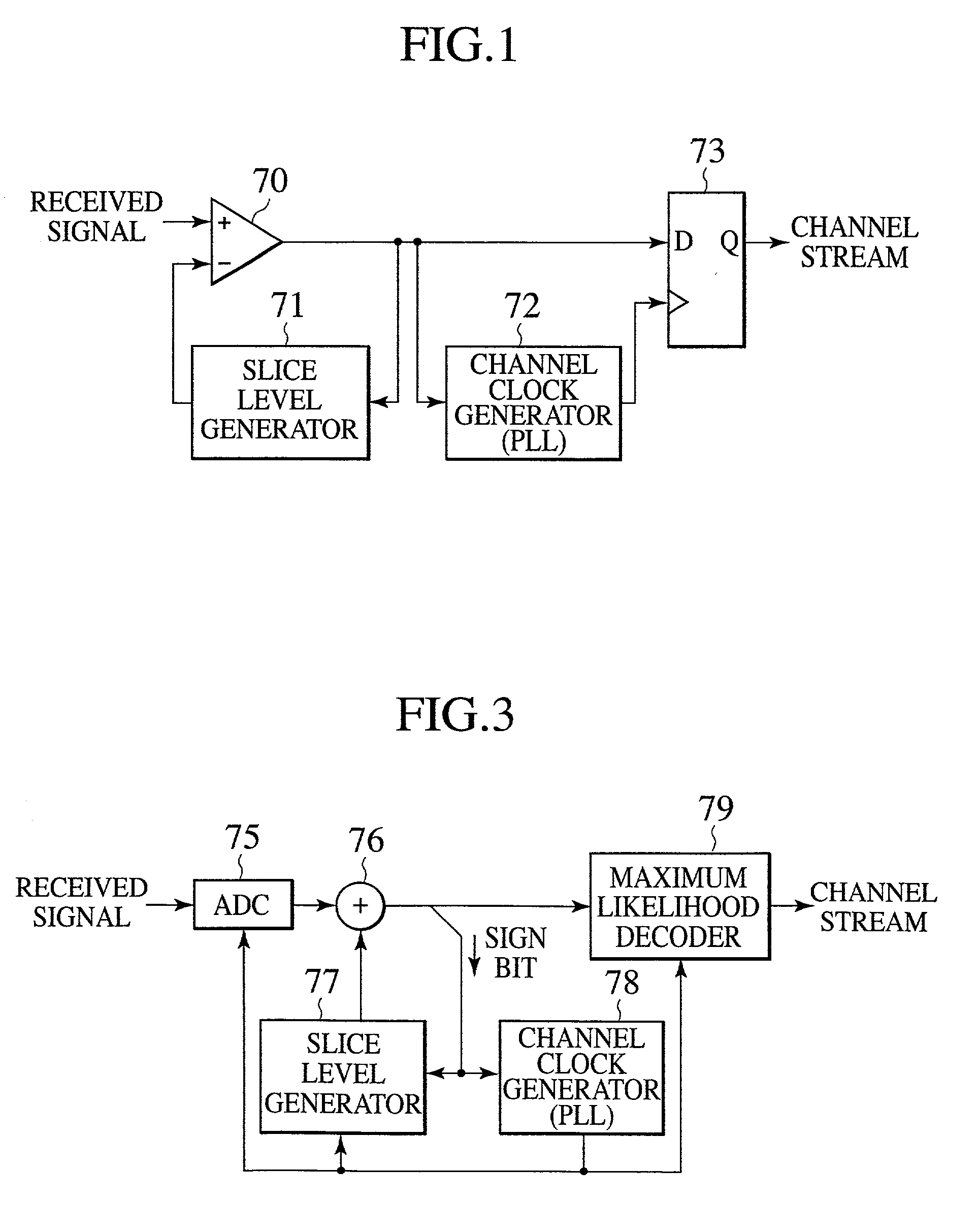

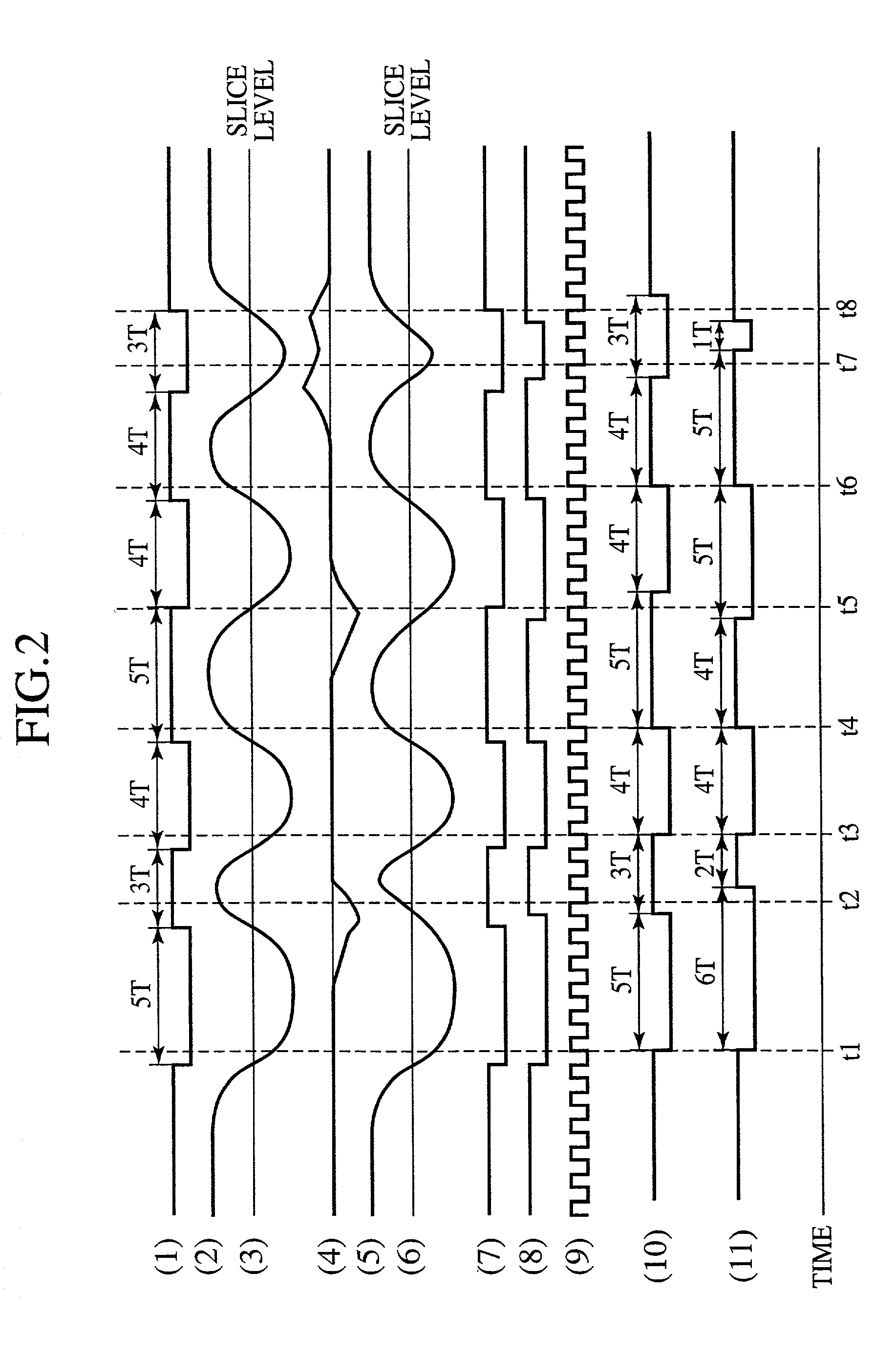

Read channel circuit and method for decoding using reduced-complexity error correction

A decoding technique is disclosed for proving inexpensively a read channel circuit which has an error correction function and is applicable to high channel frequencies. In this read channel circuit, generating a reference slice level signal and a plurality of slice level signals which are different from the reference slice level signal, converting the playback signal into a plurality of binary signals synchronized with a channel clock according to each of the slice level signals, selecting two binary signals, measuring the phase distance between the two binary signals, judging the polarity of an inverted edge of a reference binary signal, and generating an error correction signal on the basis of the phase distance and the polarity of the inverted edge of the reference binary signal, whereby any error in the playback signal can be eliminated.

Owner:KK TOSHIBA

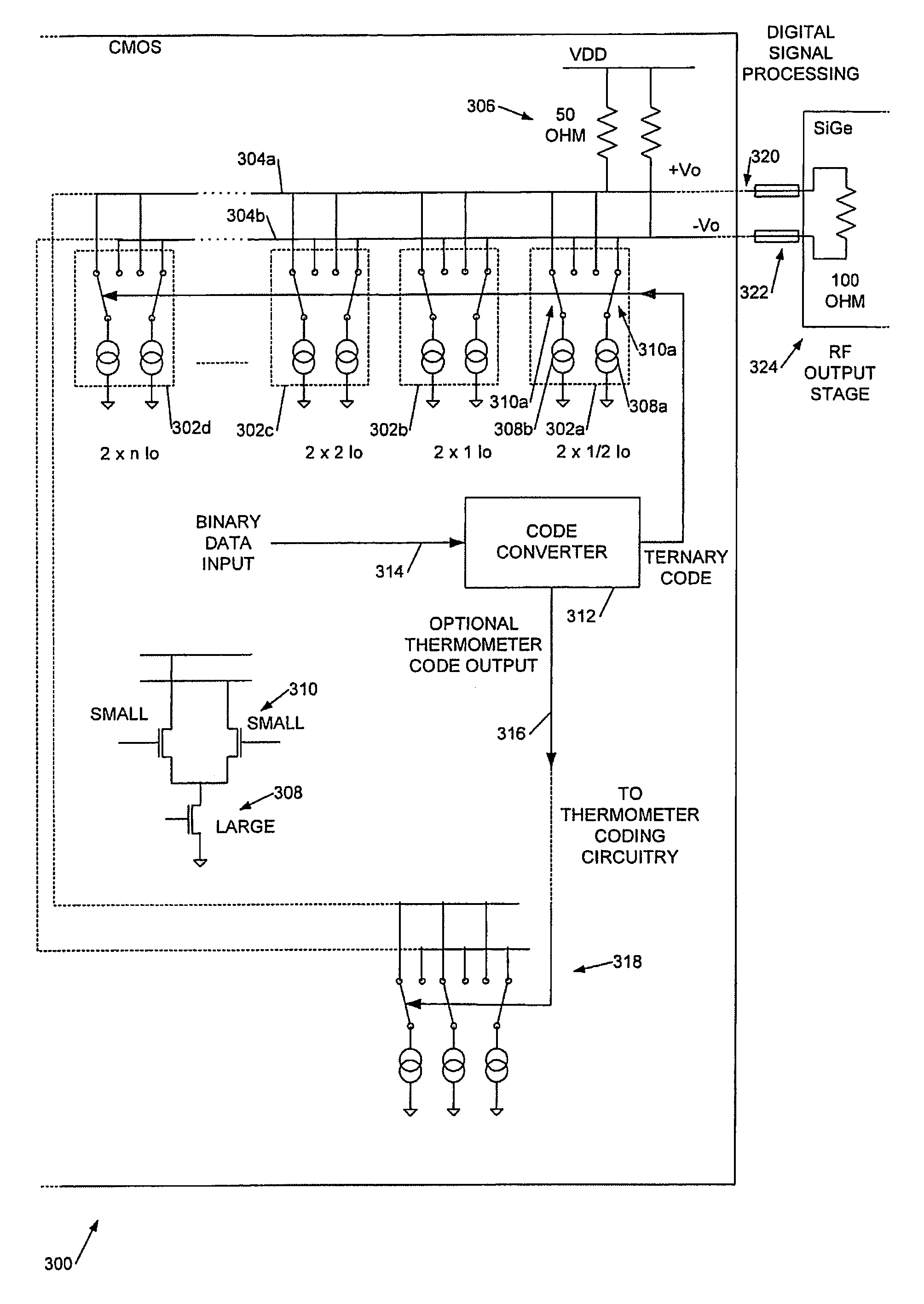

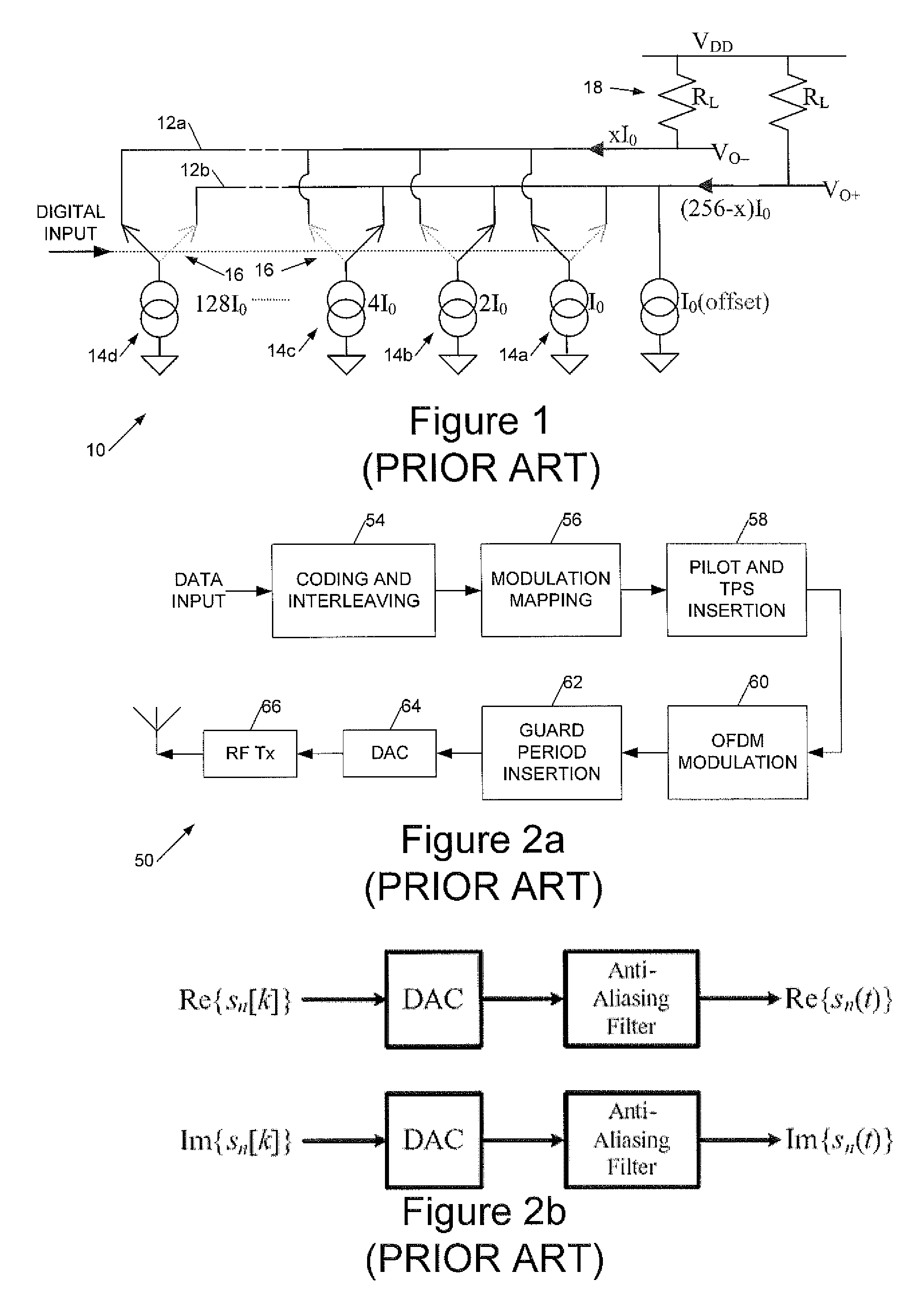

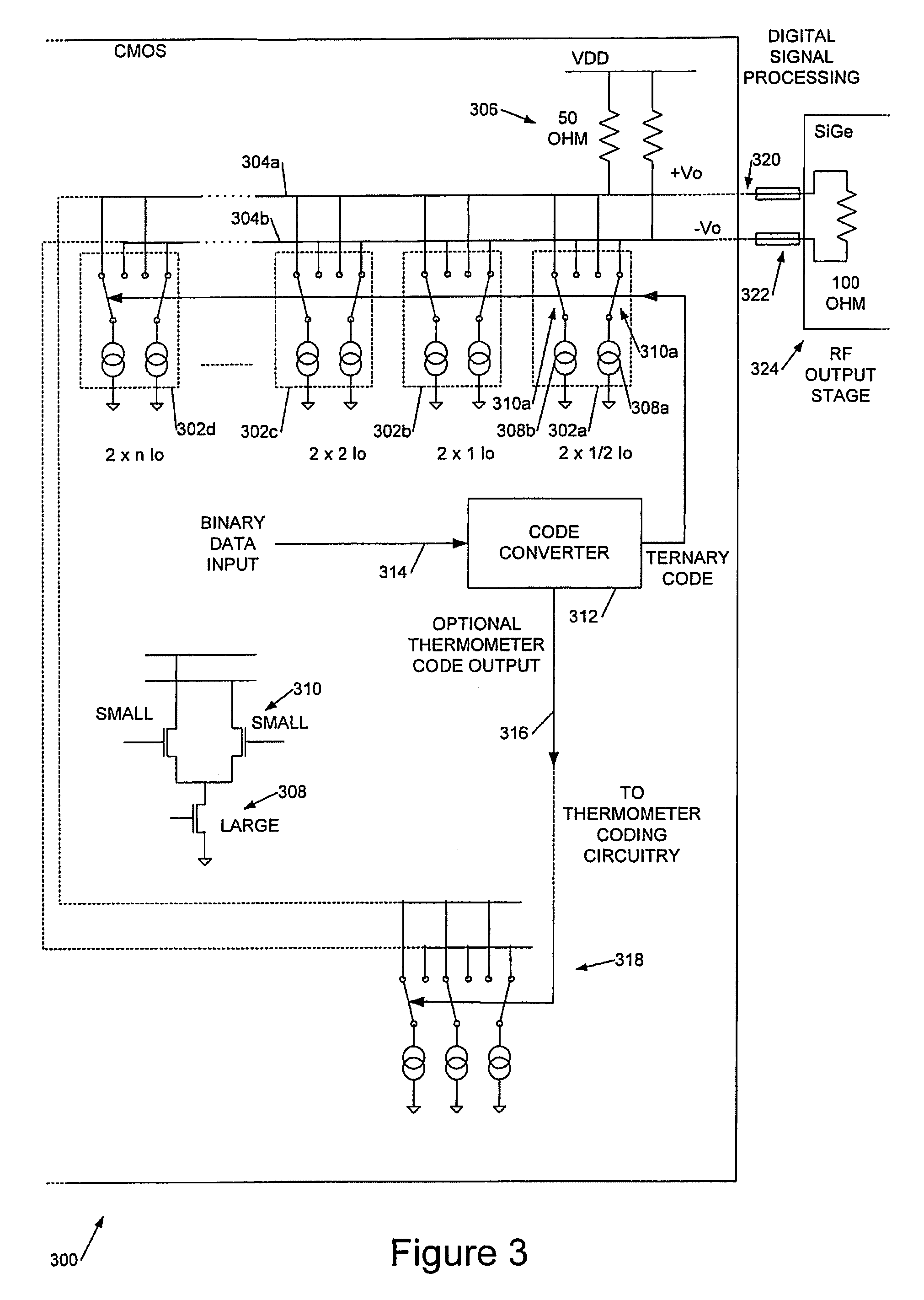

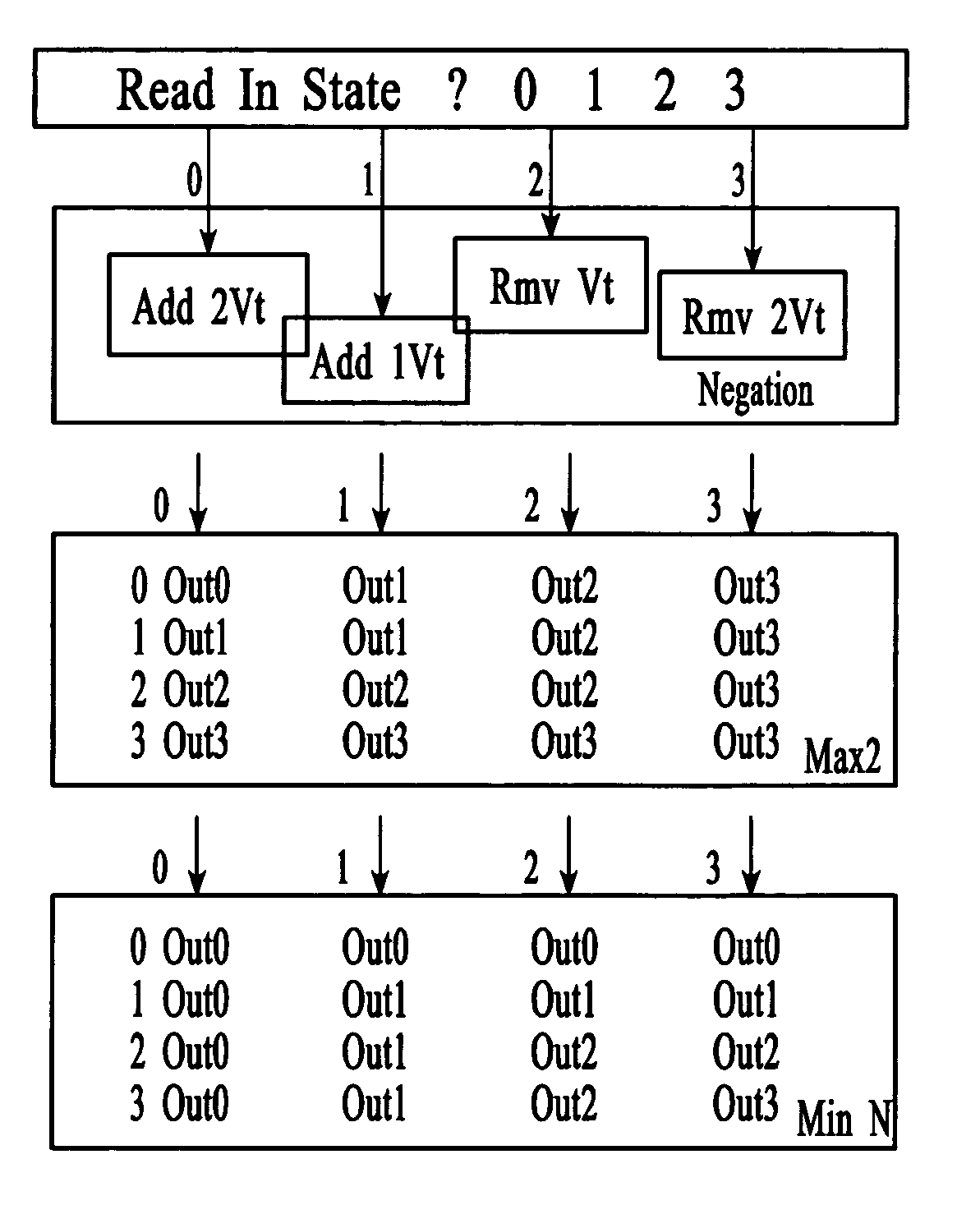

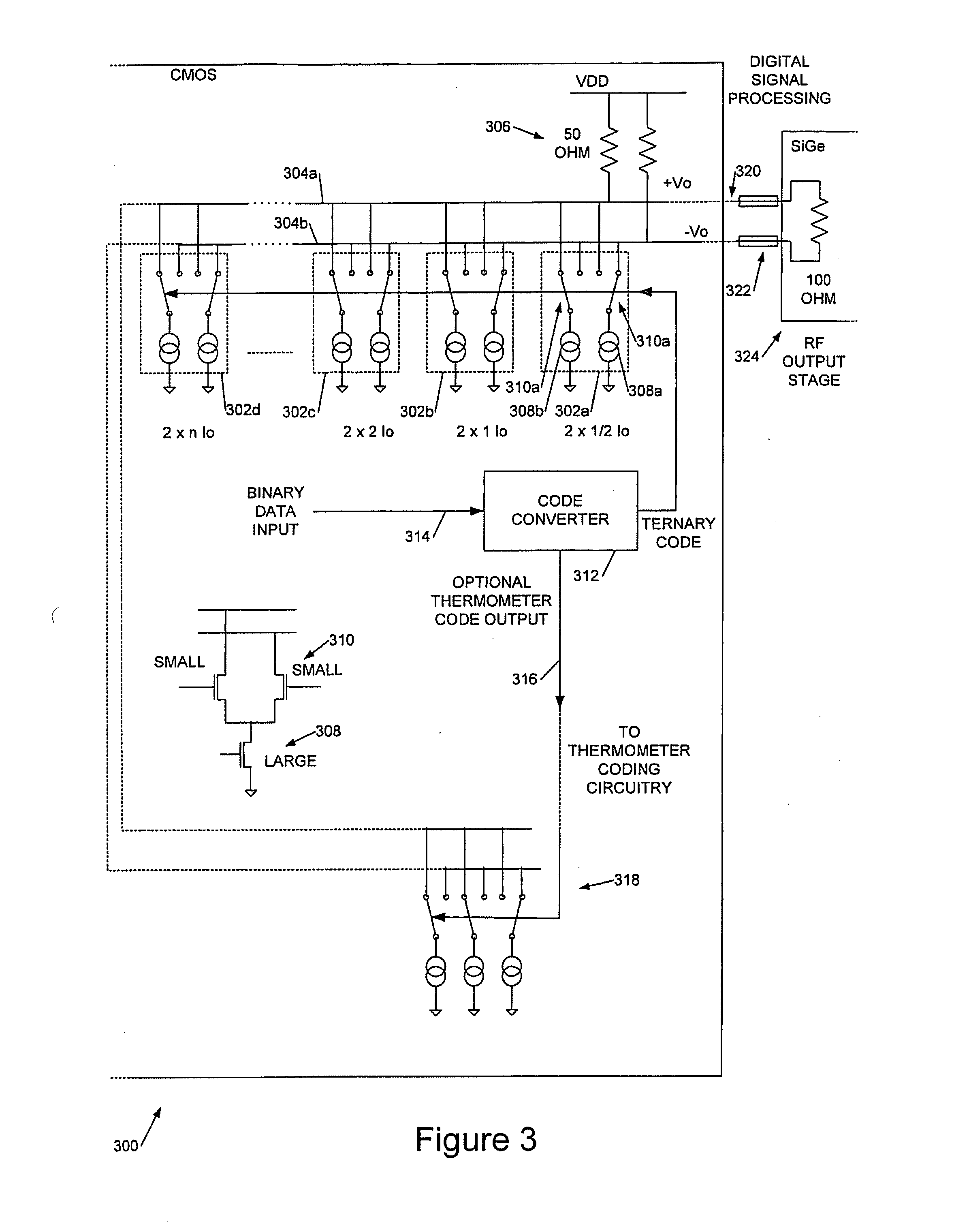

Differential current-steering digital-to-analog converter

InactiveUS7369077B2Reduce noiseElectric signal transmission systemsDigital-analogue convertorsCurrent generatorDigital input

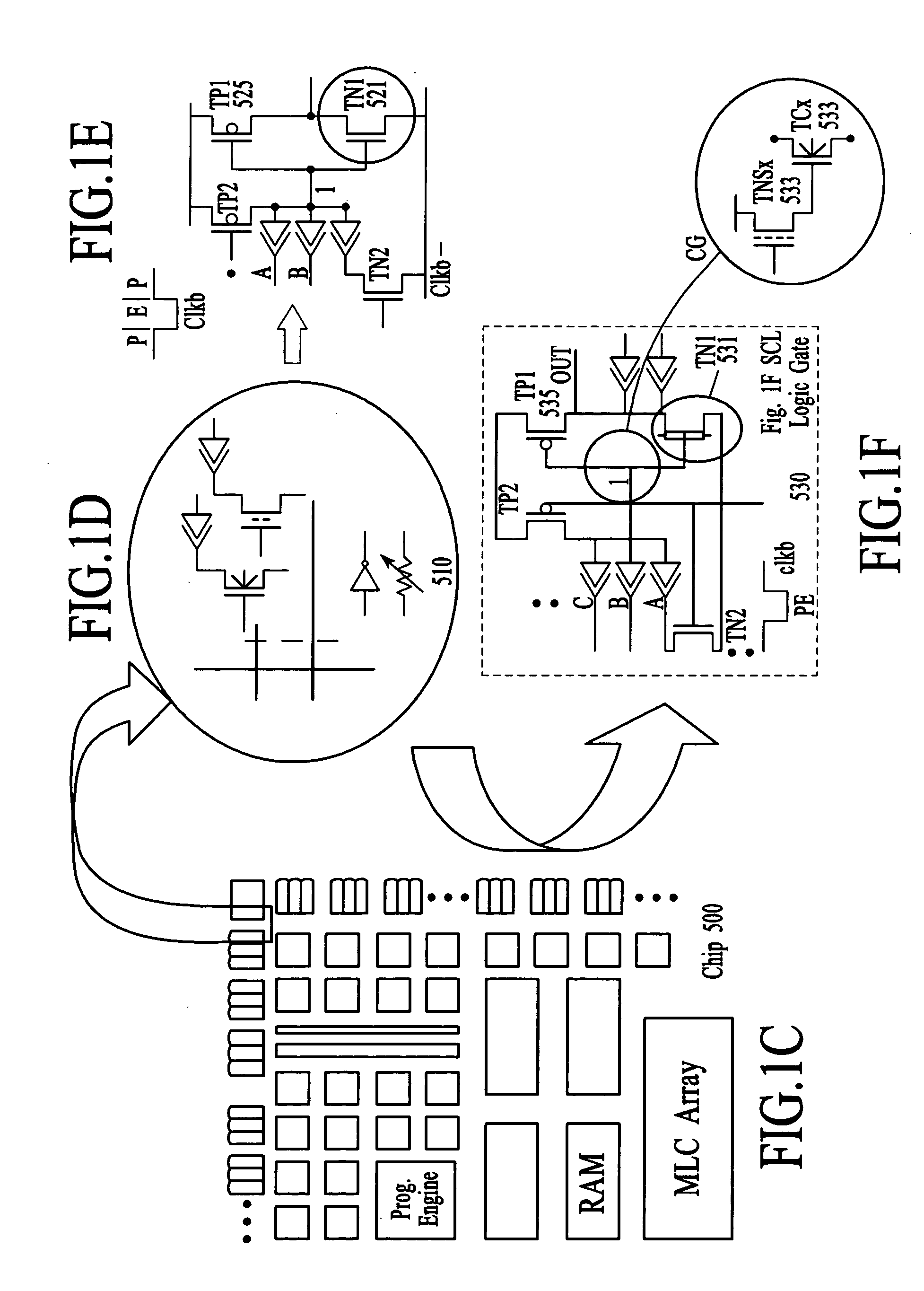

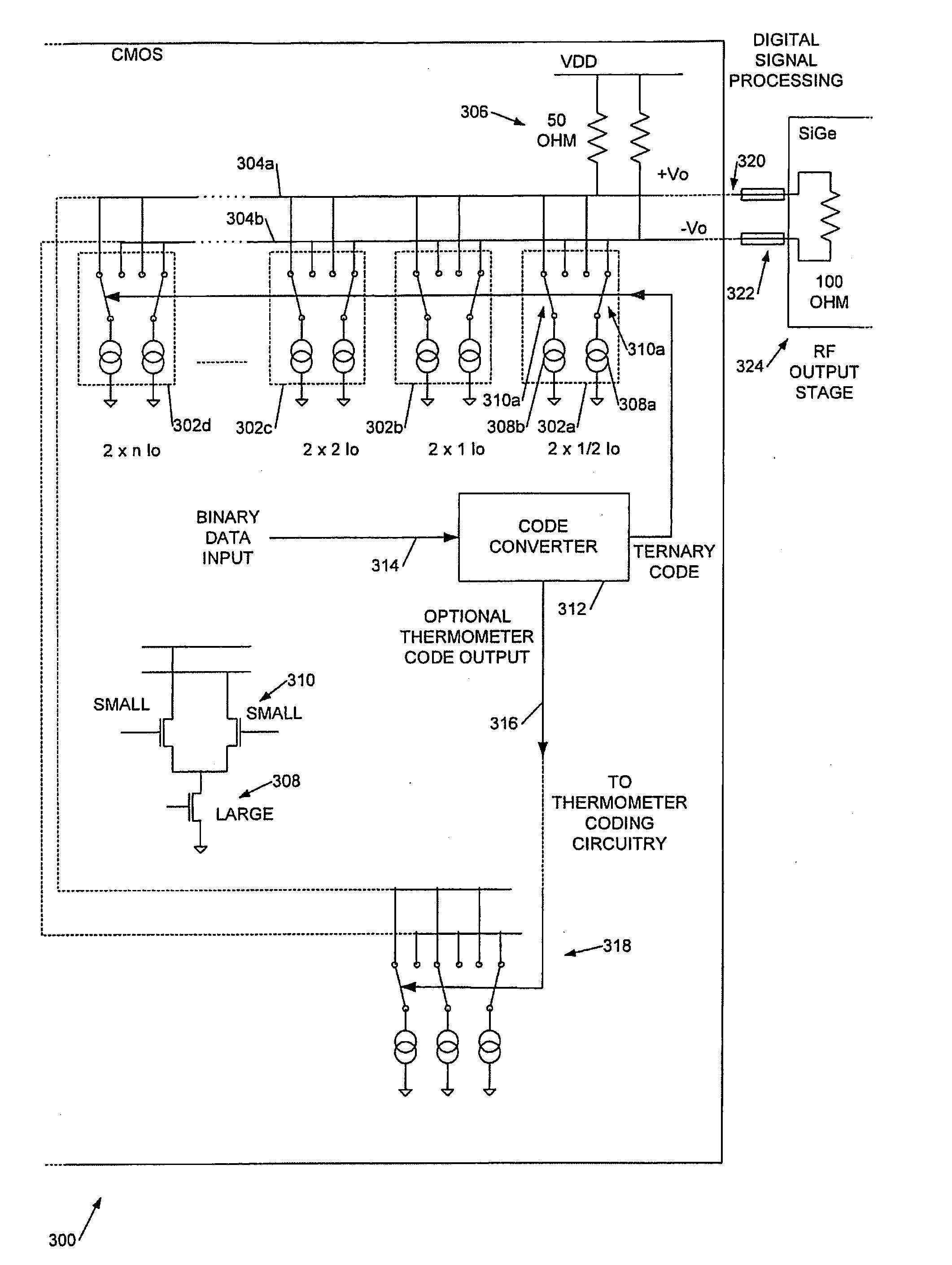

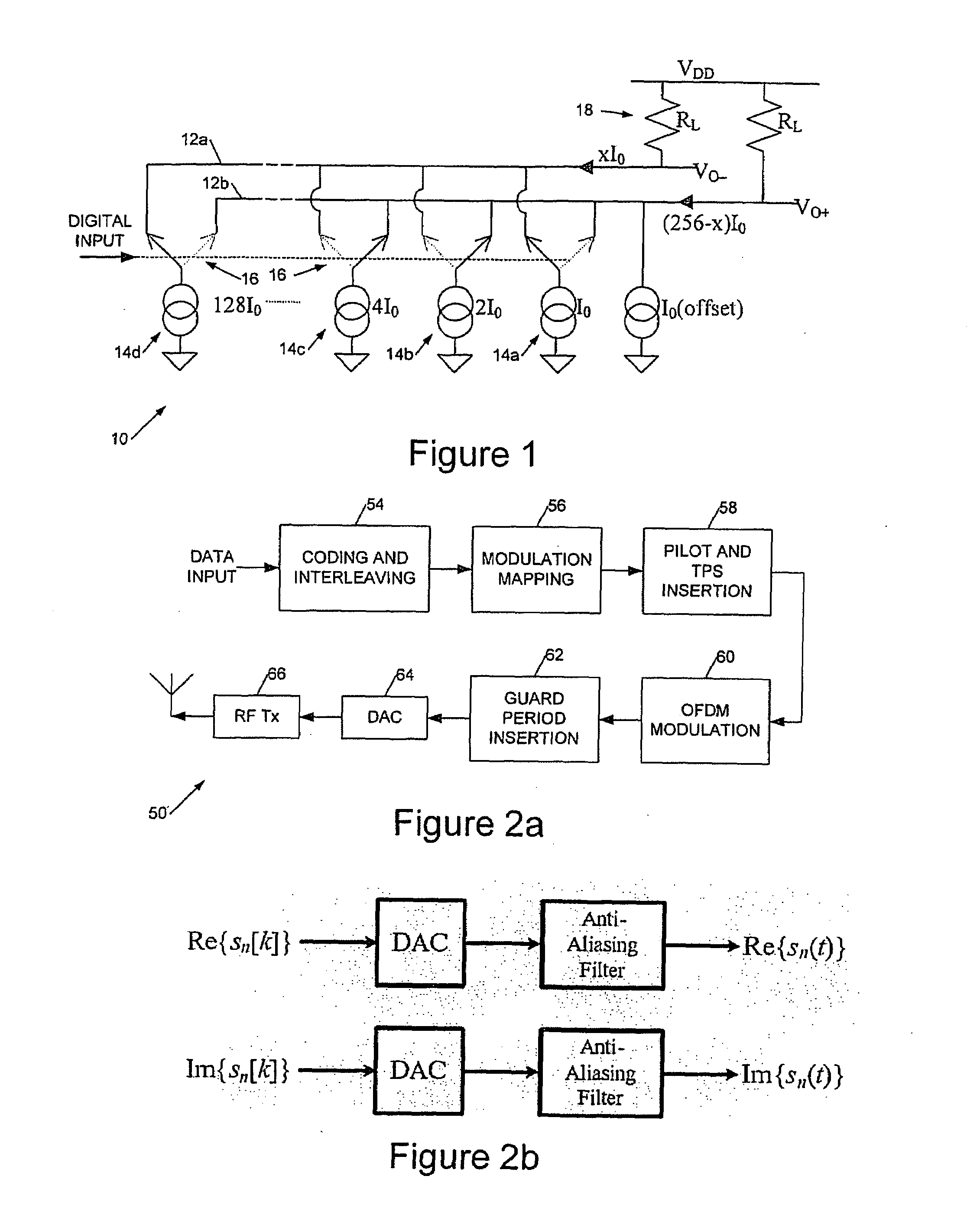

Differential, current-steering DACs with reduced small signal differential non-linearity. A set of binary-weighted steerable constant current generators is used in which each constant current generator comprises a ternary constant current generator configured to generate a three-state differential current in response to a ternary signal on a control input. Each ternary current generator is associated with a bit of the binary code. The DAC further comprises a code converter coupled between a digital input, to receive a signed digital value for conversion, and control inputs of the steerable current generators, to convert the binary input code to a ternary code to control the steerable current generators to provide a differential analogue output. In embodiments the smallest current source is ½I0 where I0 is a change in differential output current caused by an lsb change in the binary input code.

Owner:INTEL CORP

Quaternary and trinary logic switching circuits

InactiveUS20050258863A1Increase spacingIncrease powerMultistate logicSolid-state devicesCost effectivenessTime efficient

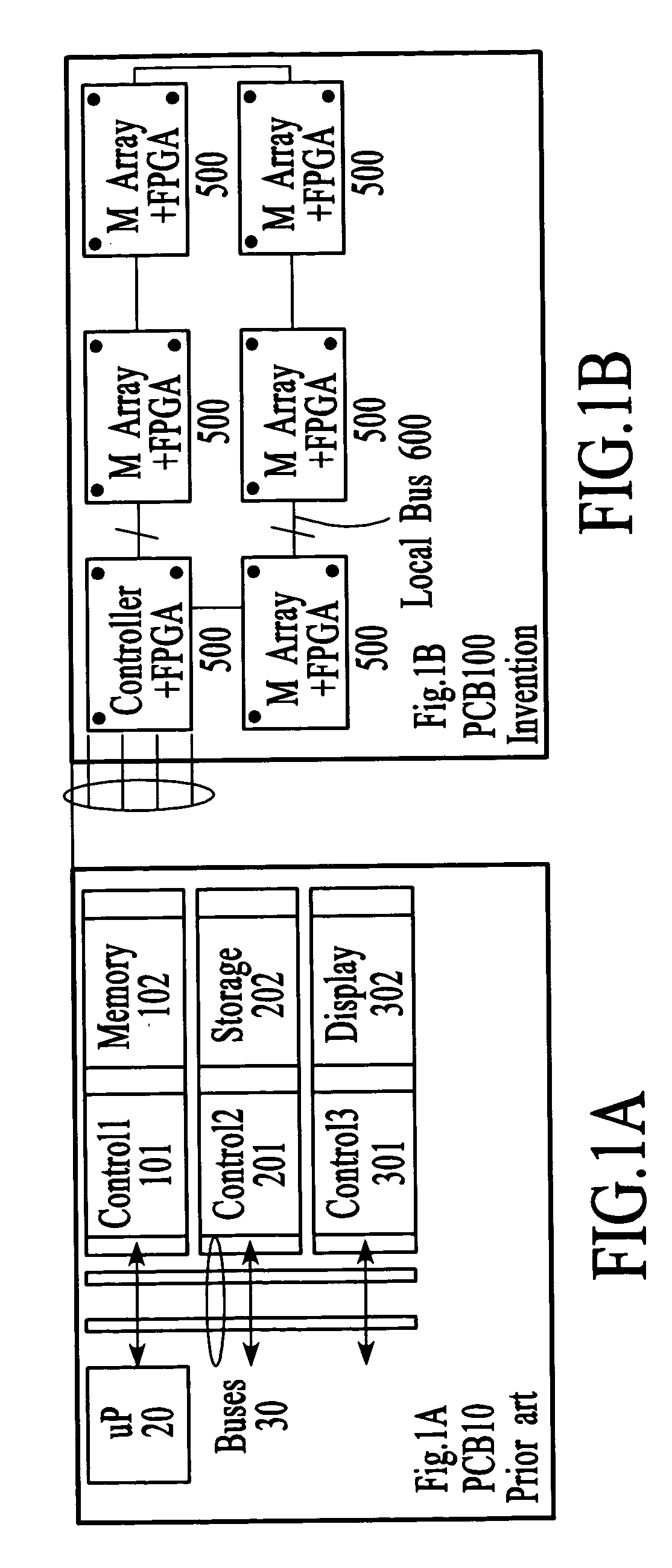

A logic circuit comprising a quaternary logic switching circuit which includes a multilevel storage cell (MLSC), and the trinary or variable threshold logic means to yield an improved space, power, and time-efficient performance device is disclosed. The present invention is used for the implementation of a customized new logic design to further improve the cost-effectiveness of the application. Advanced circuit solutions are provided using asynchronous clock controlled functional units which are field programmable. A diode capacitor ladder chain is also used on an on-chip power supply multiplier to support internal high voltage operations. A digital-to-analog-to-digital translation (DADT) apparatus is also provided utilizing the above identified circuits. Finally, a printed circuit board (PCB) net driver with a trinary signal wire provides 50% bandwidth increase over conventional binary solutions.

Owner:CHANG AUGUSTINE W +1

Digital-to-analogue converters

InactiveUS20070252739A1Reduce noiseElectric signal transmission systemsDigital-analogue convertorsDigital analog converterCurrent generator

Differential, current-steering DACs with reduced small signal differential non-linearity. A set of binary-weighted steerable constant current generators is used in which each constant current generator comprises a ternary constant current generator configured to generate a three-state differential current in response to a ternary signal on a control input. Each ternary current generator is associated with a bit of the binary code. The DAC further comprises a code converter coupled between a digital input, to receive a signed digital value for conversion, and control inputs of the steerable current generators, to convert the binary input code to a ternary code to control the steerable current generators to provide a differential analogue output. In embodiments the smallest current source is ½I0 where I0 is a change in differential output current caused by an 1sb change in the binary input code.

Owner:INTEL CORP

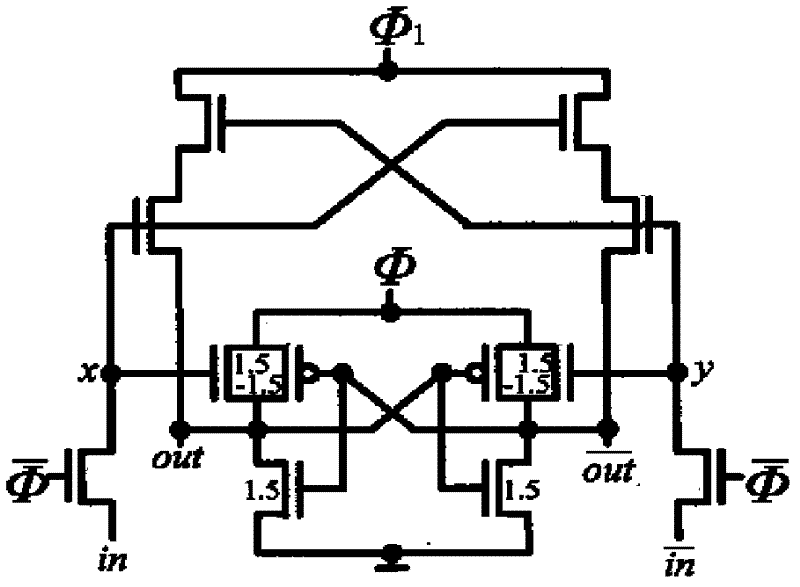

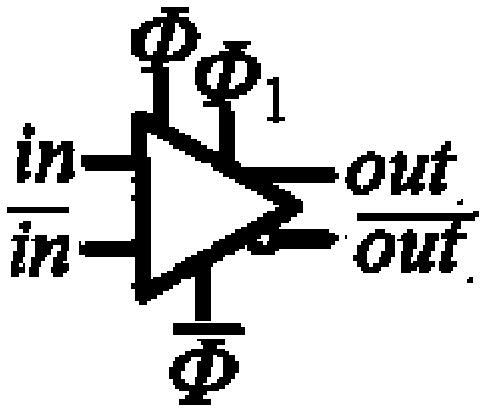

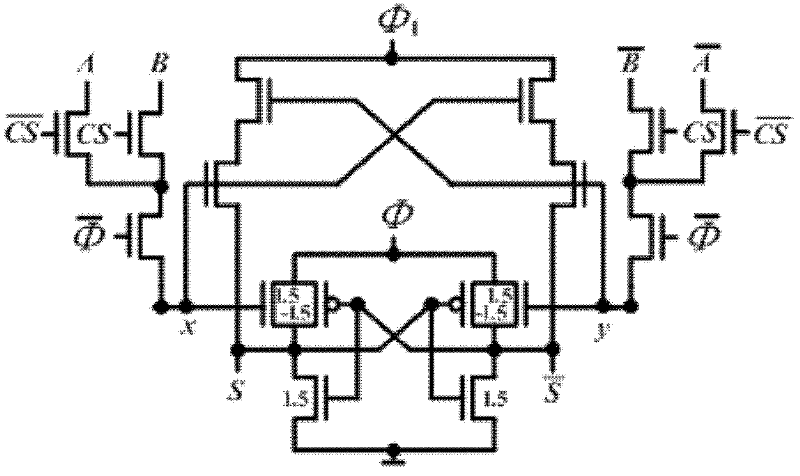

A three-value adiabatic d flip-flop and four-digit three-value adiabatic synchronous reversible counter

InactiveCN102291120AImprove space utilizationImprove time utilizationCounting chain synchronous pulse countersEngineeringEnergy recovery

The invention discloses a ternary heat insulation D trigger and a four-bit ternary heat insulation synchronous reversible counter, wherein the ternary heat insulation D trigger realizes corresponding circuits by taking the three elements theory of the circuit as guidance, combining with the three elements theory of the circuit and utilizing an NMOS (N-mental-oxide-semiconductor) transistor and a cross storage type structure with different threshold values; and the four-bit ternary heat insulation synchronous reversible counter realizes processing of a ternary signal by introducing the energy recovery theory of the heat insulation circuit, being based on the design principal of the a synchronous counter, coordinately using the ternary heat insulation D trigger, a ternary heat insulation reverse circulation gate, a ternary heat insulation reverse circulation circuit with a borrow function and a ternary heat insulation one-out-of-two data selector, adopting a two-phase power clock and utilizing a bootstrapping operated MOS (metal-oxide semiconductor) pipe with different threshold values to finish injecting and recovering the energy output by the circuit. The ternary heat insulation D trigger and the four-bit ternary heat insulation synchronous reversible counter have the advantages that the connection lines between the circuits are reduced, the chip area is saved, the packaging intensity of the integrated circuit is increased, the circuit power consumption is effectively reduced, and the average power consumption can be reduced to 67.5% compared with the traditional CMOS (complementary metal-oxide-semiconductor) synchronous reversible counter.

Owner:HANGZHOU MAEN TECH

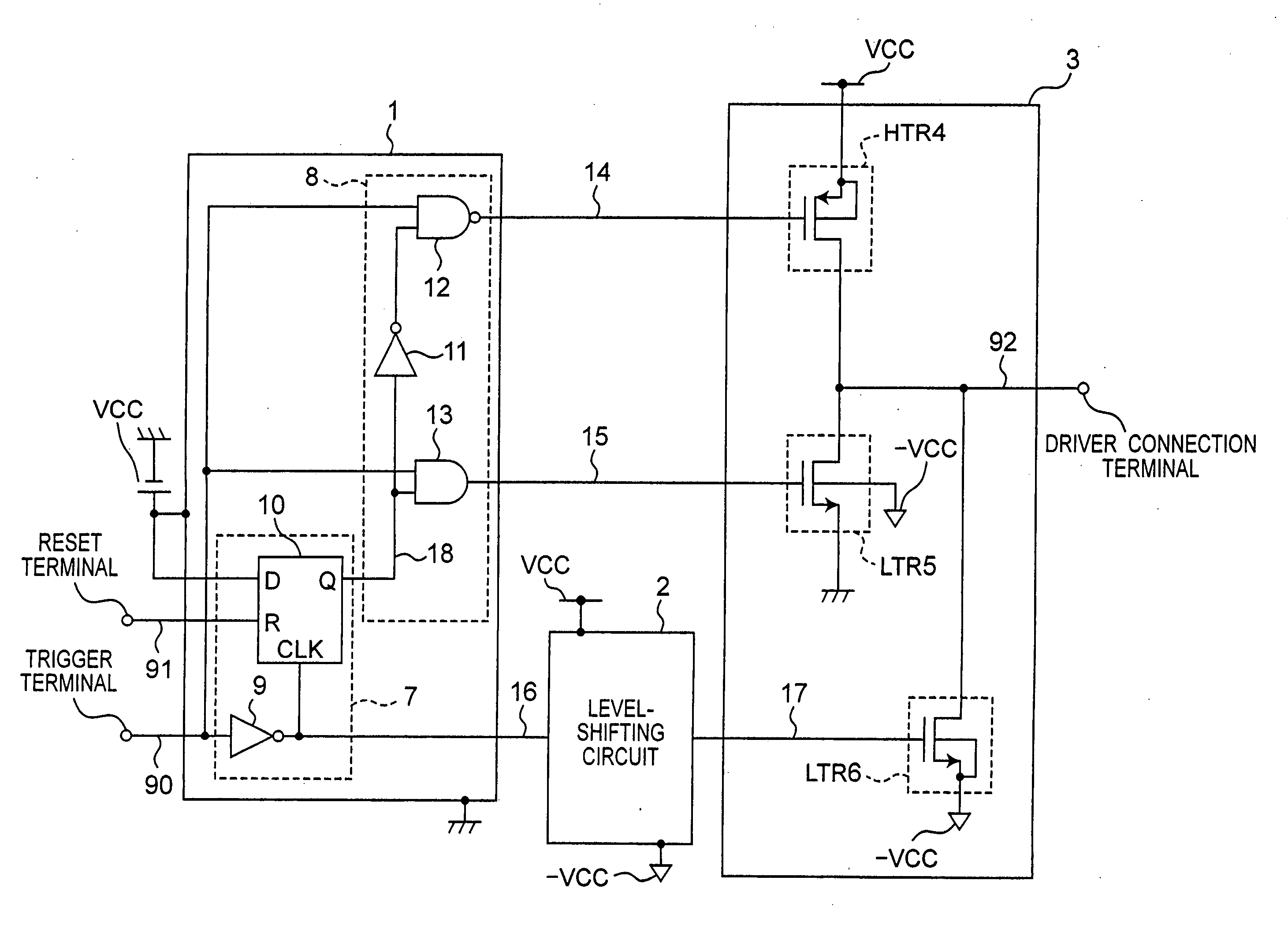

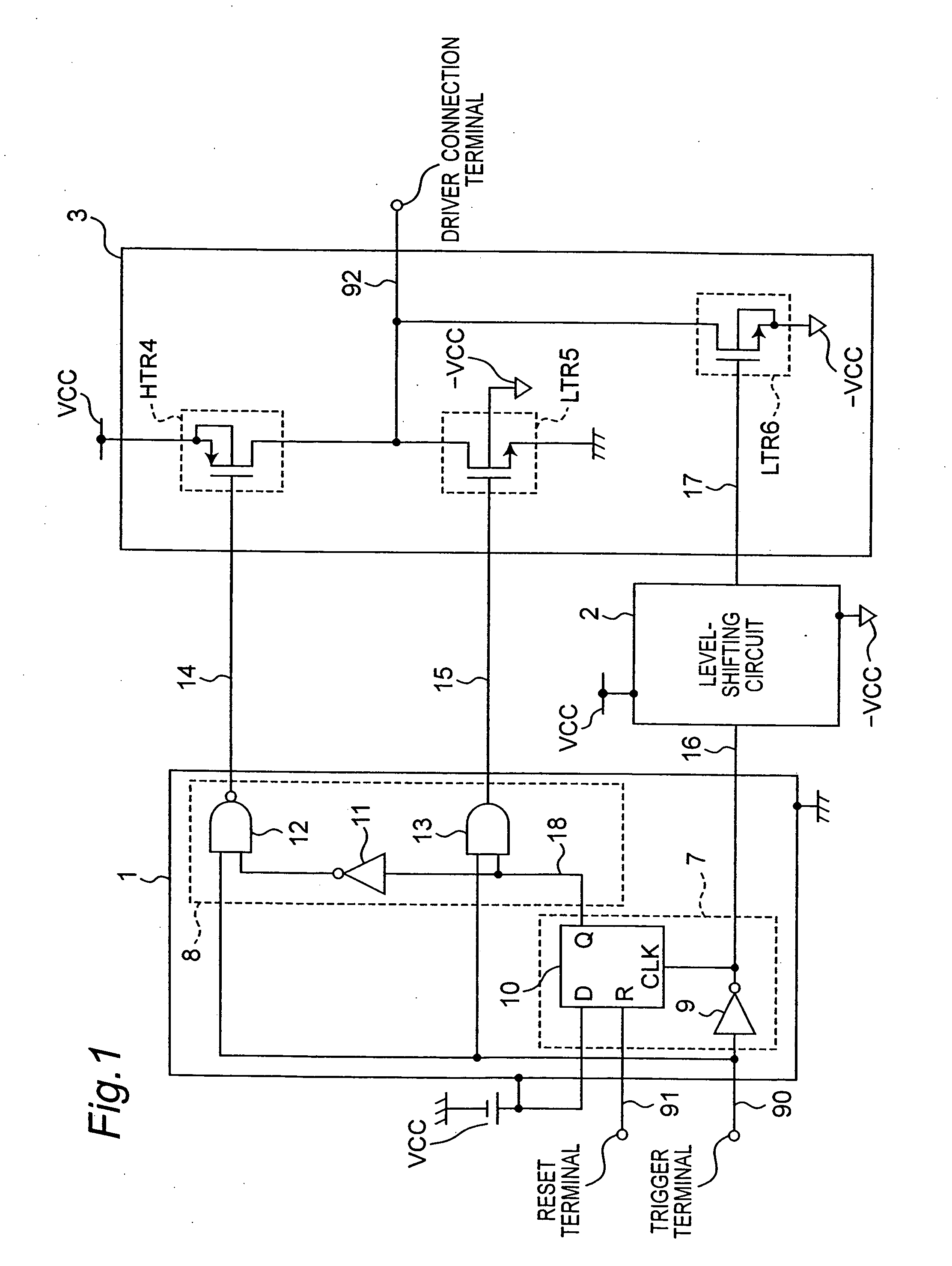

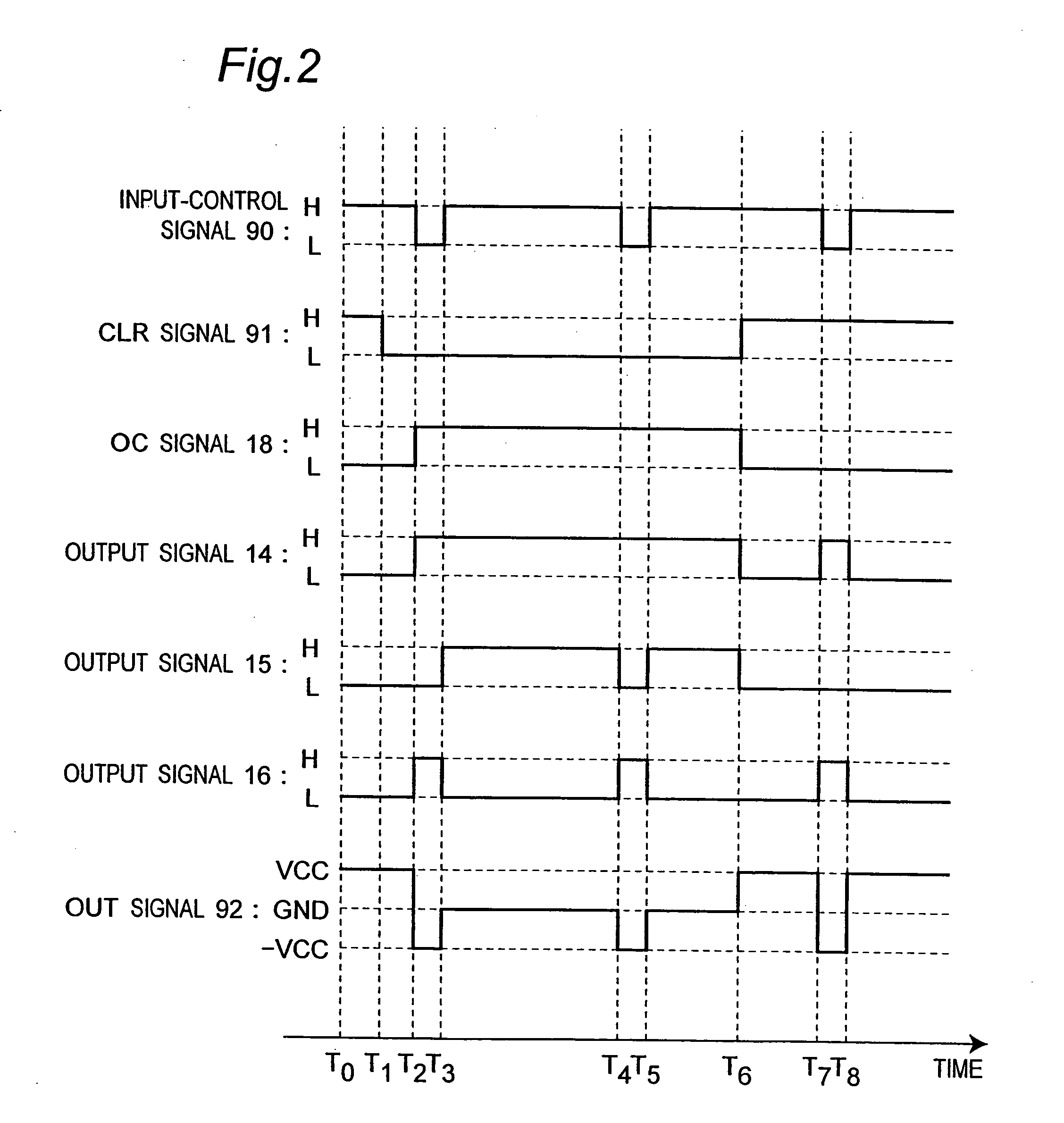

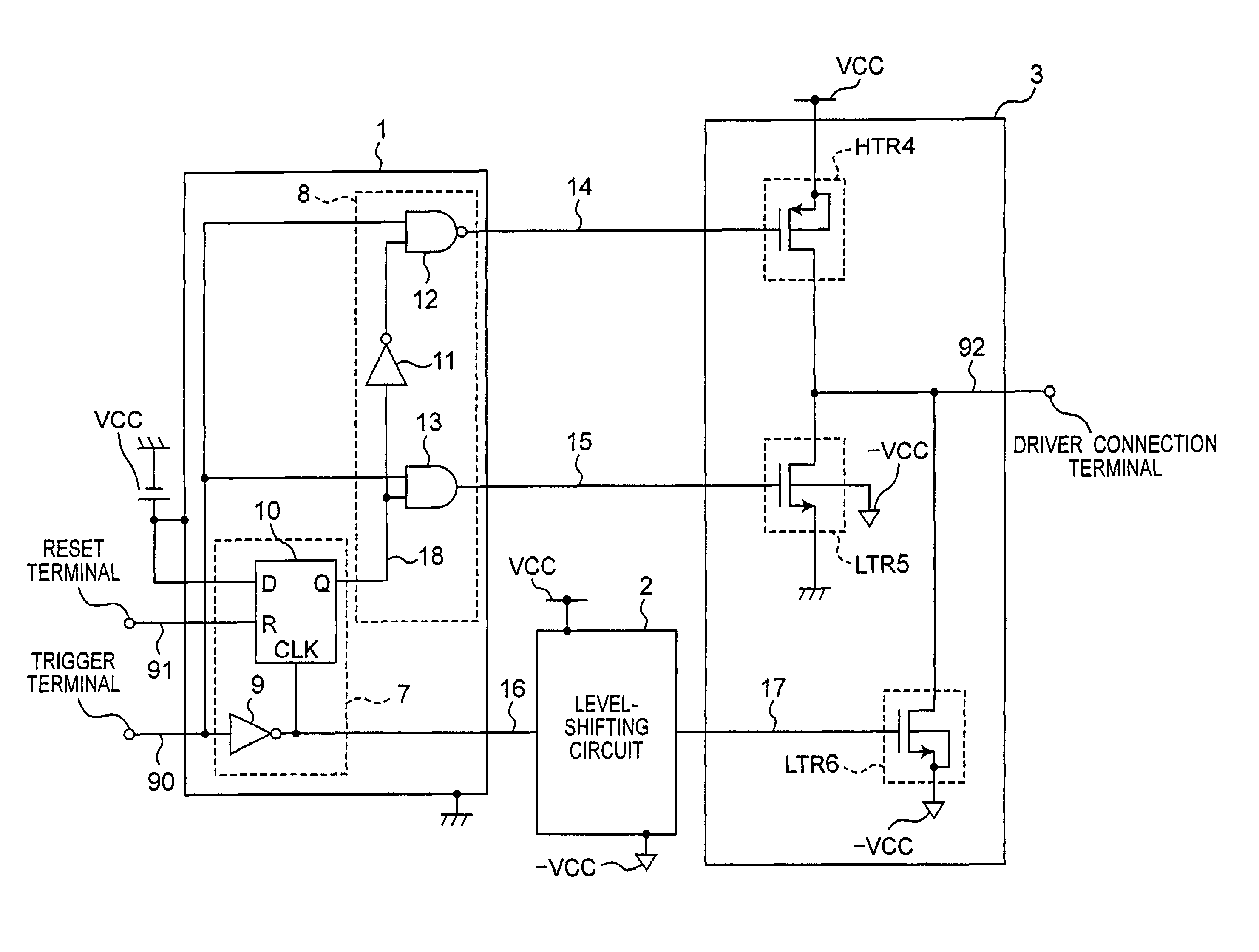

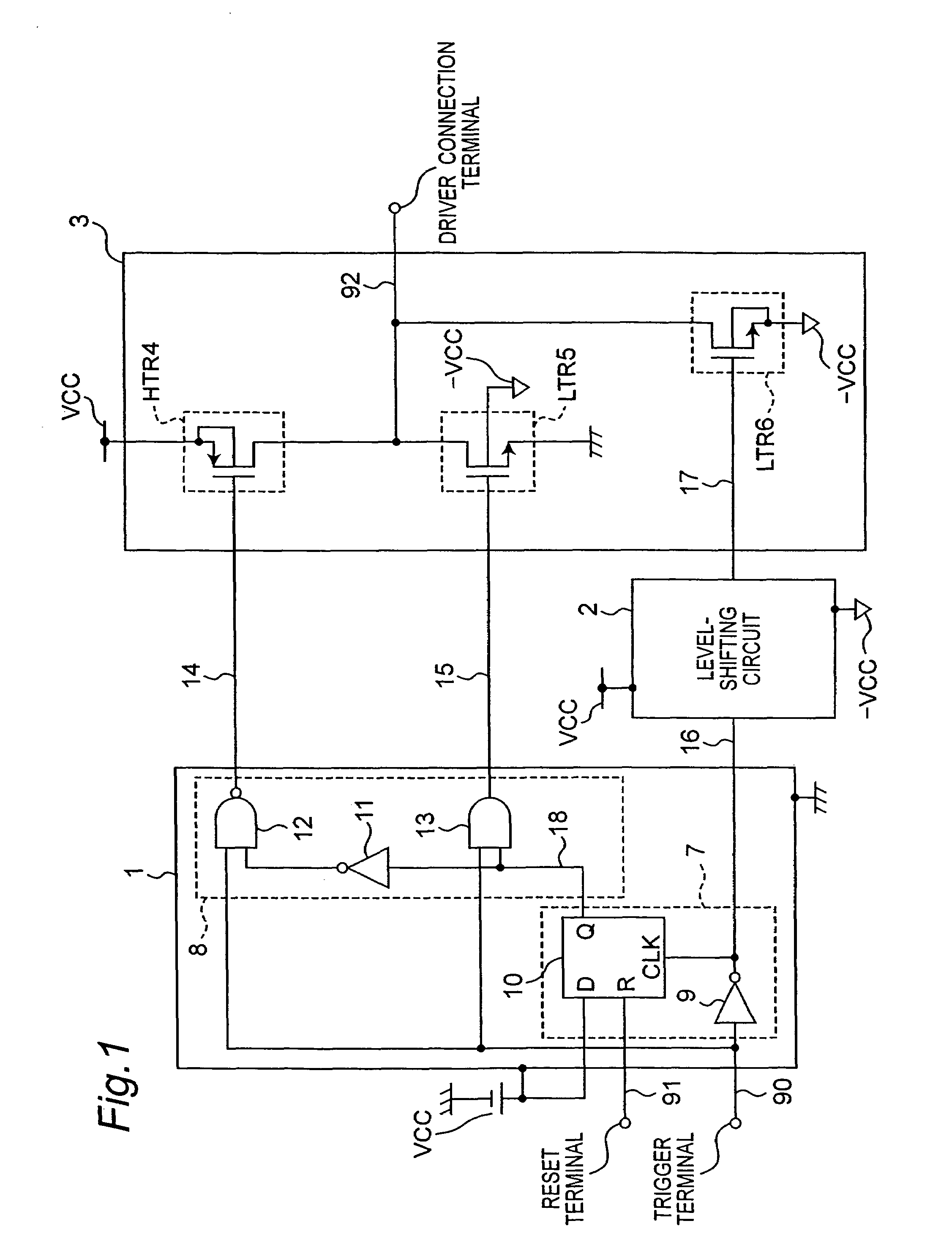

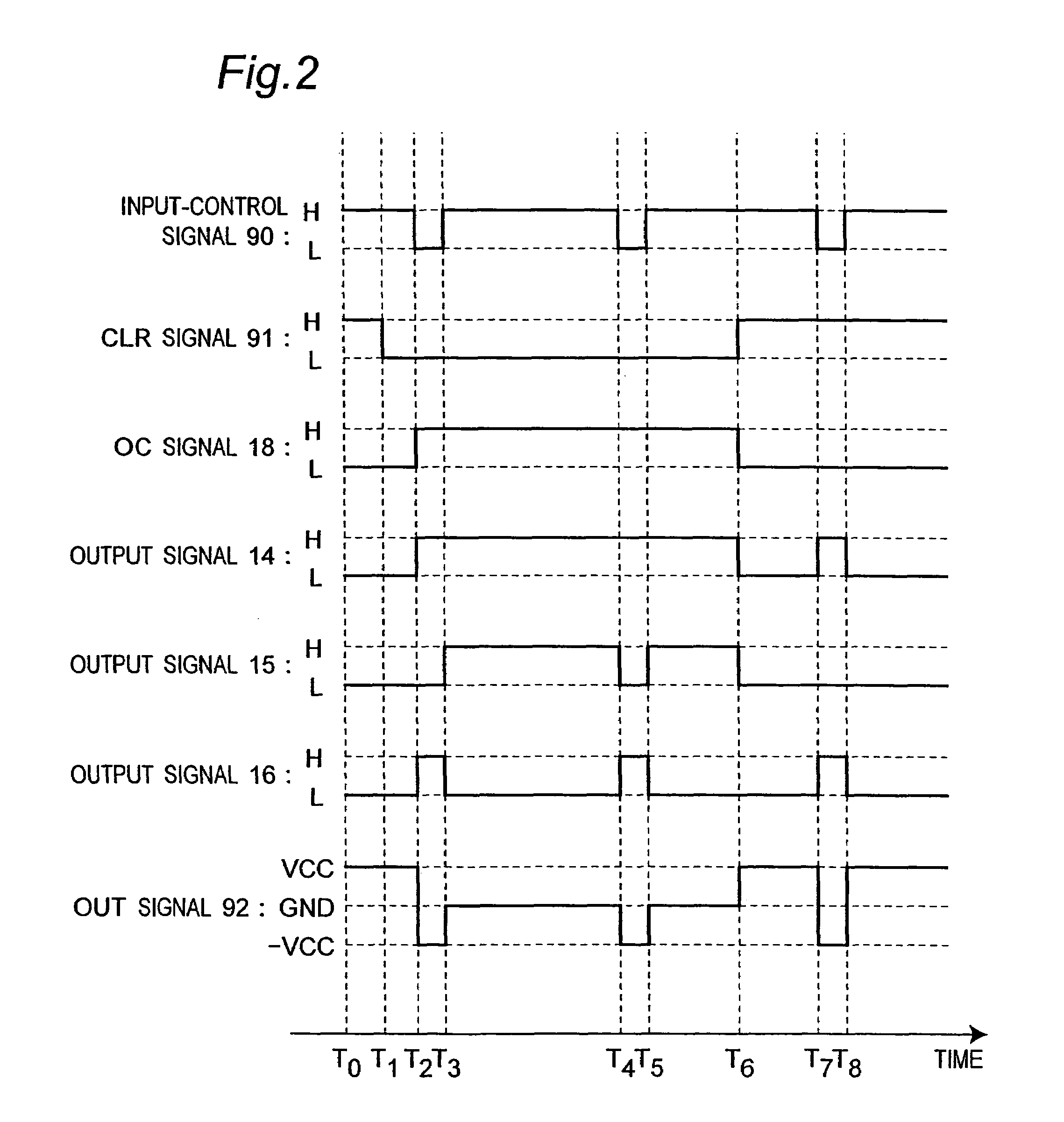

Circuit for generating ternary signal

InactiveUS20060119389A1Low costMiniaturizationElectronic switchingElectric pulse generator circuitsControl signalInput control

Owner:COLLABO INNOVATIONS INC

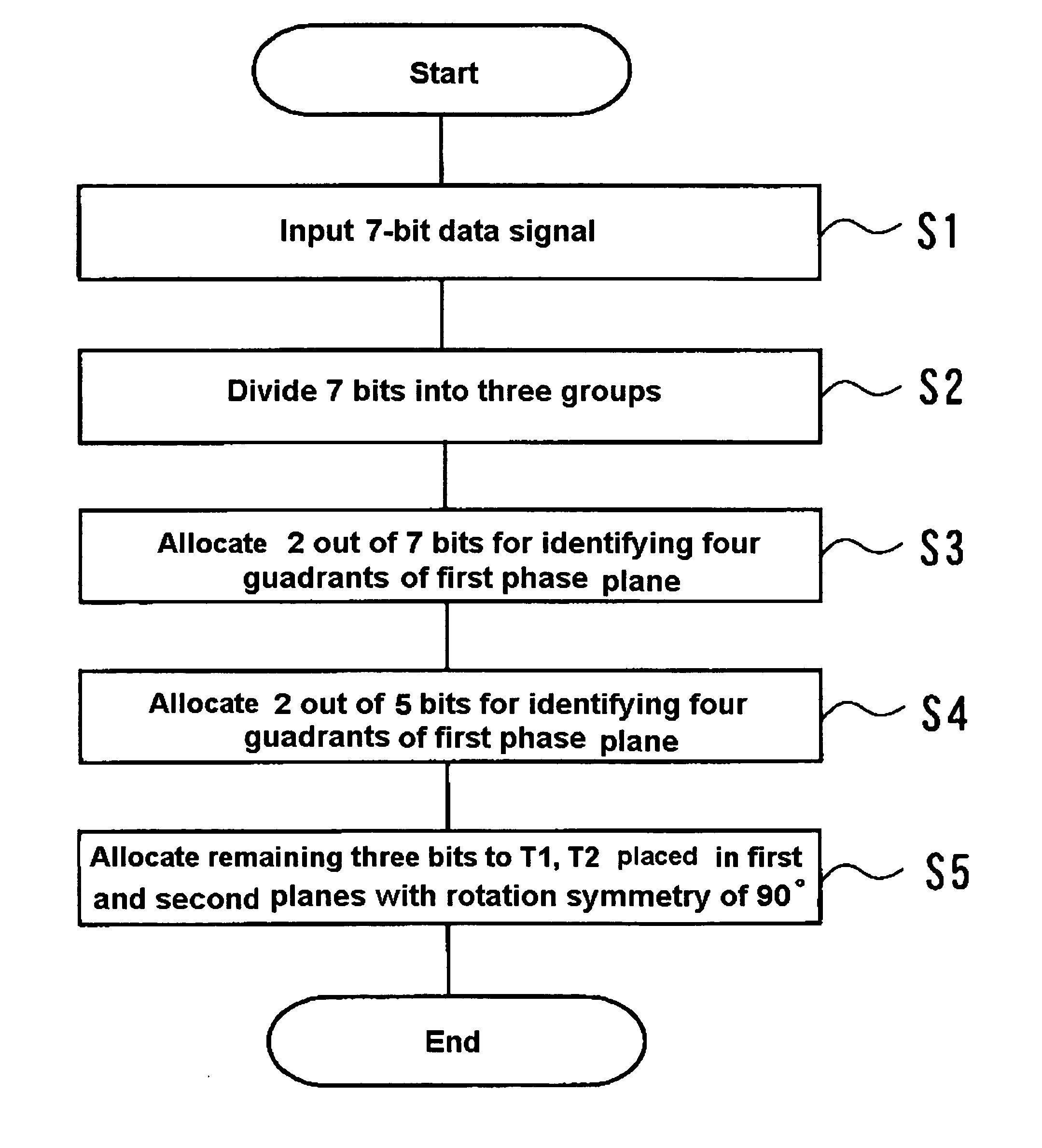

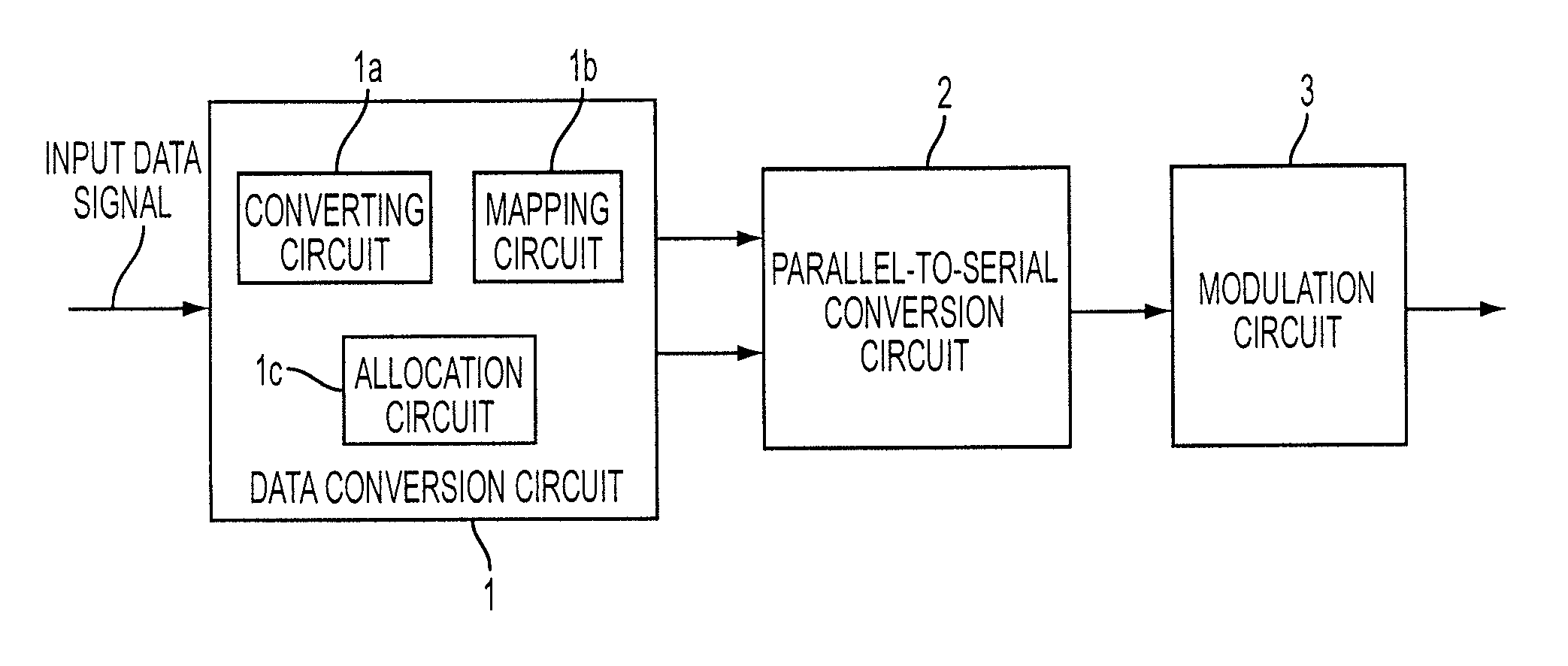

Multi-level modulation method and system

InactiveUS20050201479A1Minimizes error against symbol errorError minimizationPhase-modulated carrier systemsMultiple carrier systemsFour quadrantsEngineering

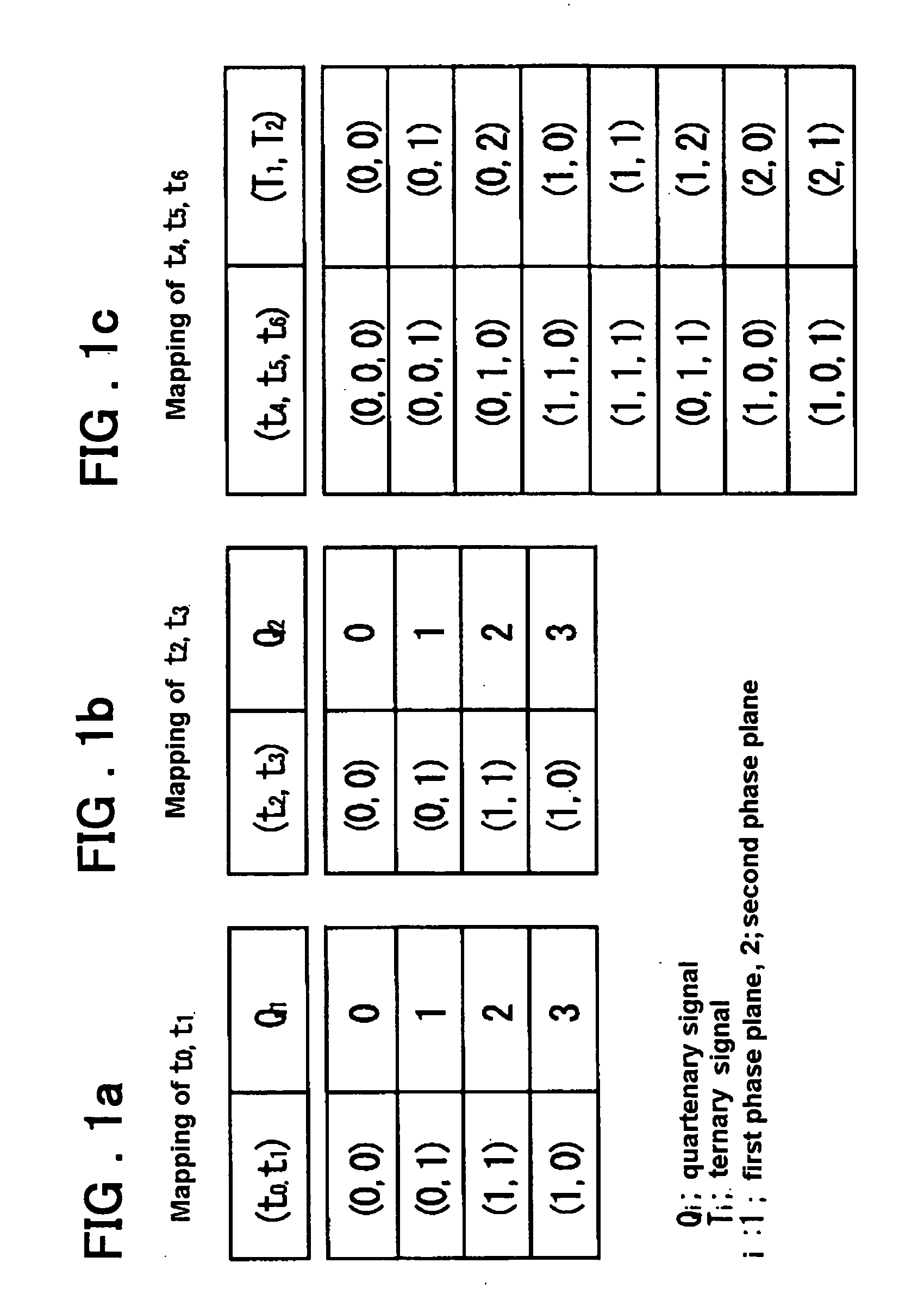

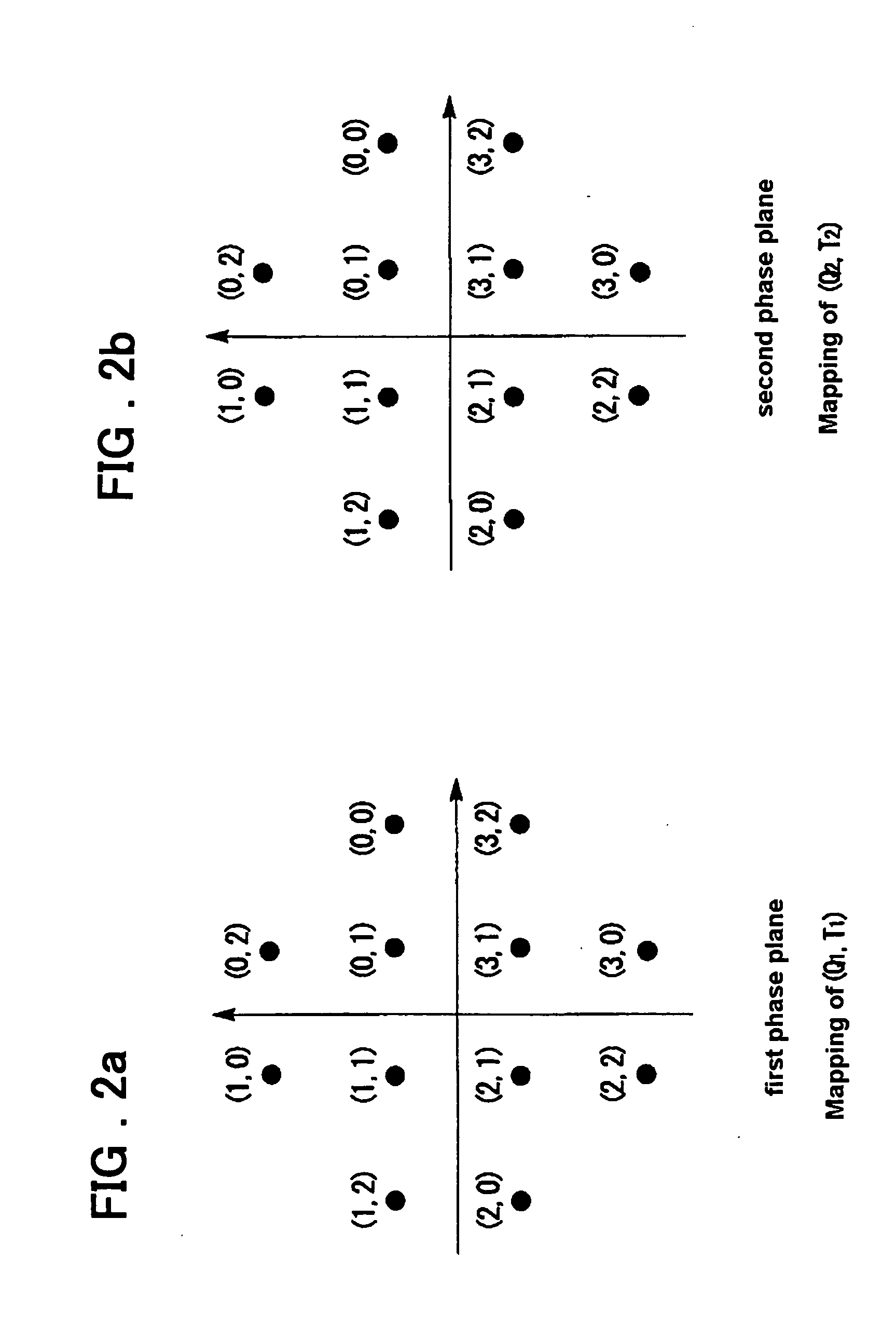

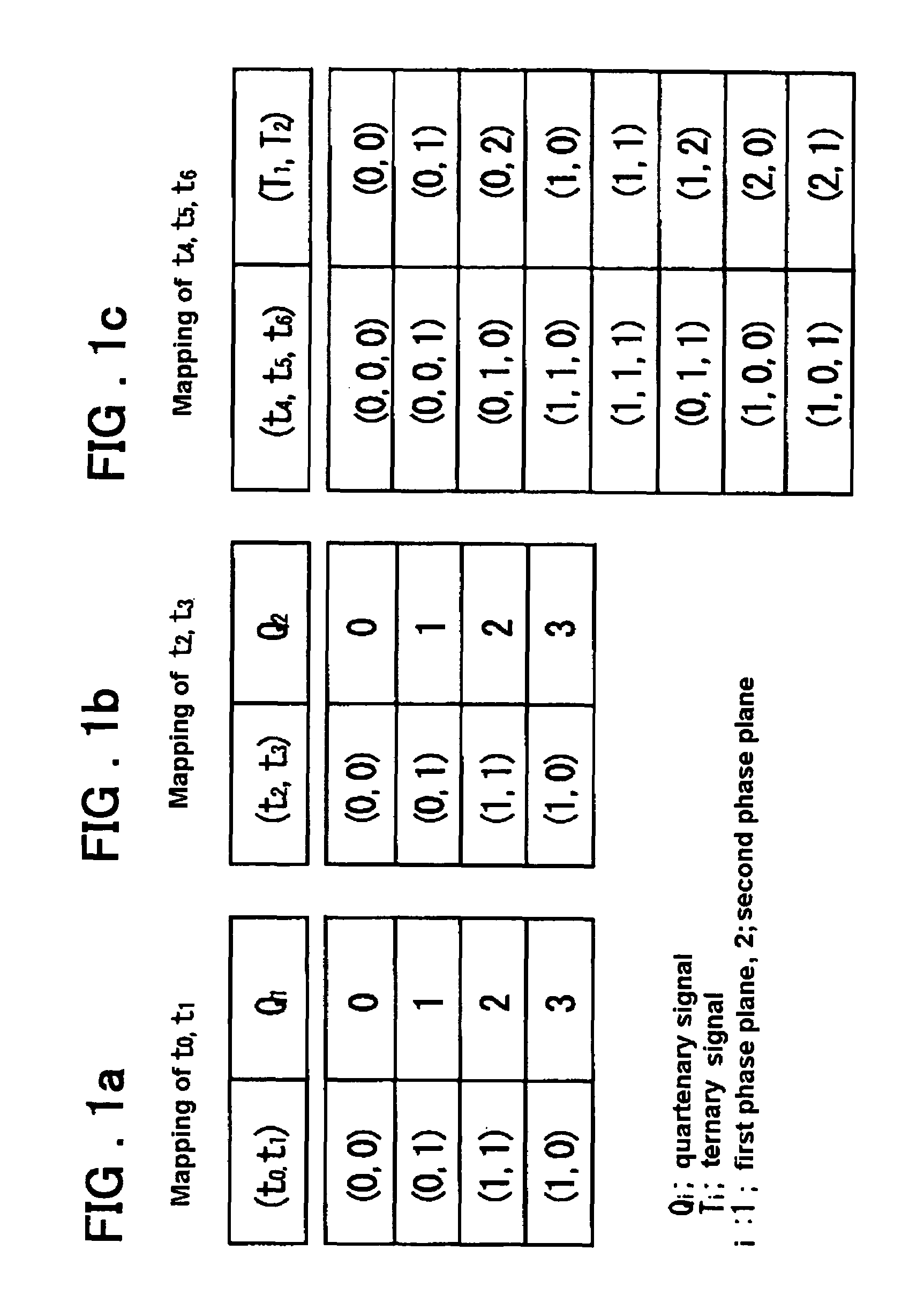

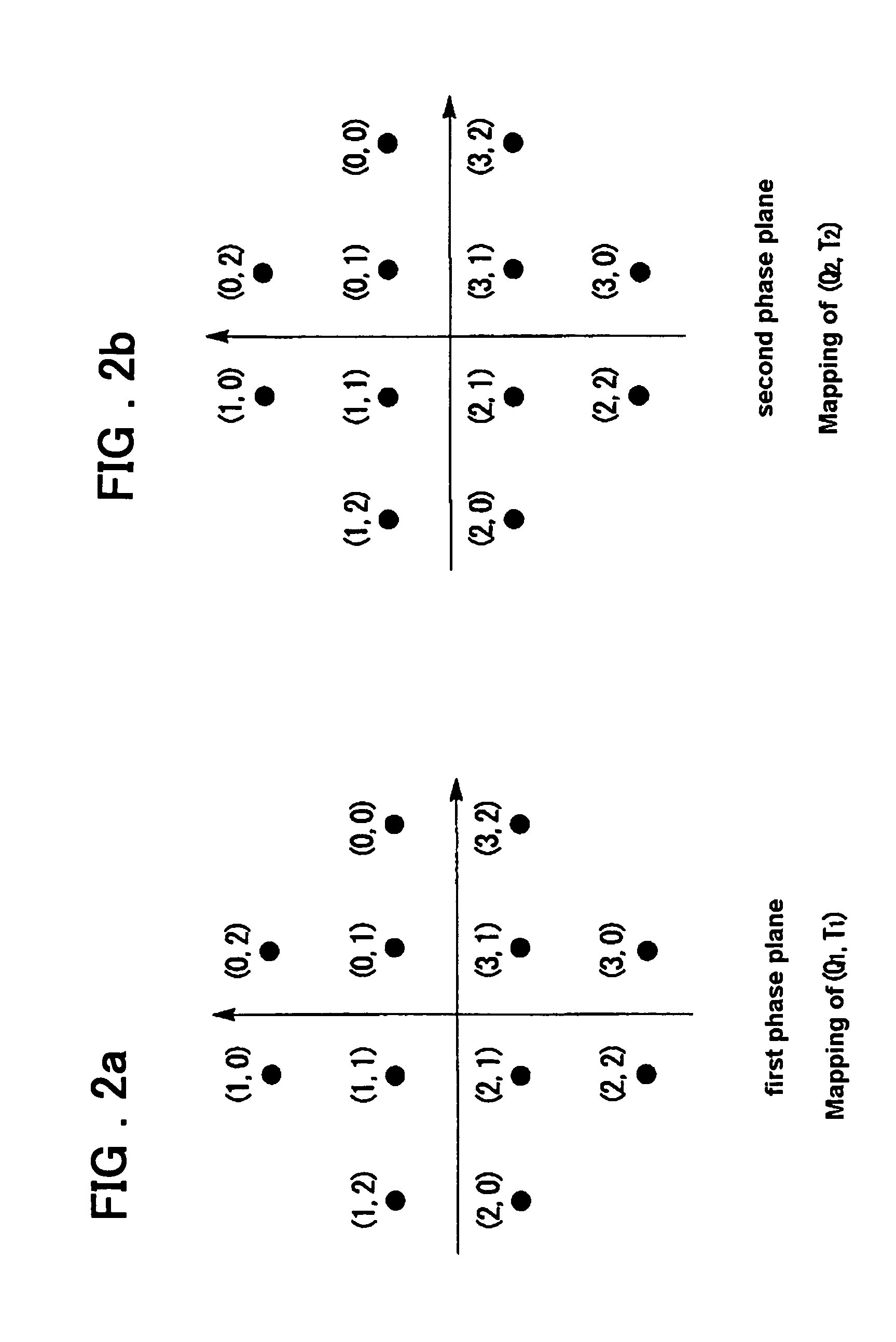

Disclosed is a method and a system for performing N-ary modulation in which bit errors may be reduced against symbol error. A binary signal, a bit length thereof being n, is associated with N-ary signals arranged in first and second phase planes respectively for transmission, wherein N is not a number belonging to powers of 2 but is a number belonging to a series beginning from 12 and sequentially doubled, that is, any one of 12, 24, 48, 96, . . . , and wherein n is such that, if the bit length n is 7, 9, 11, 13, . . . , the number N is 12, 24, 48, 96, . . . , respectively, two out of the n bits are allocated for identifying four quadrants of the first phase plane, two out of the remaining (n−2) bits are allocated for identifying four quadrants of the second phase plane. The binary signal of three out of the n bits is converted into two digits of ternary signals (T1, T2). The ternary signals are mapped to the first and second phase planes with rotational symmetry of 90° or with axial symmetry.

Owner:NEC CORP

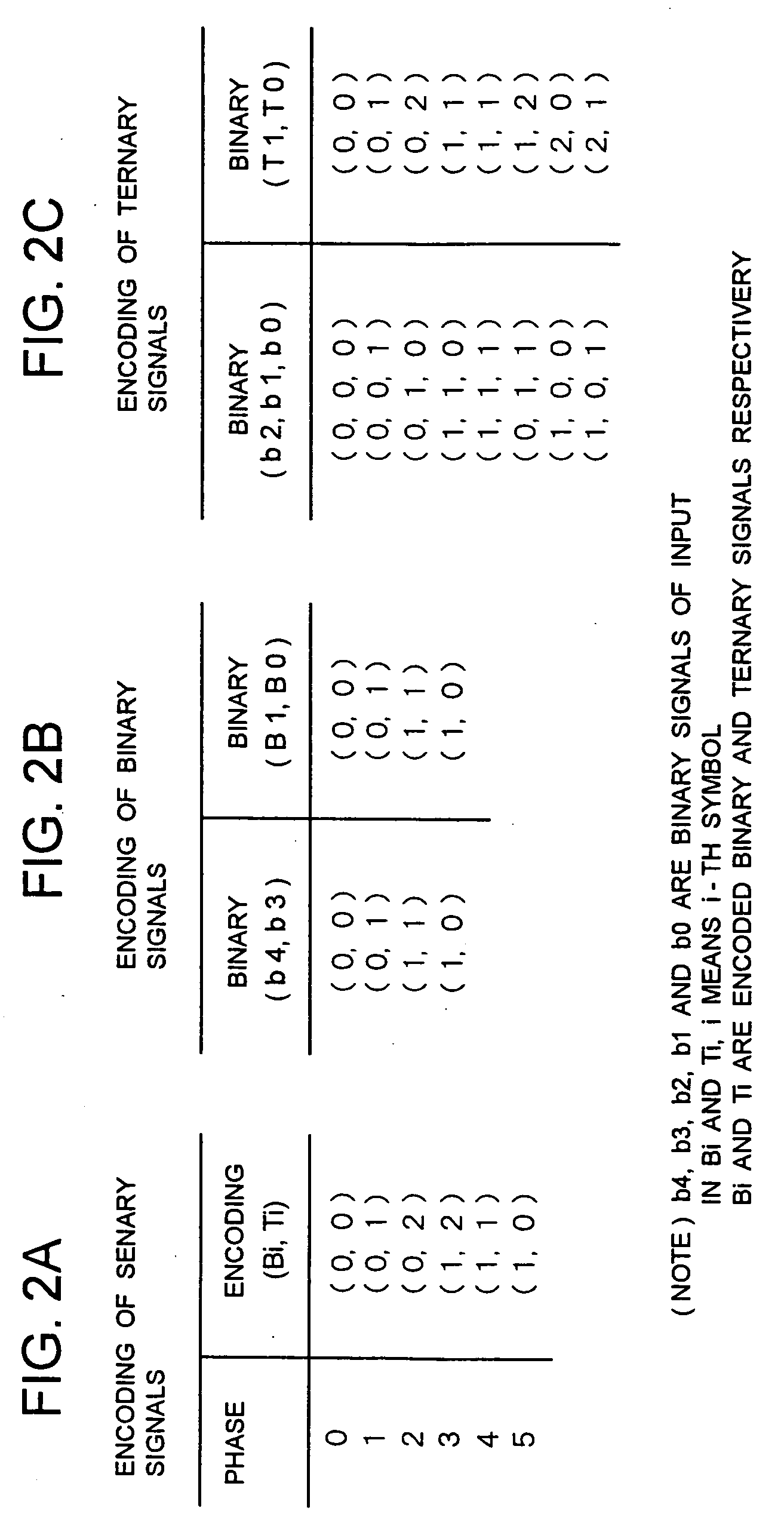

Modulation and demodulation system, modulator, demodulator and phase modulation method and phase demodulation method used therefor

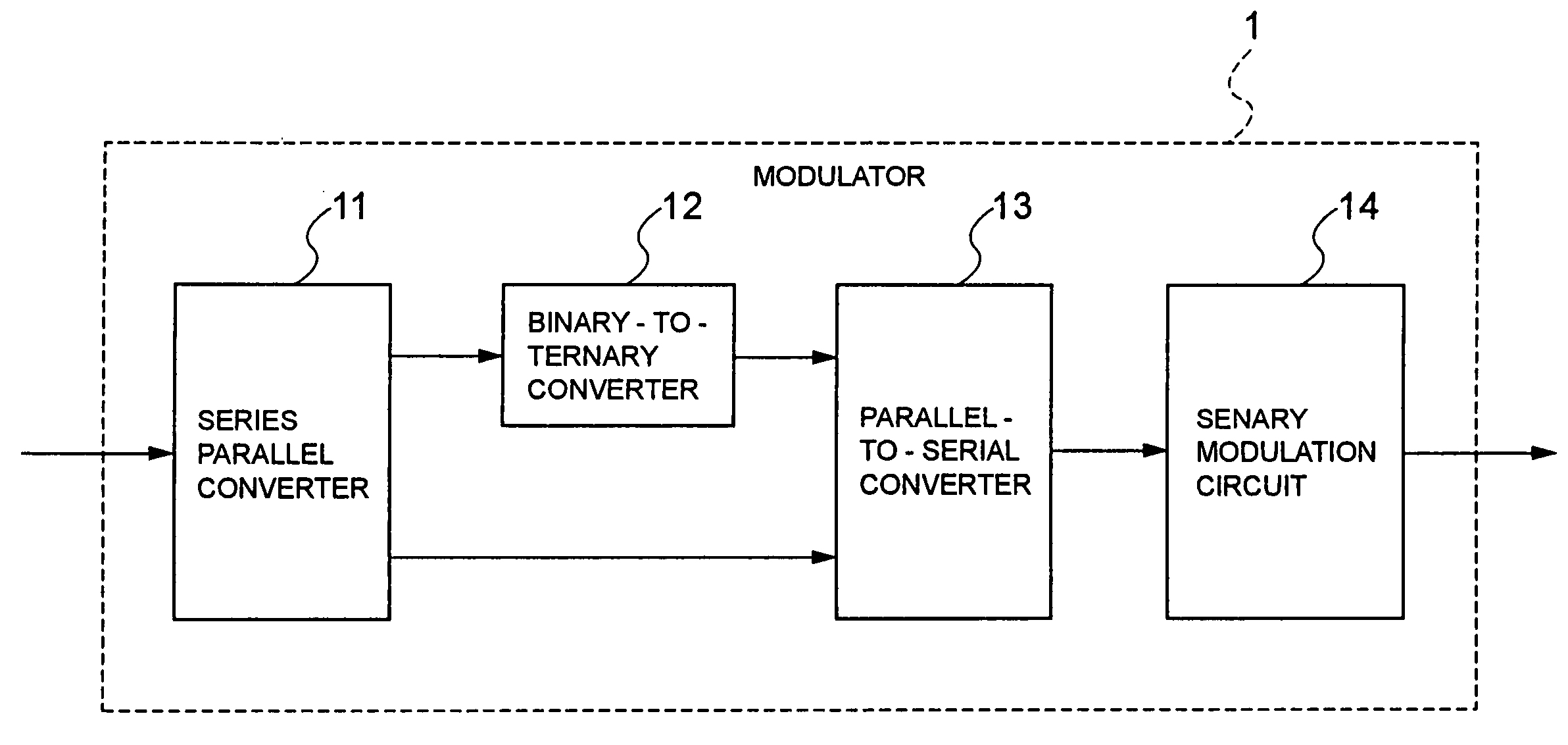

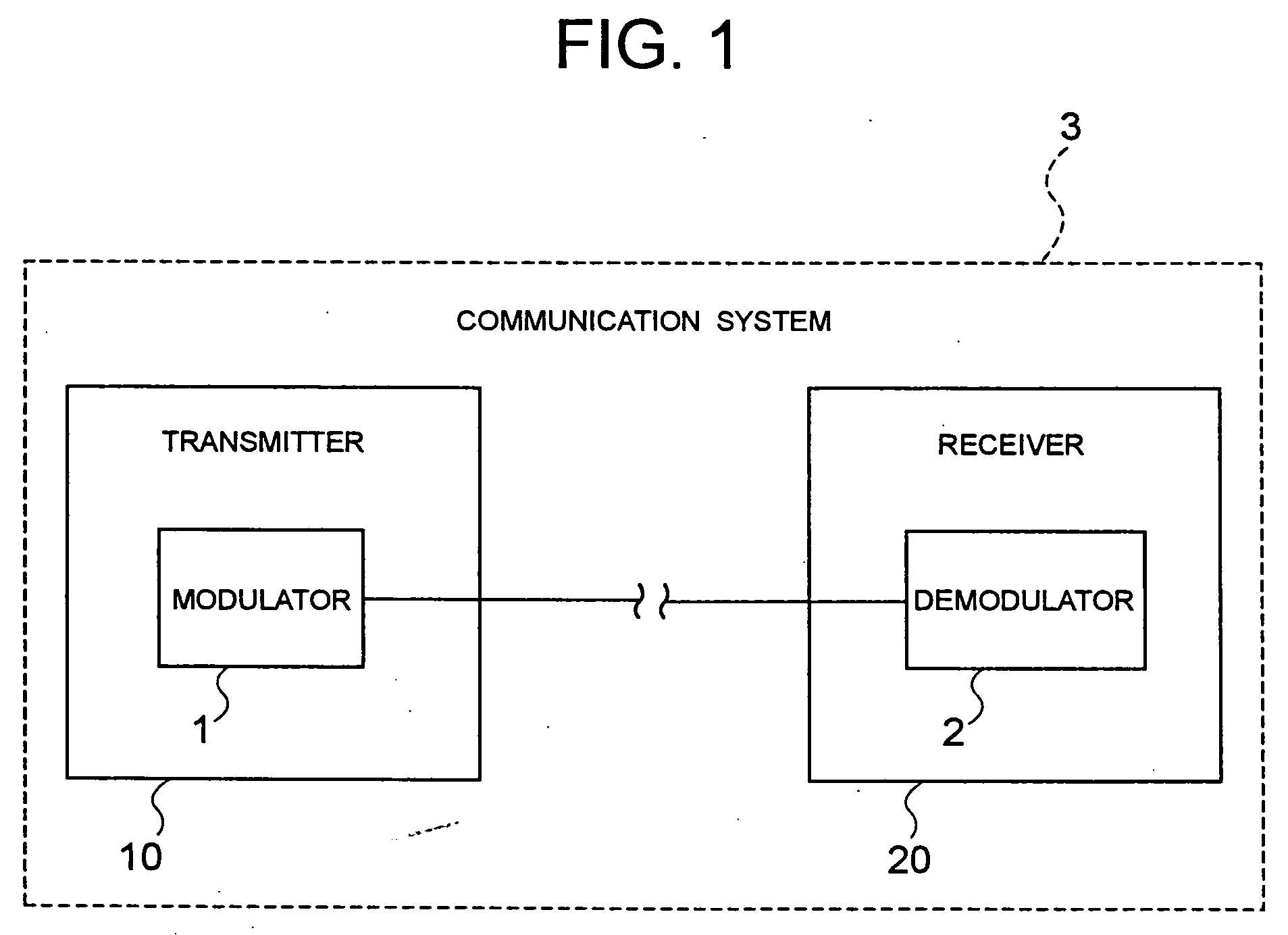

InactiveUS20060088127A1Minimizes bit error rateSimple circuit configurationAngle modulationFrequency-modulated carrier systemsPhase modulationTernary signal

The present invention provides a modulation and demodulation system capable of minimizing a bit error rate in a six-phase phase modulation method. A senary signal phase-modulated and outputted by a modulator of a first embodiment is received and phase-modulated by a destination demodulator to a binary signal before conversion by the modulator. The modulator assigns (0, 0), (0, 1), (0, 2), (1, 2), (1, 1) and (1, 0) which are senary signals (bi, ti) to first to sixth phases respectively. The demodulator performs a conversion process from the senary signals to the binary signals, for instance, by storing transmitted senary signals and sequentially converting every senary signal of length m to binary signal of length b so as to output them. The process of the demodulator assigns the first to sixth phases as the senary signals (bi, ti) to (0, 0), (0, 1), (0, 2), (1, 2), (1, 1) and (1, 0) respectively. The modulator of a second embodiment assigns (0, 0), (0, 1), (0, 2), (1, 2), (1, 1) and (1, 0) to the first to sixth phases respectively by having the senary signals expressed as (Bi, Ti) with i=1 as a first symbol, i=2 as a second symbol, the binary signal as Bi and ternary signal as Ti. The demodulator performs a conversion process from the senary signals to the binary signals, for instance, by storing the transmitted senary signals and sequentially converting every 2 pieces of them to 5 pieces of binary signal so as to output them. The process of the demodulator assigns the first to sixth phases as the senary signals (Bi, Ti) to (0, 0), (0, 1), (0, 2), (1, 2), (1, 1) and (1, 0) respectively.

Owner:NEC CORP

Read channel circuit and method for decoding using reduced-complexity error correction

A decoding technique is disclosed for proving inexpensively a read channel circuit which has an error correction function and is applicable to high channel frequencies. In this read channel circuit, generating a reference slice level signal and a plurality of slice level signals which are different from the reference slice level signal, converting the playback signal into a plurality of binary signals synchronized with a channel clock according to each of the slice level signals, selecting two binary signals, measuring the phase distance between the two binary signals, judging the polarity of an inverted edge of a reference binary signal, and generating an error correction signal on the basis of the phase distance and the polarity of the inverted edge of the reference binary signal, whereby any error in the playback signal can be eliminated.

Owner:KK TOSHIBA

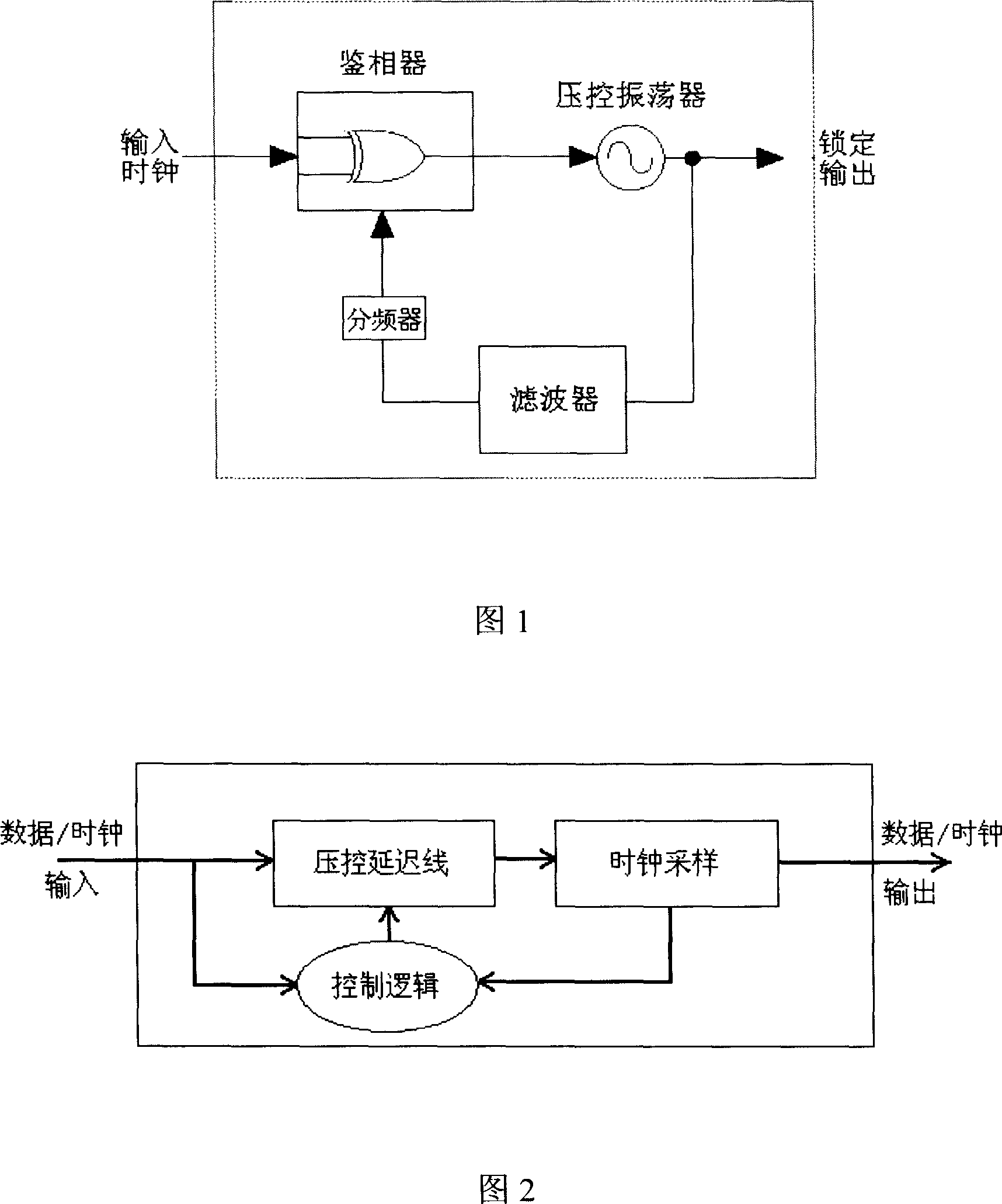

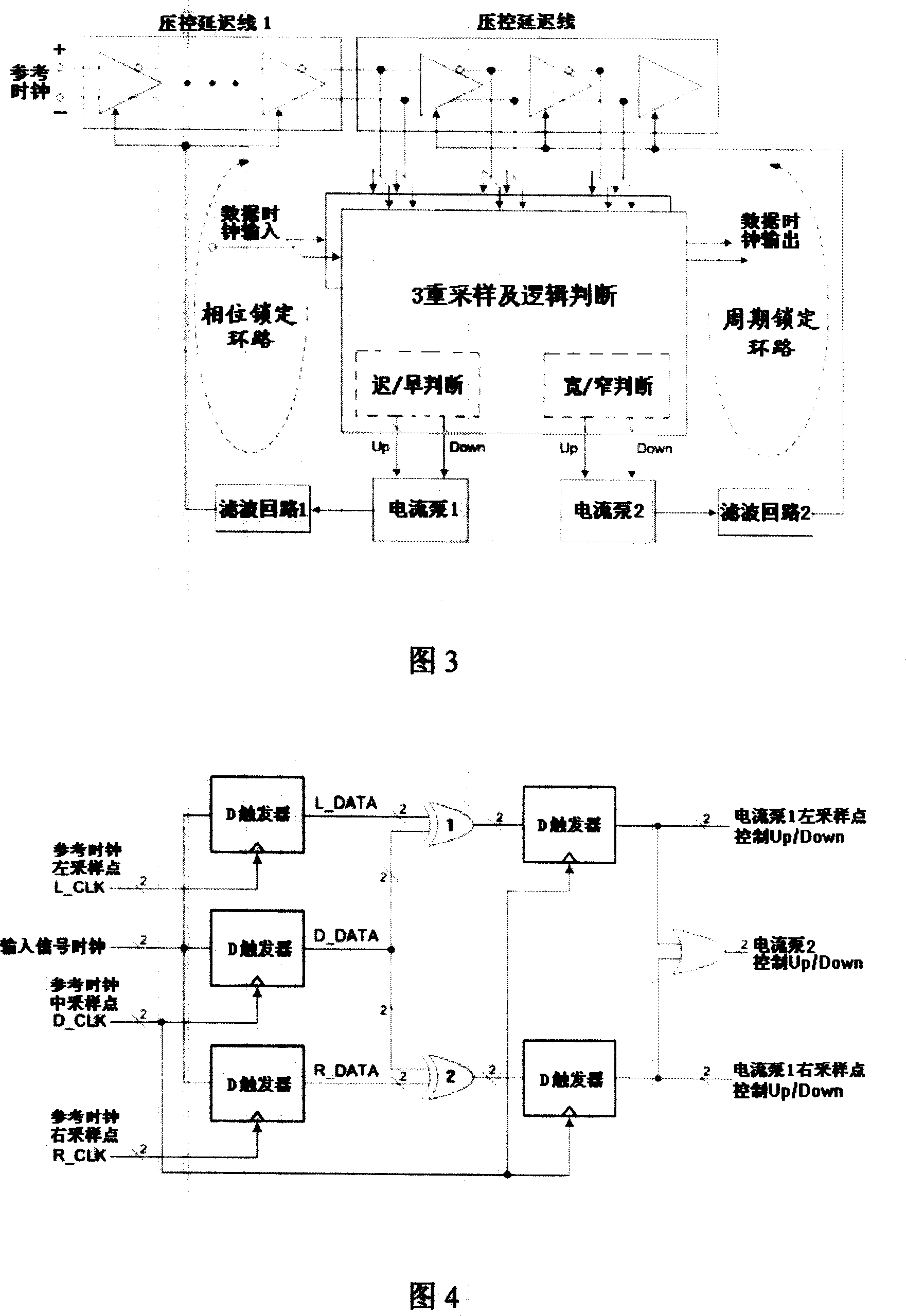

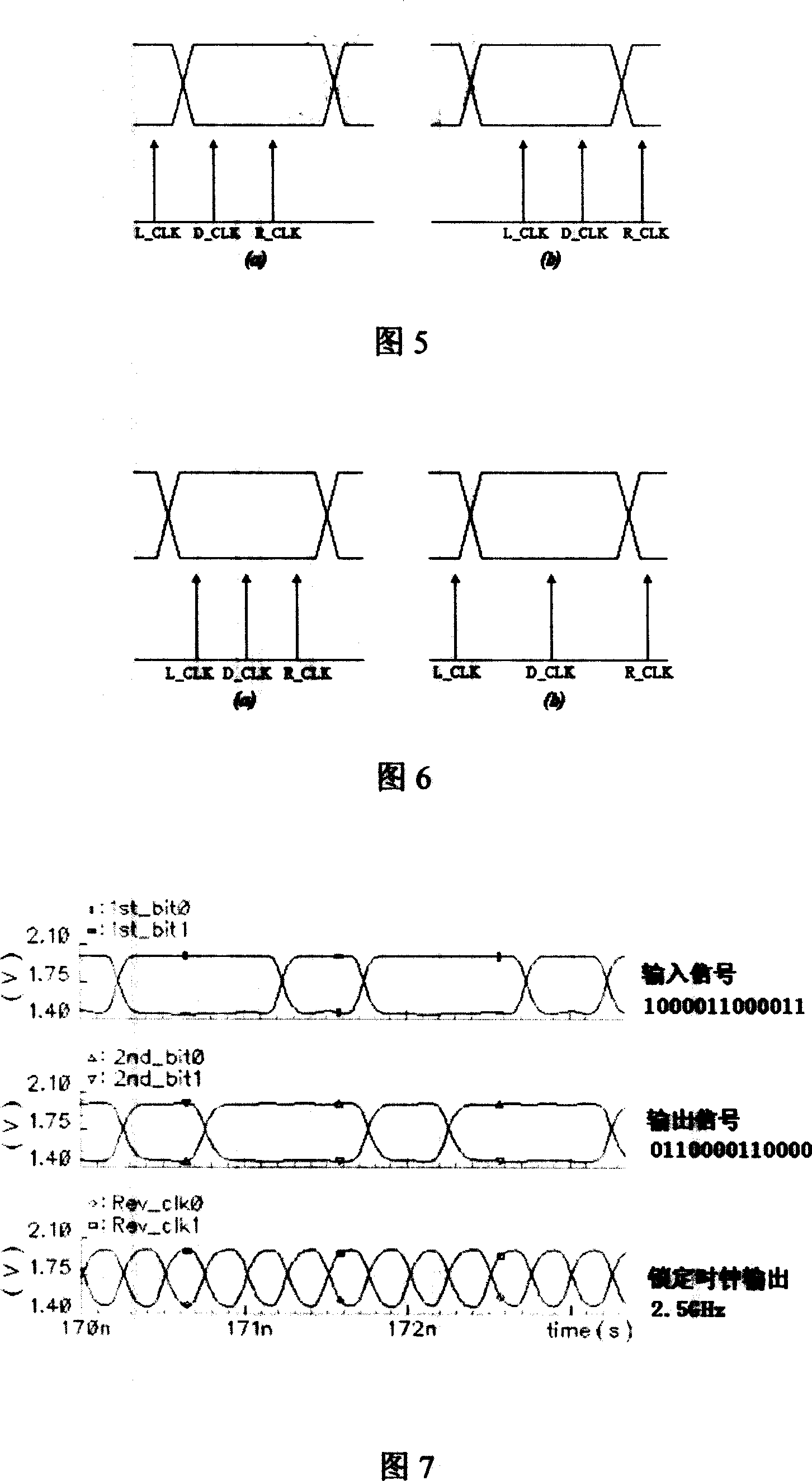

Time-delay locking loop

ActiveCN1983815AHigh logic control accuracyShort response timePulse automatic controlSignal qualityTime delays

The invention is concerned with the delay time locking loop circuit, it is higher logical control accuracy and faster response characteristic, and restrains the effect leading by the power fluctuation and the molestation from the transmission line. It is: inserts the independent double-loop (the signal phase locking loop and the signal cycle locking loop) sample loop structure in the signal path, uses the ternary signal sample method to process phase (the earlier or later logical judgment) sample / text and signal cycle (the narrow or width logic judgment) sample / text for the clock / data signal, changes the phase and space between the ternary sample points by the voltage controlling delay line if the judgment exists deviation, processes sample of the signal phase and cycle again until lock the signal phase and cycle finally.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Multi-level modulation method and system

InactiveUS7630453B2Error minimizationReducing the number of bit error against symbol errorsPhase-modulated carrier systemsMultiple carrier systemsFour quadrantsEngineering

Disclosed is a method and a system for performing N-ary modulation in which bit errors may be reduced against symbol error. A binary signal, a bit length thereof being n, is associated with N-ary signals arranged in first and second phase planes respectively for transmission, wherein N is not a number belonging to powers of 2 but is a number belonging to a series beginning from 12 and sequentially doubled, that is, any one of 12, 24, 48, 96, . . . , and wherein n is such that, if the bit length n is 7, 9, 11, 13, . . . , the number N is 12, 24, 48, 96, . . . , respectively, two out of the n bits are allocated for identifying four quadrants of the first phase plane, two out of the remaining (n−2) bits are allocated for identifying four quadrants of the second phase plane. The binary signal of three out of the n bits is converted into two digits of ternary signals (T1, T2). The ternary signals are mapped to the first and second phase planes with rotational symmetry of 90° or with axial symmetry.

Owner:NEC CORP

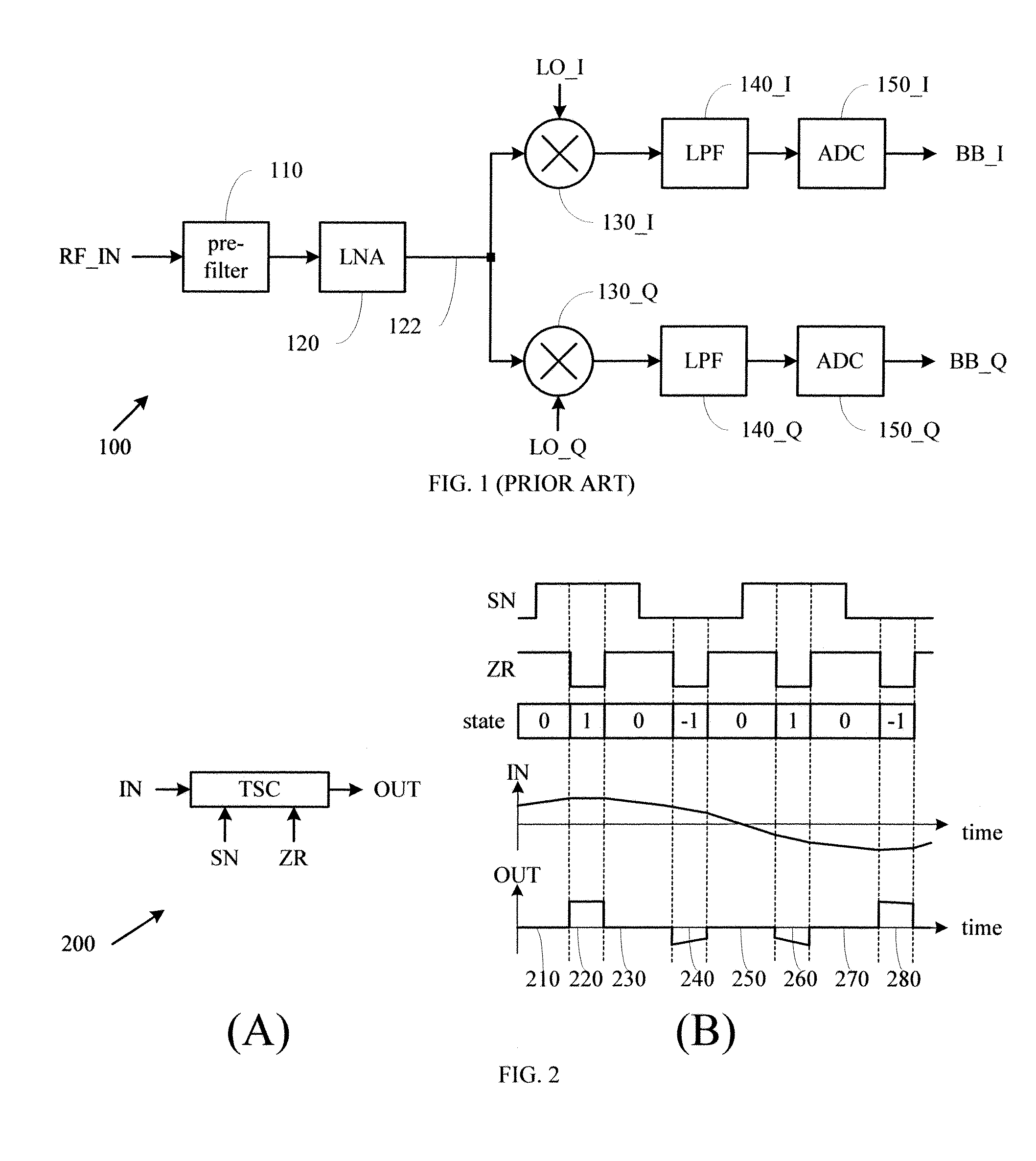

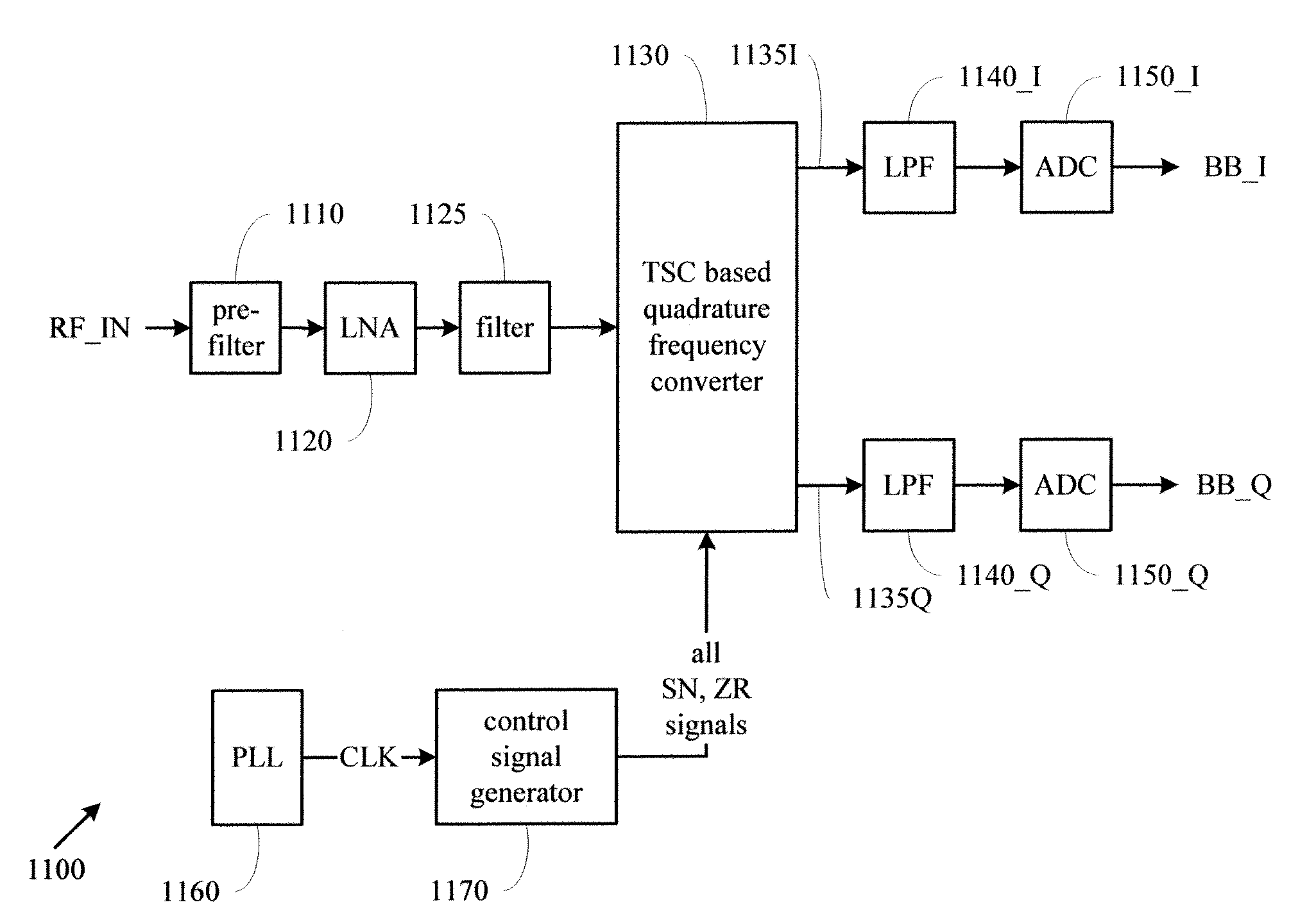

Direct conversion TV tuner and method thereof

A direct conversion method is disclosed. The method comprises: amplifying the input signal to generate an amplified signal; down-converting the amplified signal into two intermediate signals using a first set of ternary signals and a second set of ternary signals, respectively; filtering the first intermediate signal to generate a third intermediate signal; filtering the second intermediate signal to generate a fourth intermediate signal; digitizing the third intermediate signal into a first output signal in accordance with a first clock; digitizing the fourth intermediate signal into a second output signal in accordance with the first clock; and generating the first set of ternary signals and the second set of ternary signals based on a second clock.

Owner:REALTEK SEMICON CORP

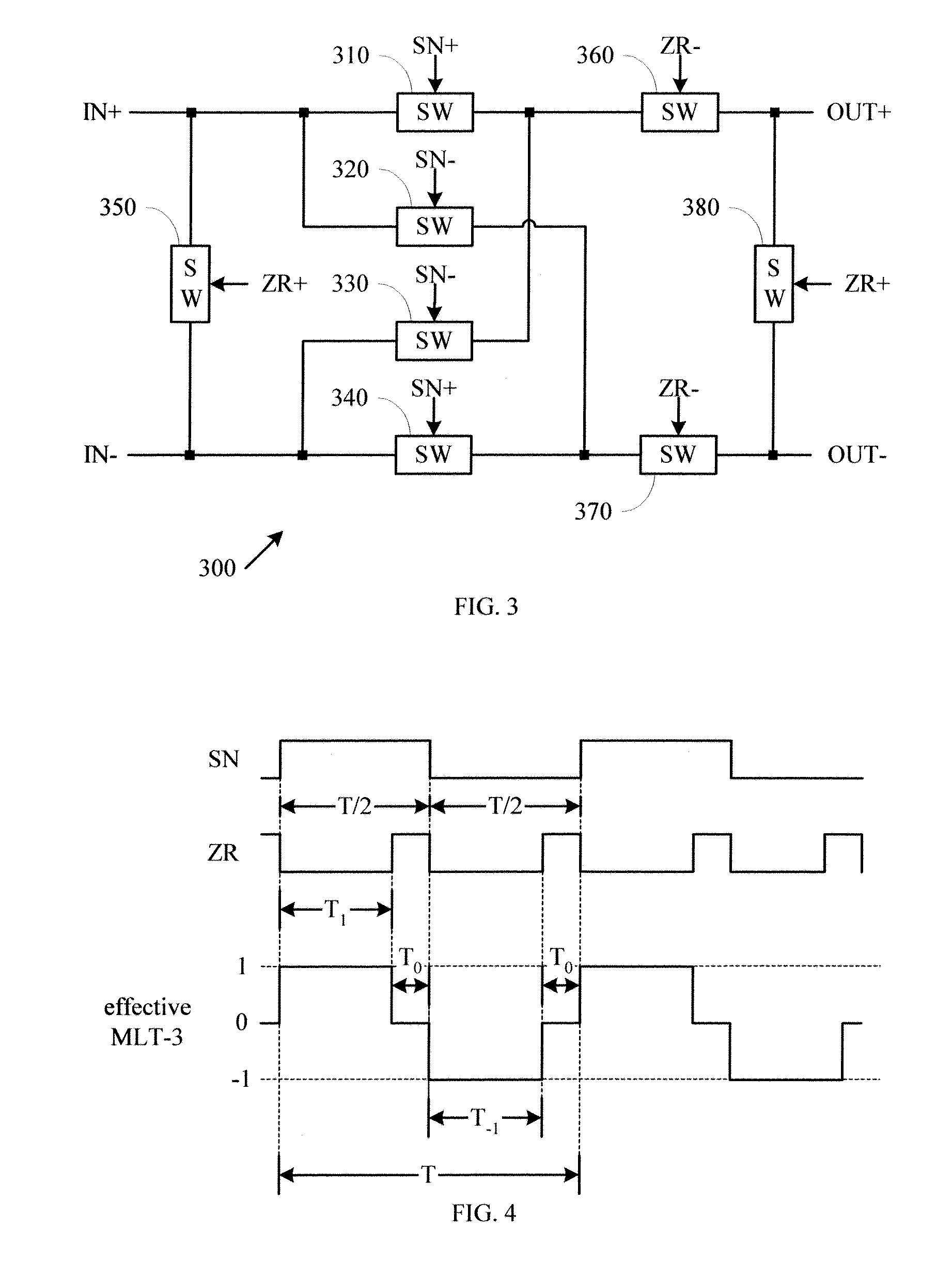

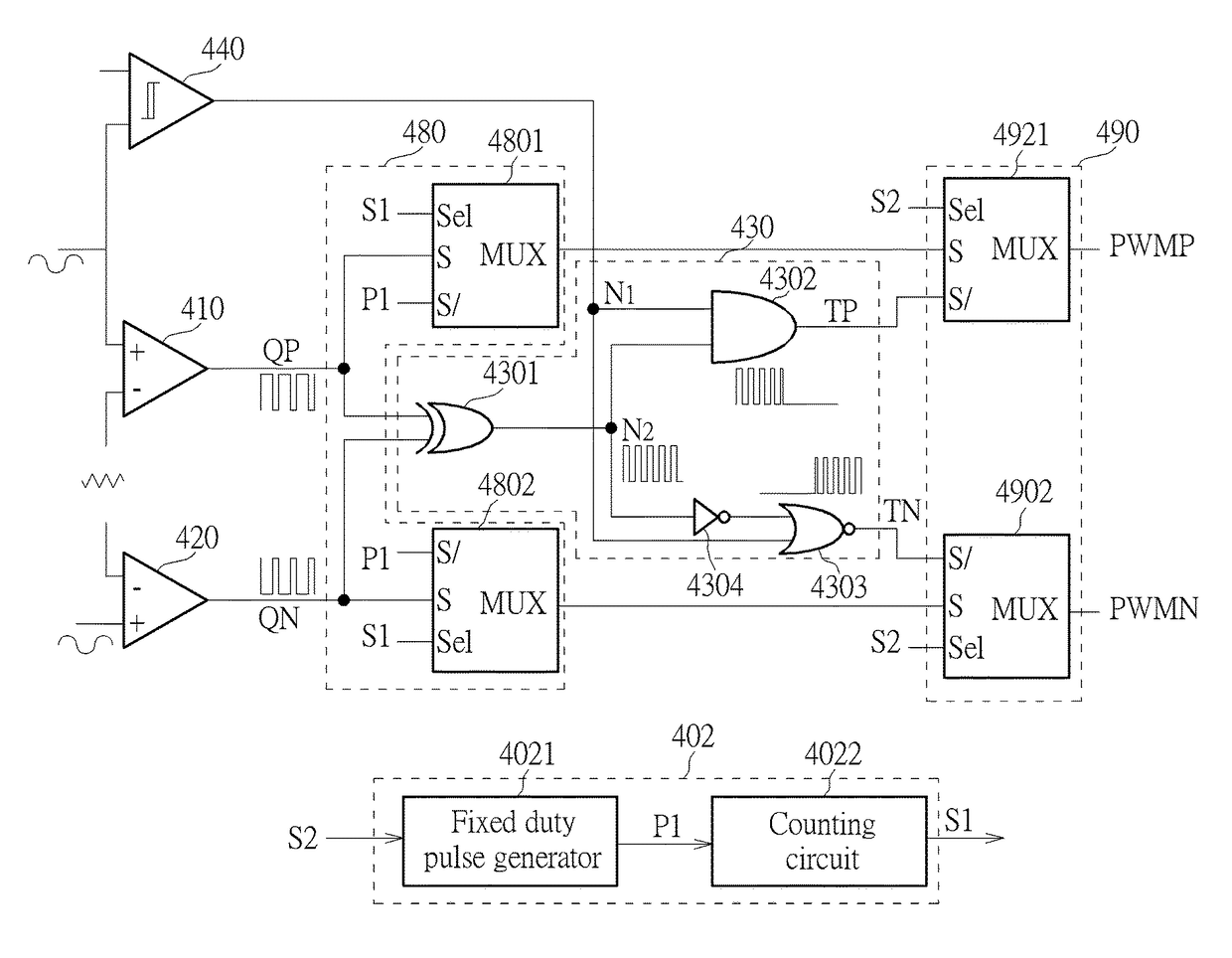

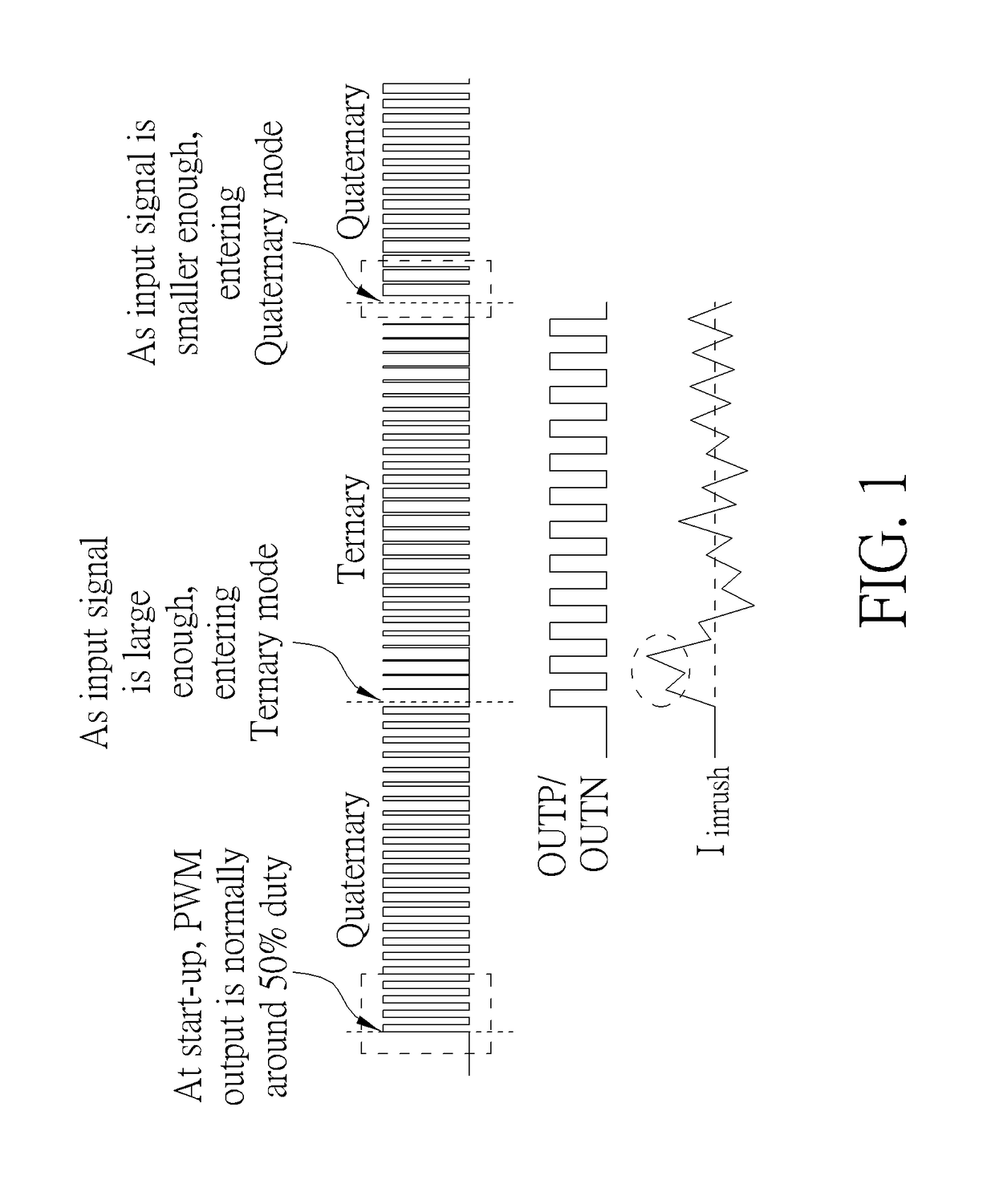

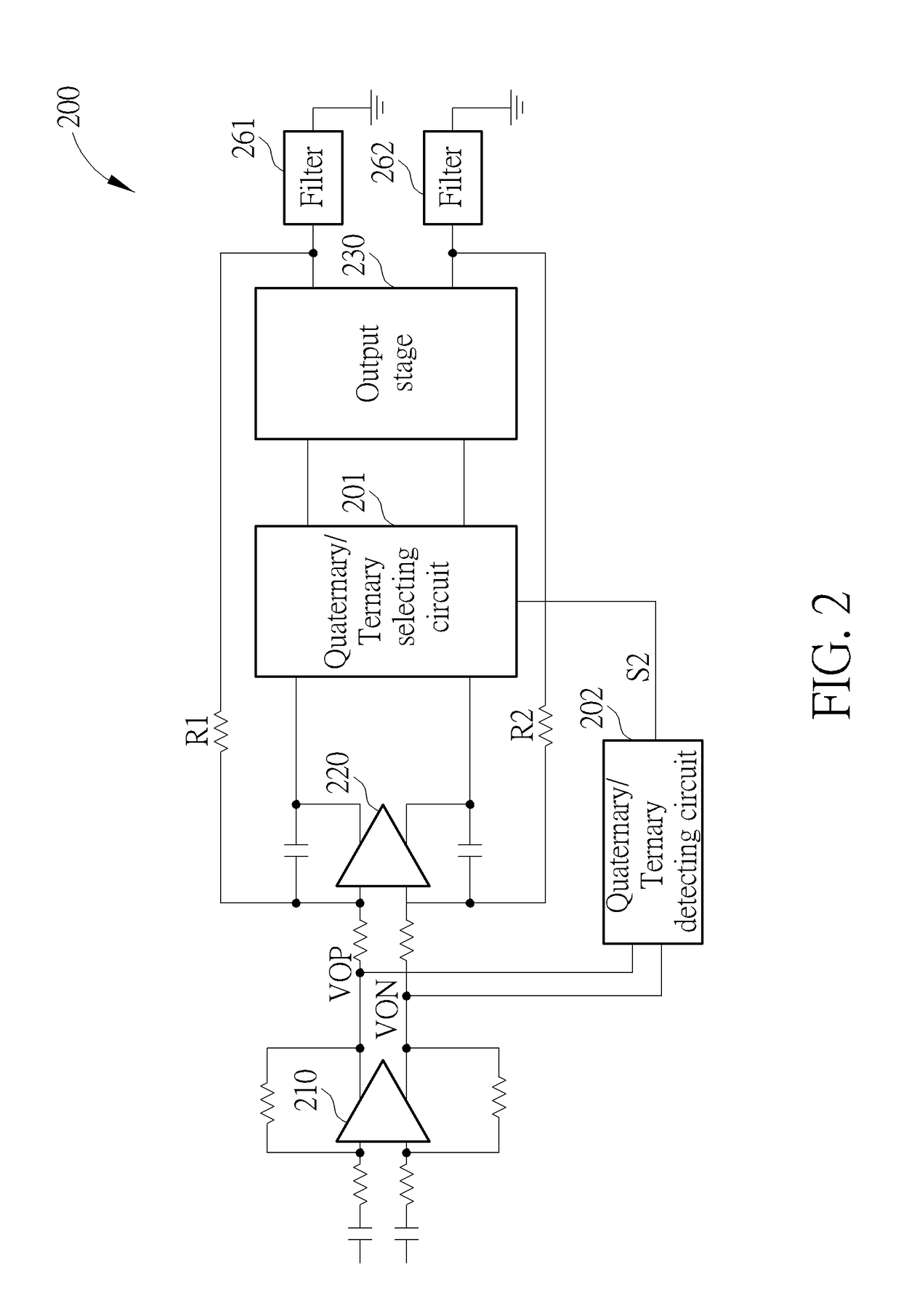

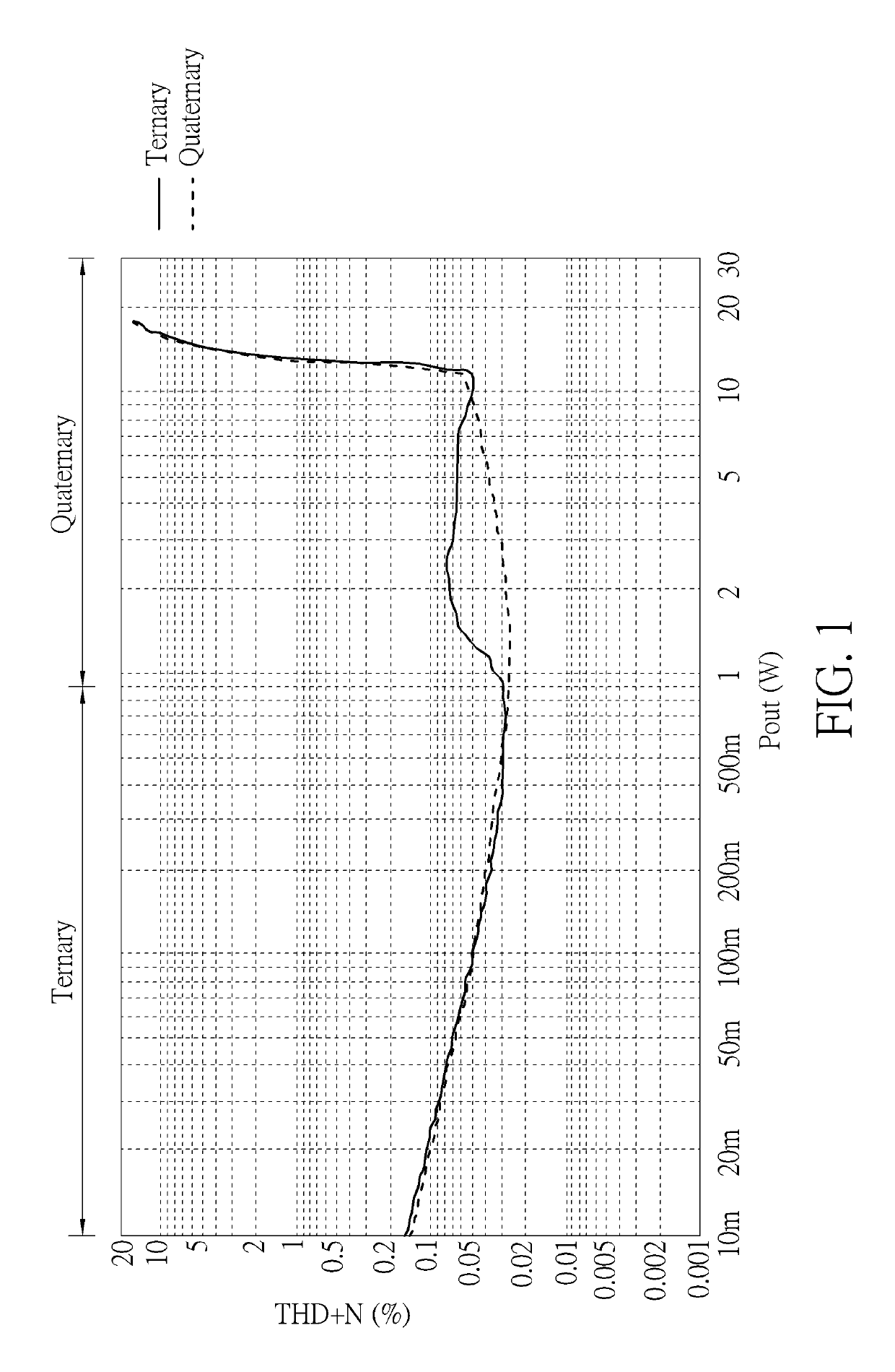

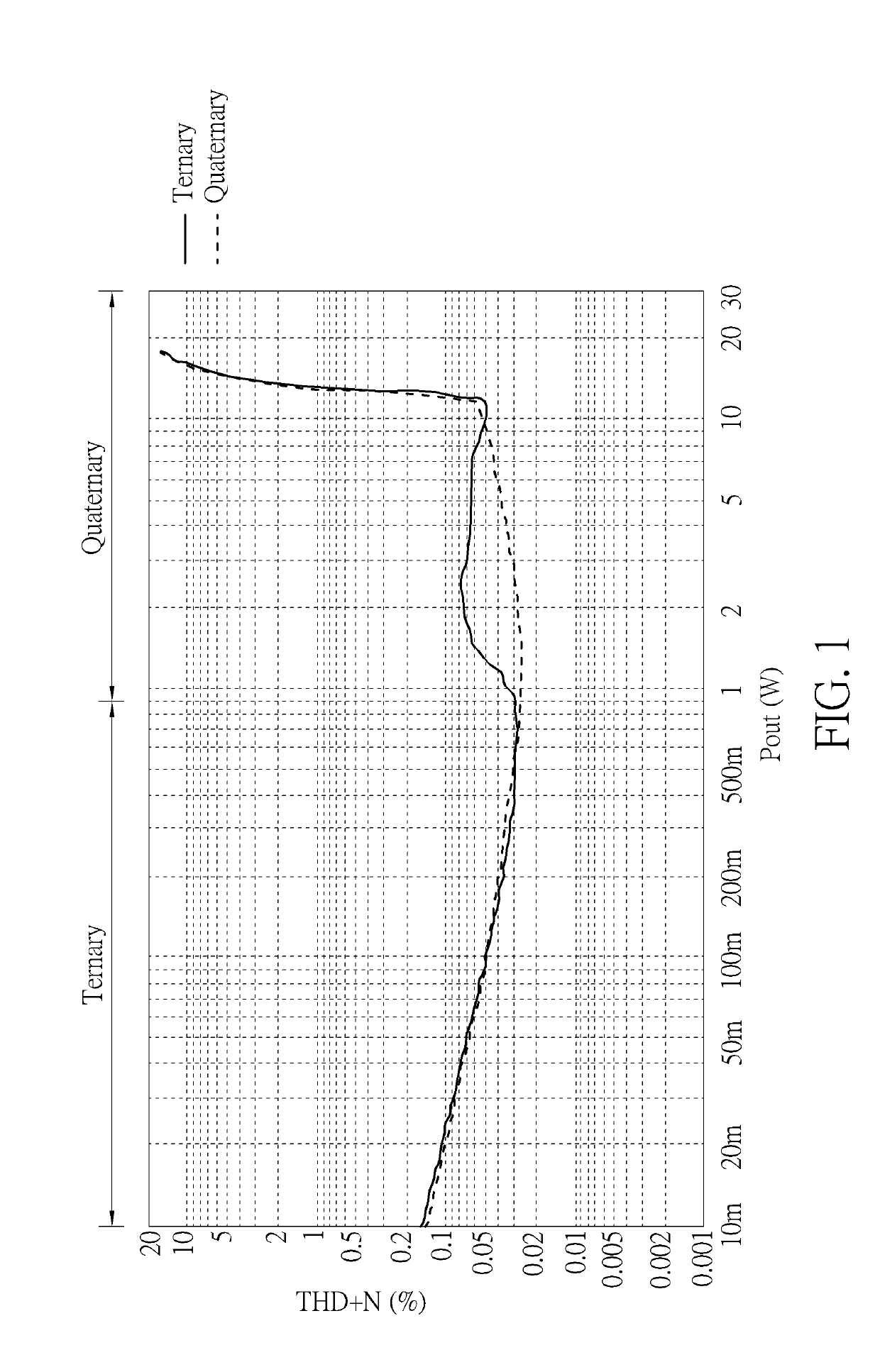

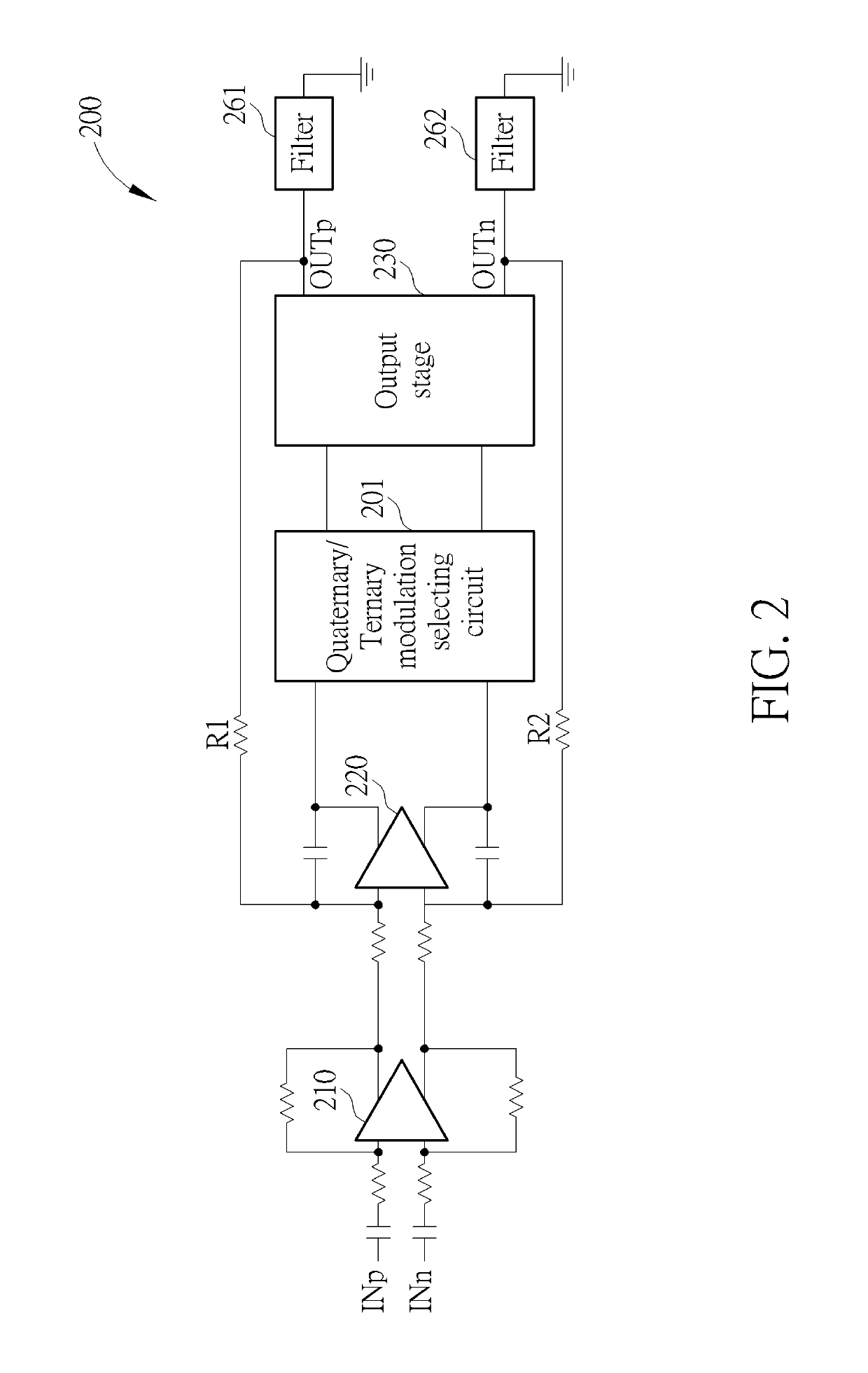

Quaternary/ternary modulation selecting circuit and associated method

A quaternary / ternary modulation selecting method of an audio amplifier includes: generating a ternary signal and a quaternary signal; generating a plurality of pulses with limited duty cycles; and selecting one of the quaternary signal, the ternary signal and the plurality of pulses for an output stage of the audio amplifier.

Owner:ELITE SEMICON MEMORY TECH INC

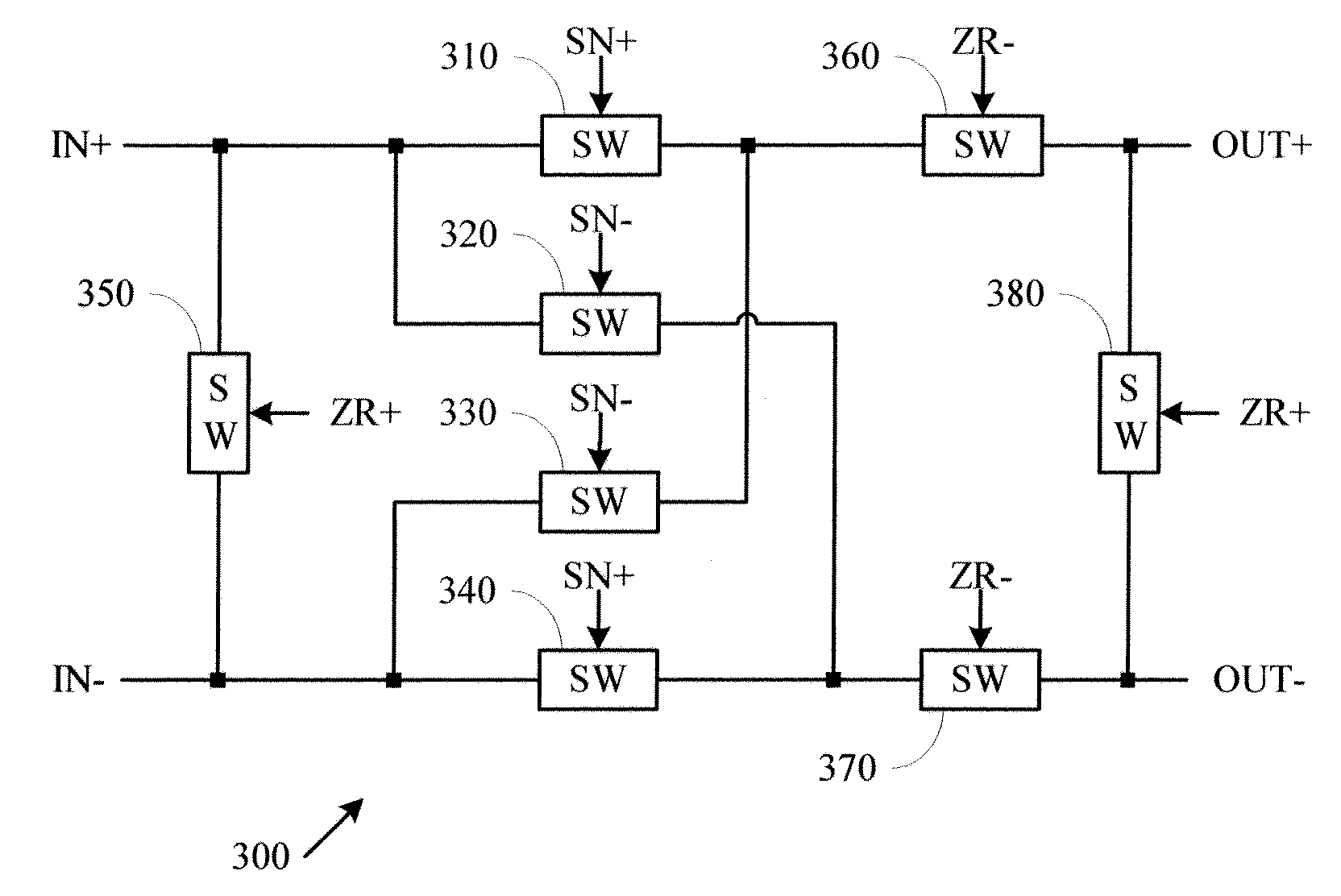

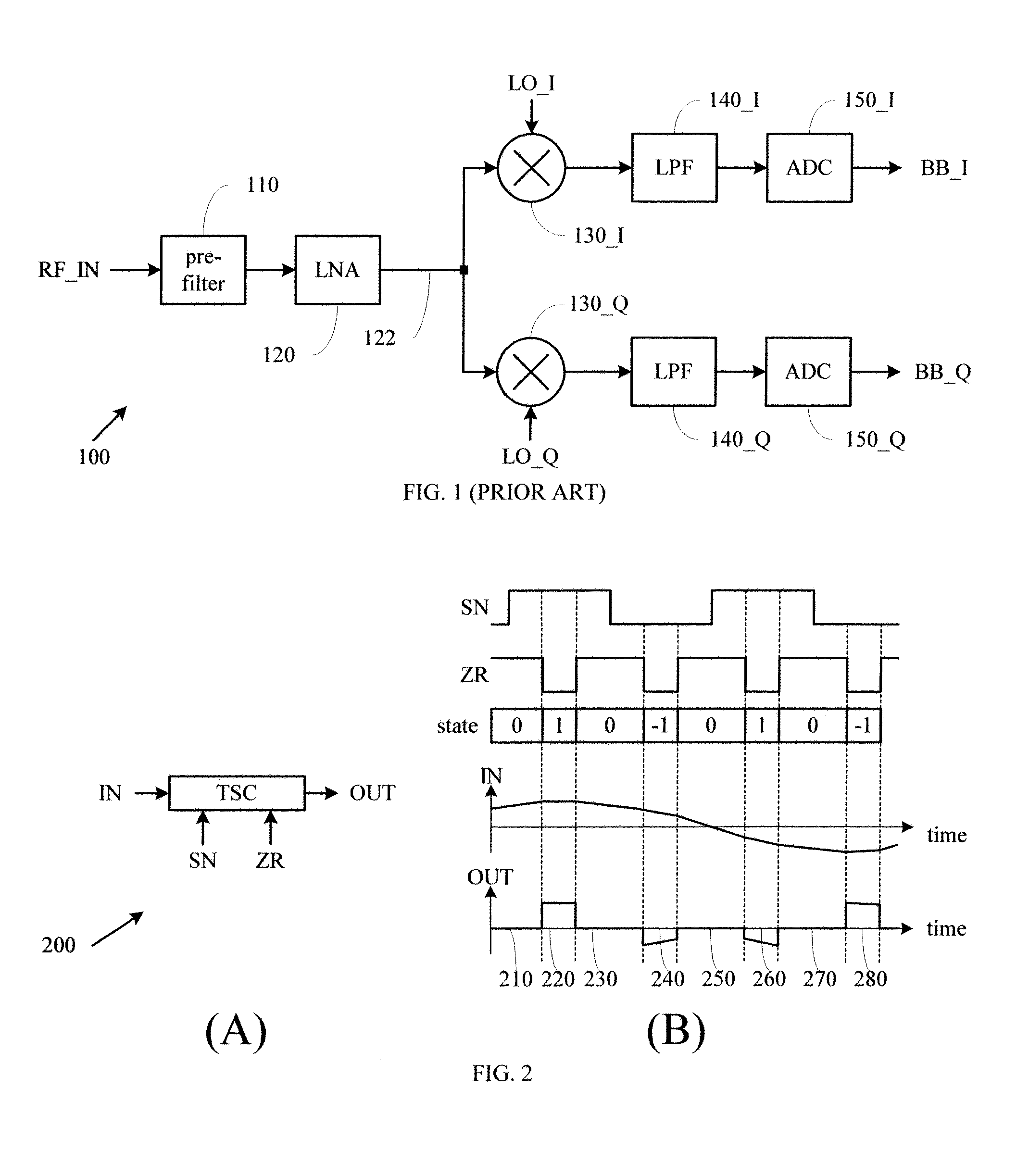

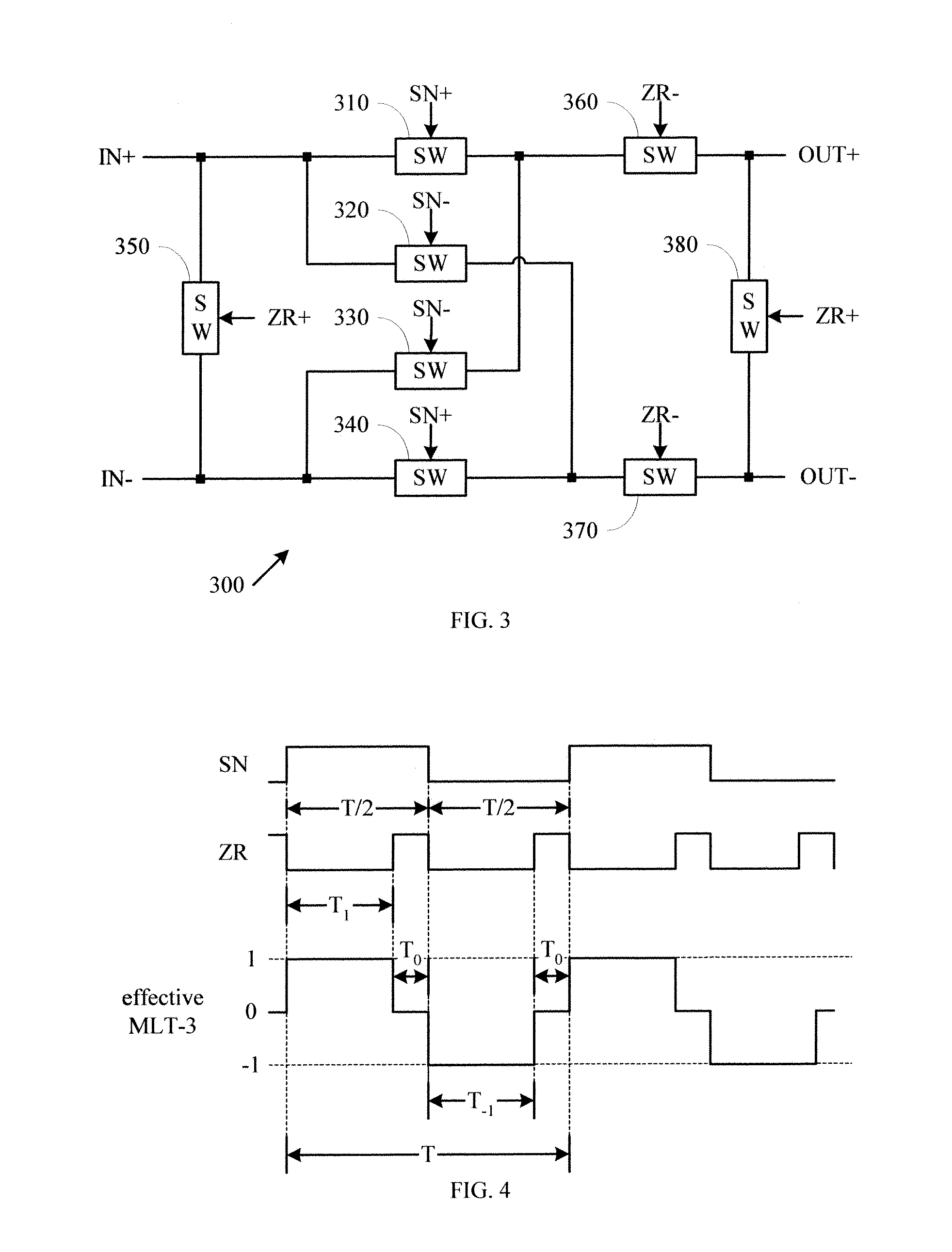

Tri-state chopper for frequency conversion

ActiveUS20070270109A1Suppression mixingModulation transferenceTransmissionFrequency conversionTernary signal

A tri-state chopper (TSC) circuit and method is disclosed. The tri-state chopper (TSC) circuit receives an input signal and a ternary signal and generates an output signal, wherein: the output signal tracks the input signal in both magnitude and sign when the ternary signal is in a first state; the output signal tracks the input signal in magnitude but has an opposite sign when the ternary signal is in a second state; and the output signal is set to zero when the ternary signal is in a third state.

Owner:REALTEK SEMICON CORP

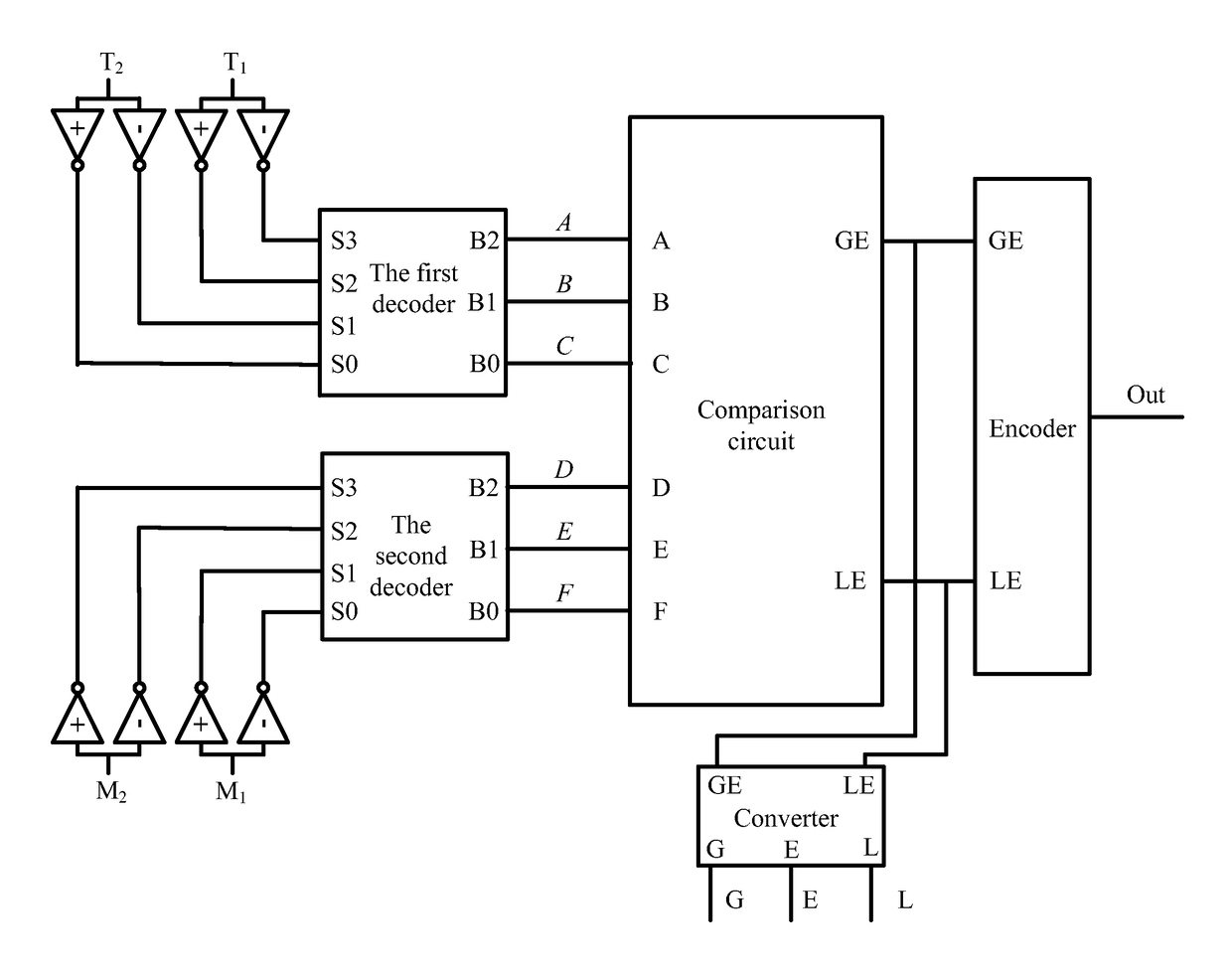

Carbon nanotube-based ternary comparator

ActiveUS9640764B2Reduce power consumptionReduce areaMultiple input and output pulse circuitsSolid-state devicesCarbon nanotubeEngineering

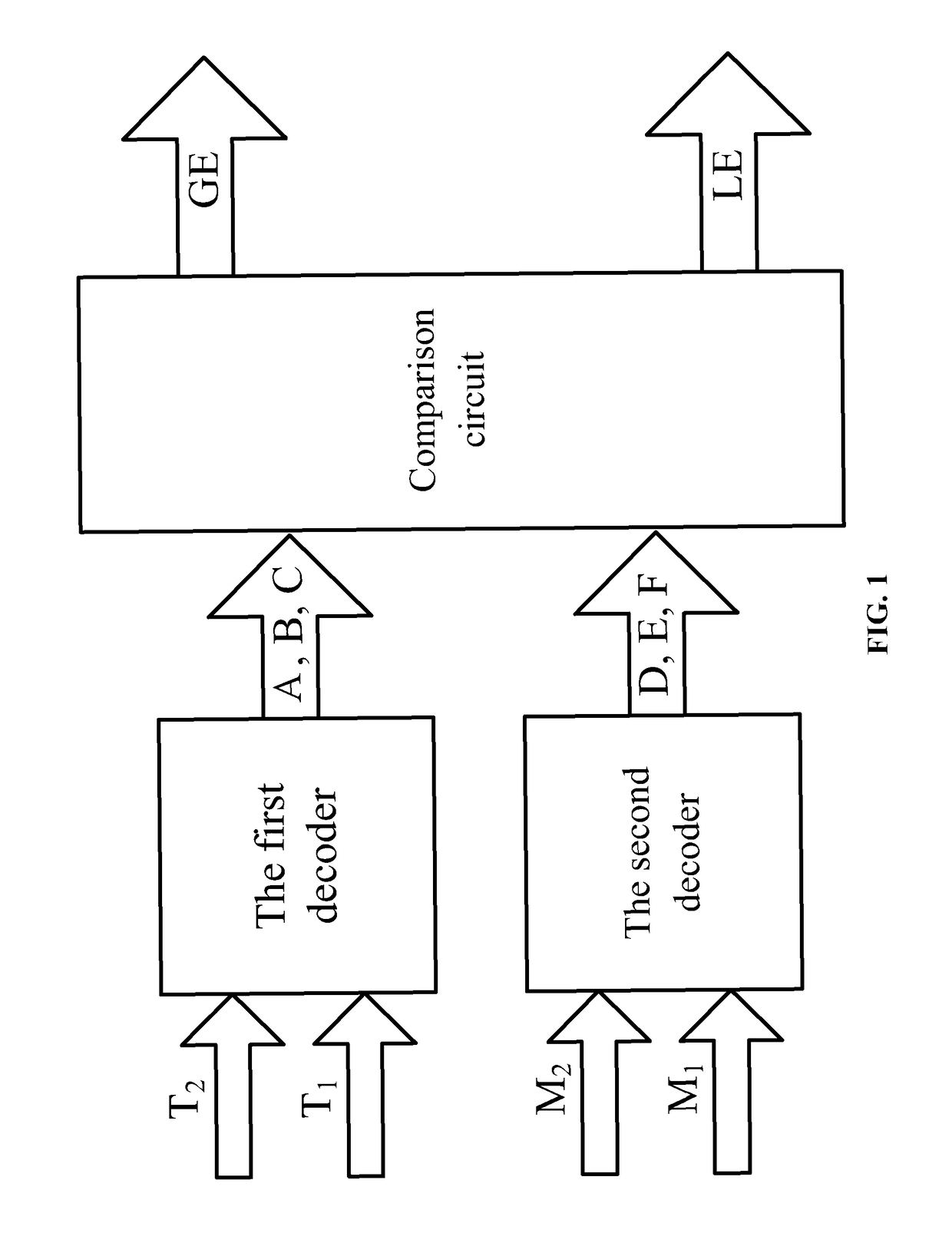

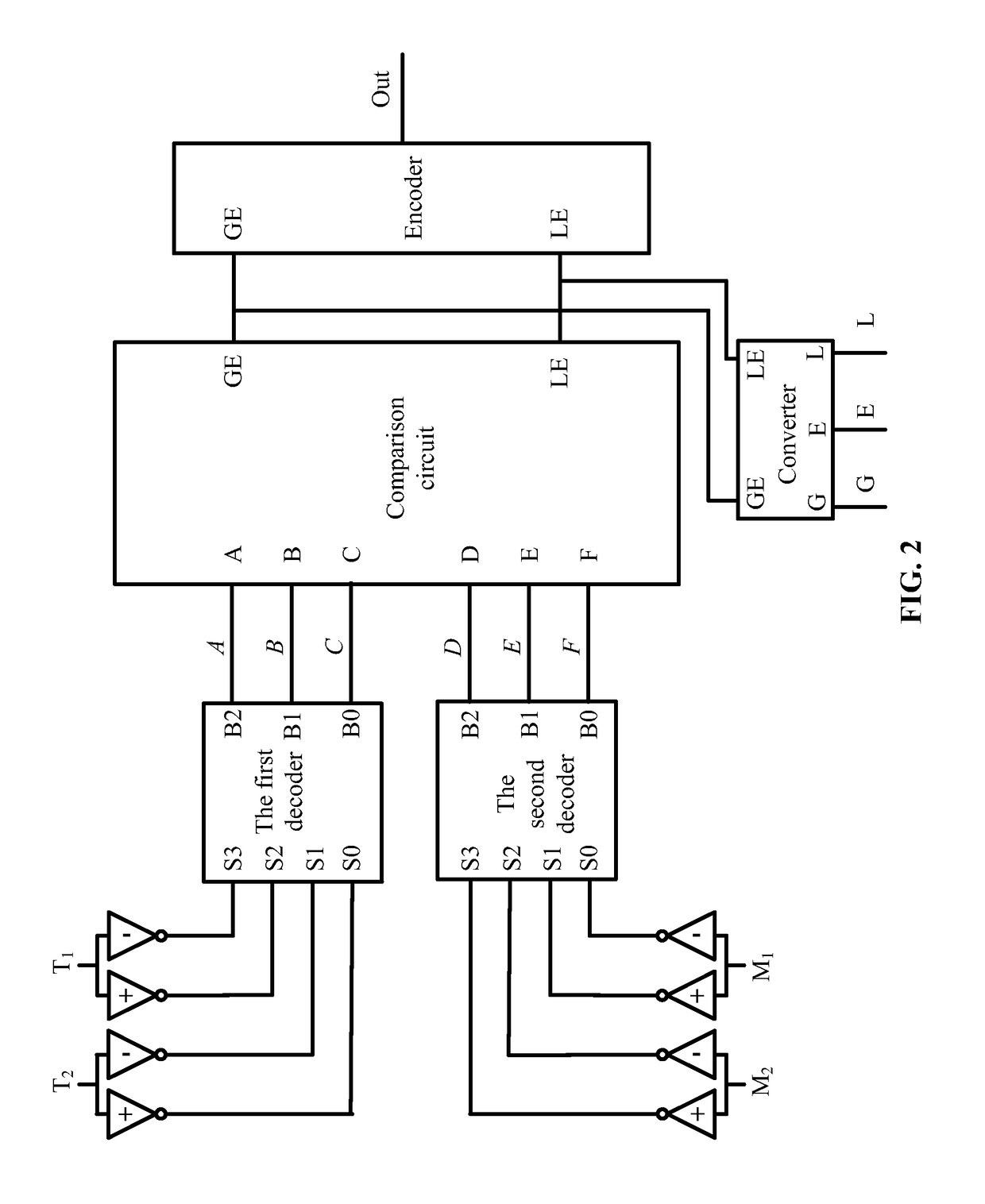

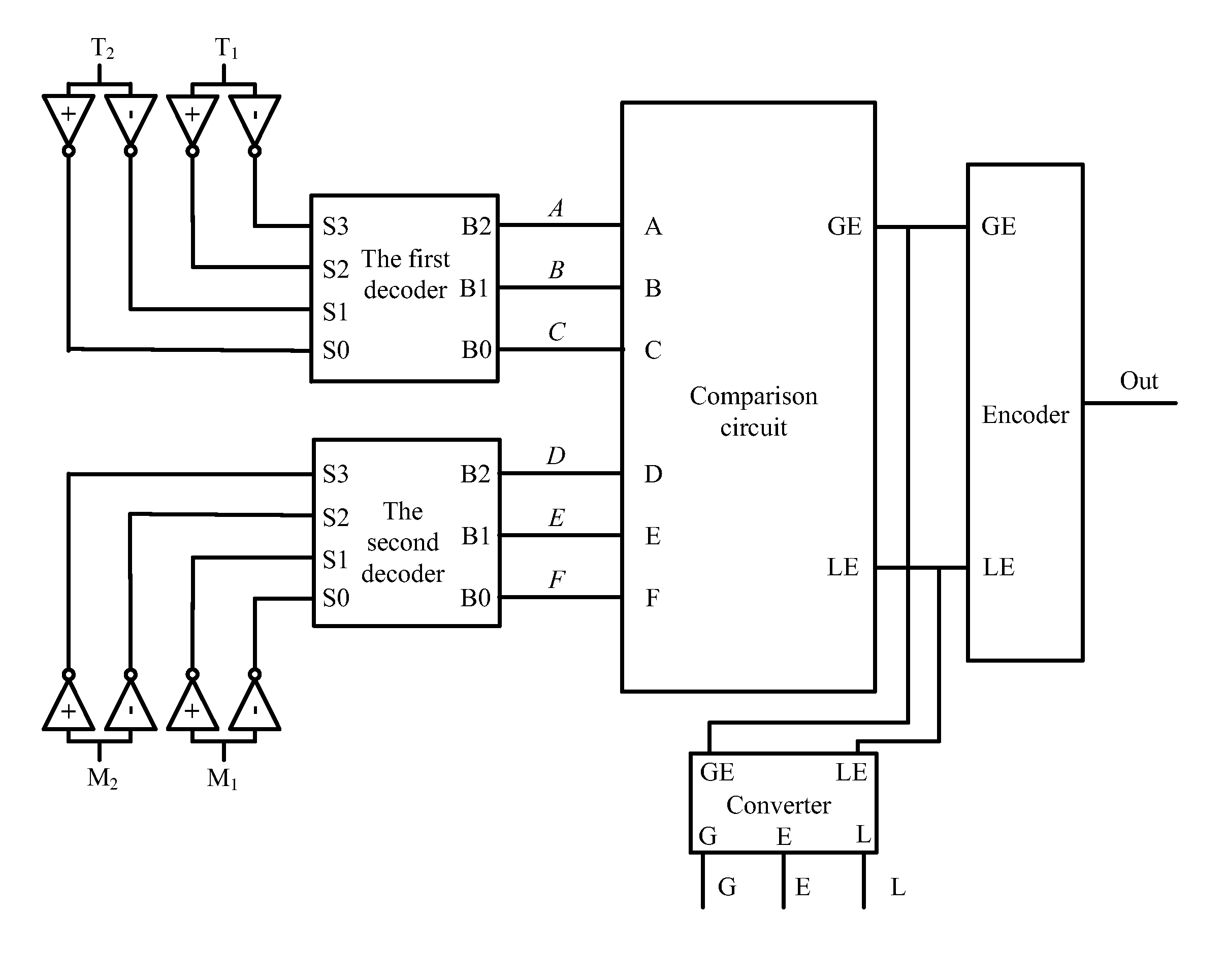

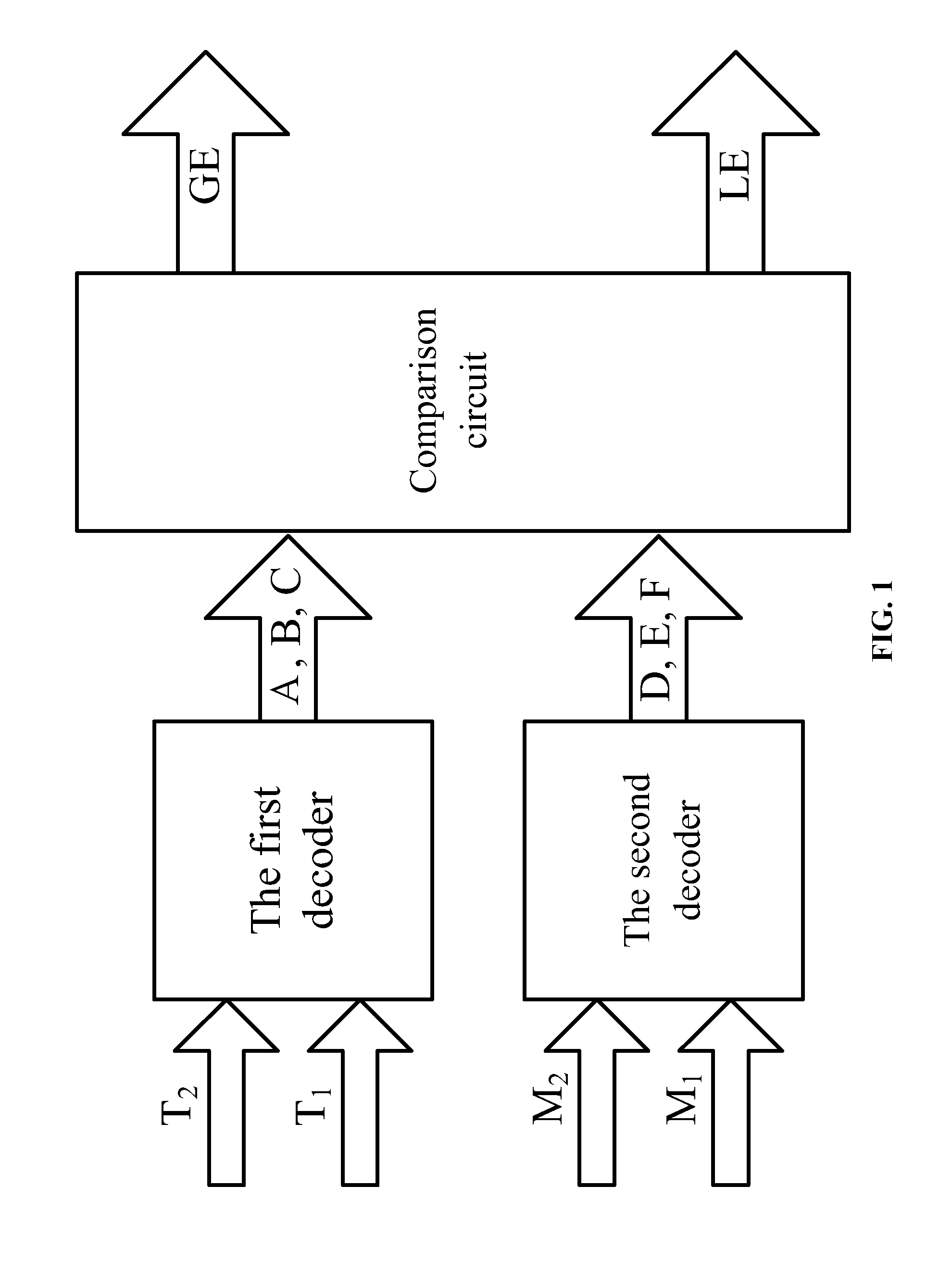

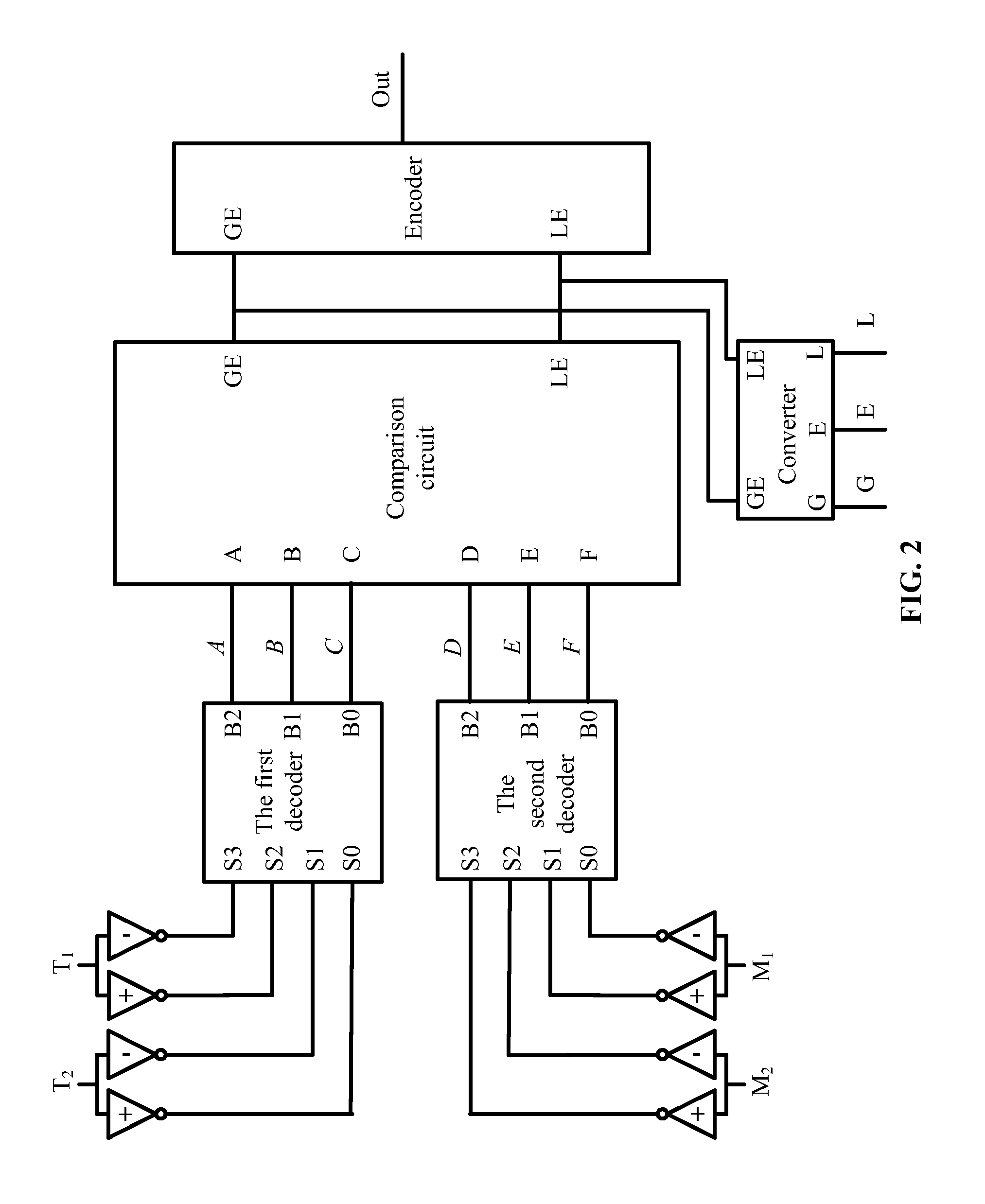

A carbon nanotube-based ternary comparator including a first decoder, a second decoder, and a comparison circuit. The comparison circuit includes: a first comparison unit for producing a greater-than-or-equal-to signal, and a second comparison unit for producing a less-than-or-equal-to signal. A first two-bit ternary signal is input into the signal input terminal of the first decoder. A first three-bit binary signal and a phase inverted signal of the first three-bit binary signal are output from a signal output terminal of the first decoder. A second two-bit ternary signal is input into the signal input terminal of the second decoder. A second three-bit binary signal and a phase inverted signal of the second three-bit binary signal are output from the signal output terminal of the second decoder.

Owner:NINGBO UNIV

Method and apparatus for detecting logical signal

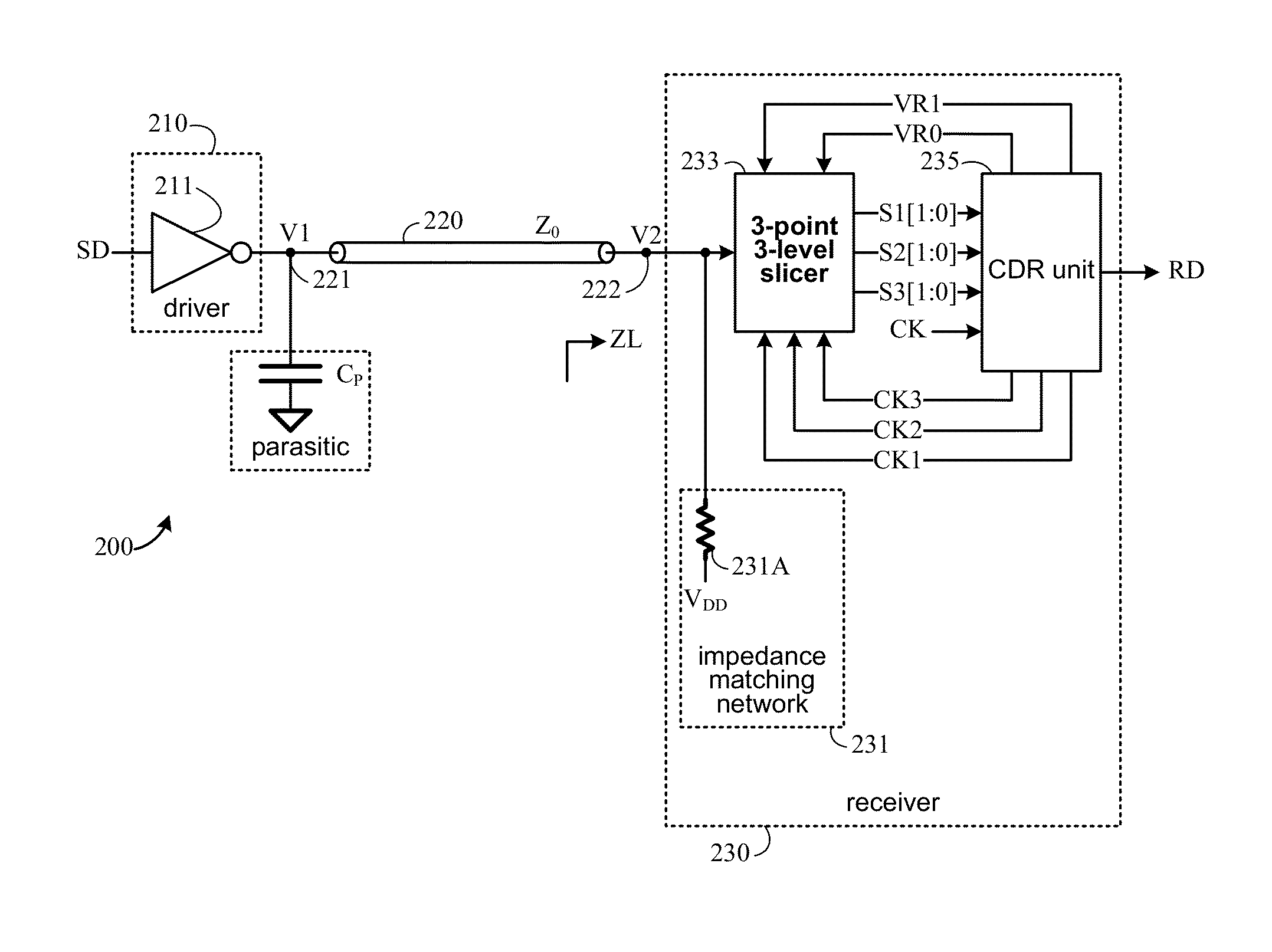

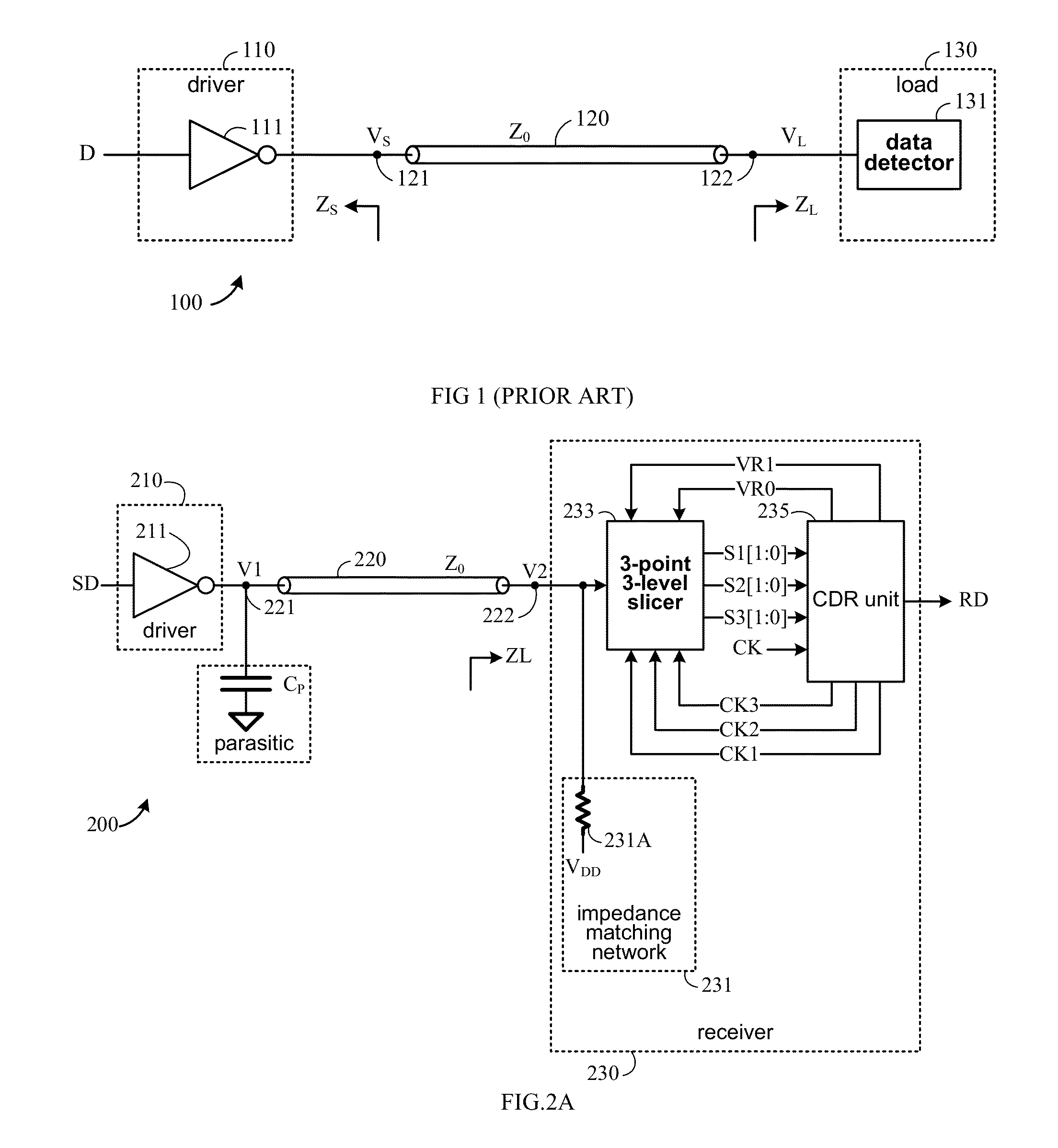

ActiveUS9350529B1High resolutionImprove accuracyAngle demodulation by phase difference detectionSynchronising arrangementThree levelEngineering

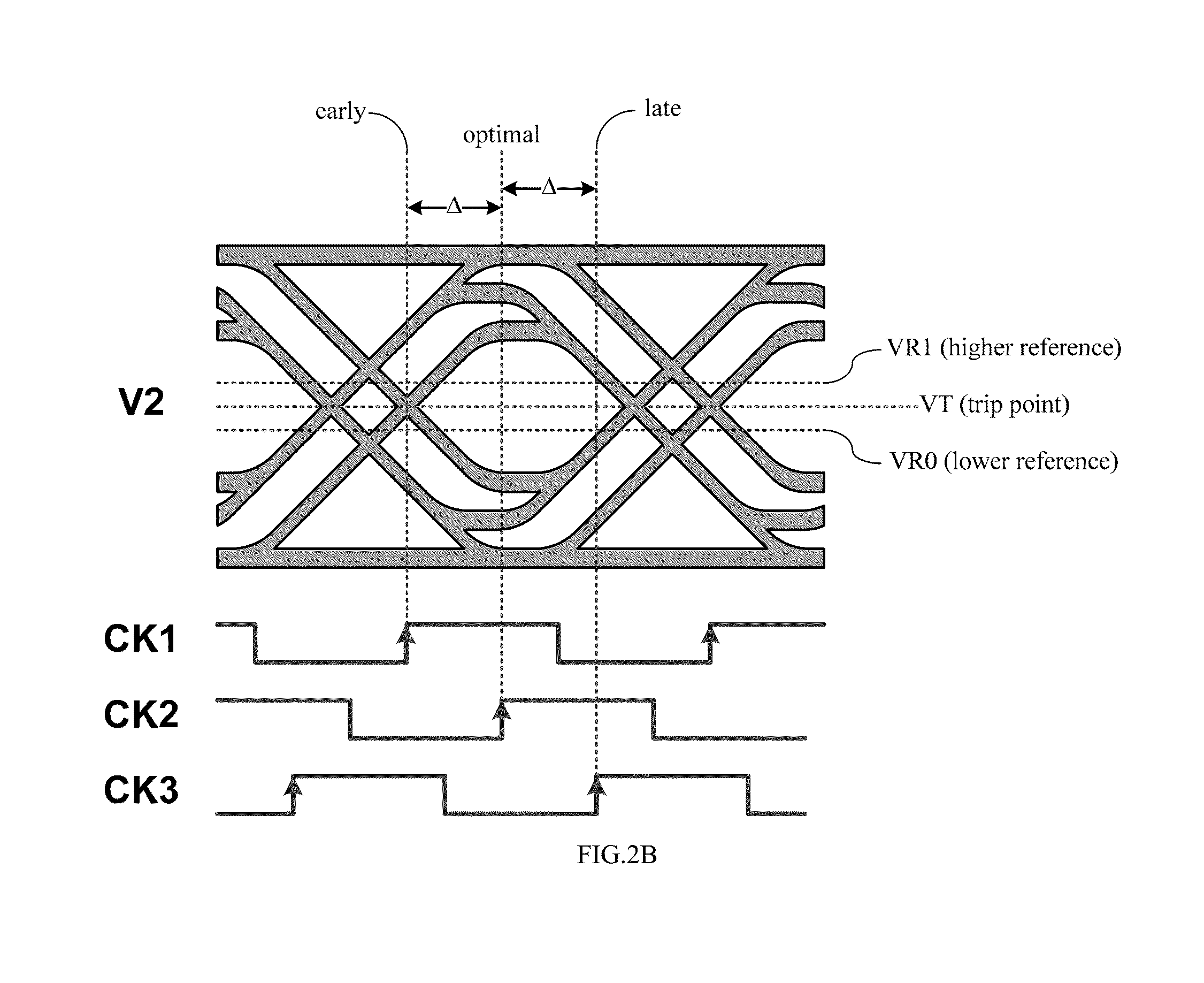

A logical transmission system includes a driver configured to receive a source data and output a first voltage at a first node; a transmission line of a characteristic impedance configured to couple the first node to a second node; a three-point three-level slicer configured to receive a second voltage at the second node and output a first ternary signal, a second ternary signal, and a third ternary in accordance with a first reference voltage, a second reference voltage, a first clock, a second clock, and a third clock; and a CDR (clock-data recovery) unit configured to receive a reference clock, the first ternary signal, the second ternary signal, and the third ternary signal and output a recovered data, the first reference voltage, the second reference voltage, the first clock, the second clock, and the third clock.

Owner:REALTEK SEMICON CORP

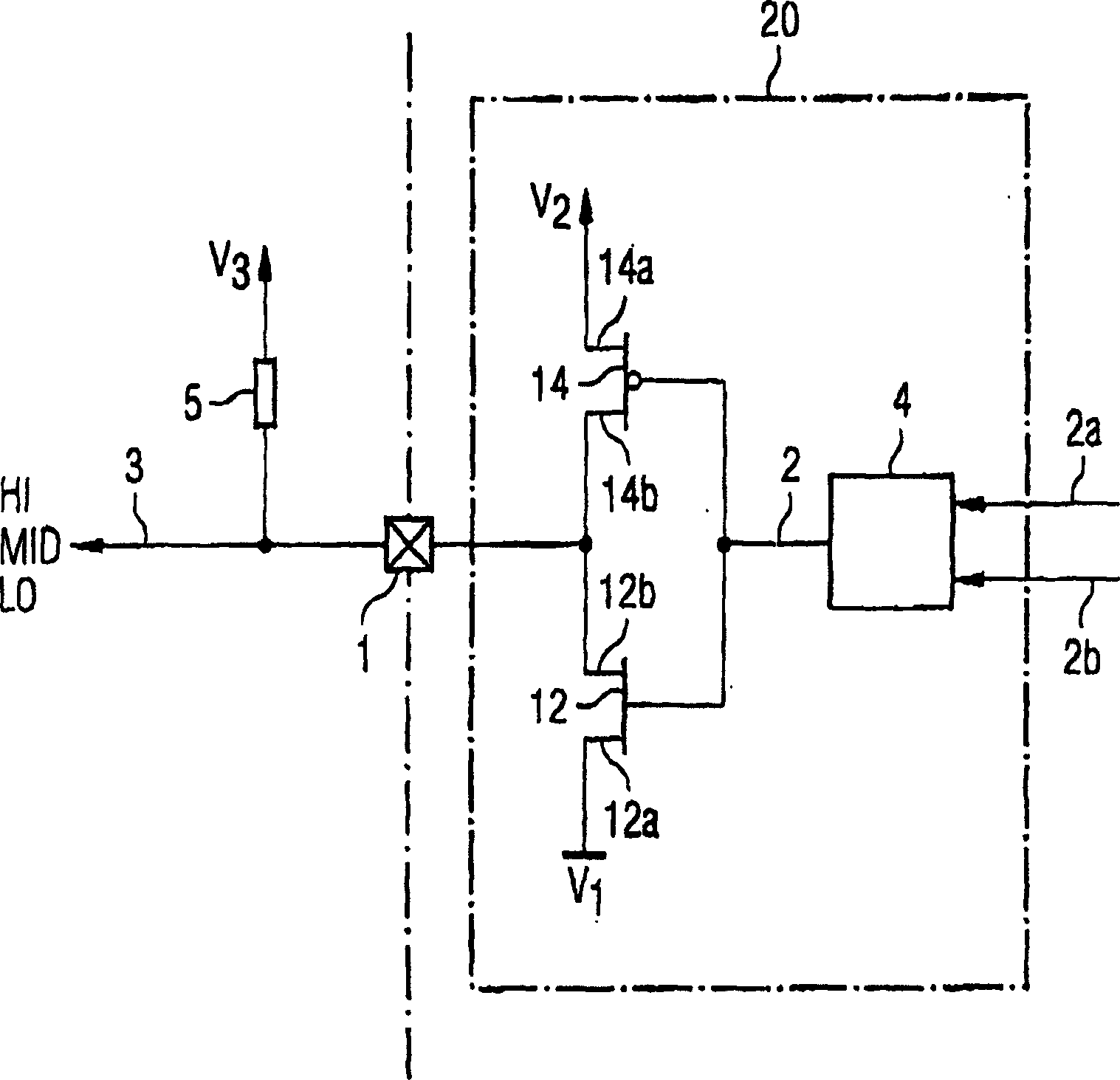

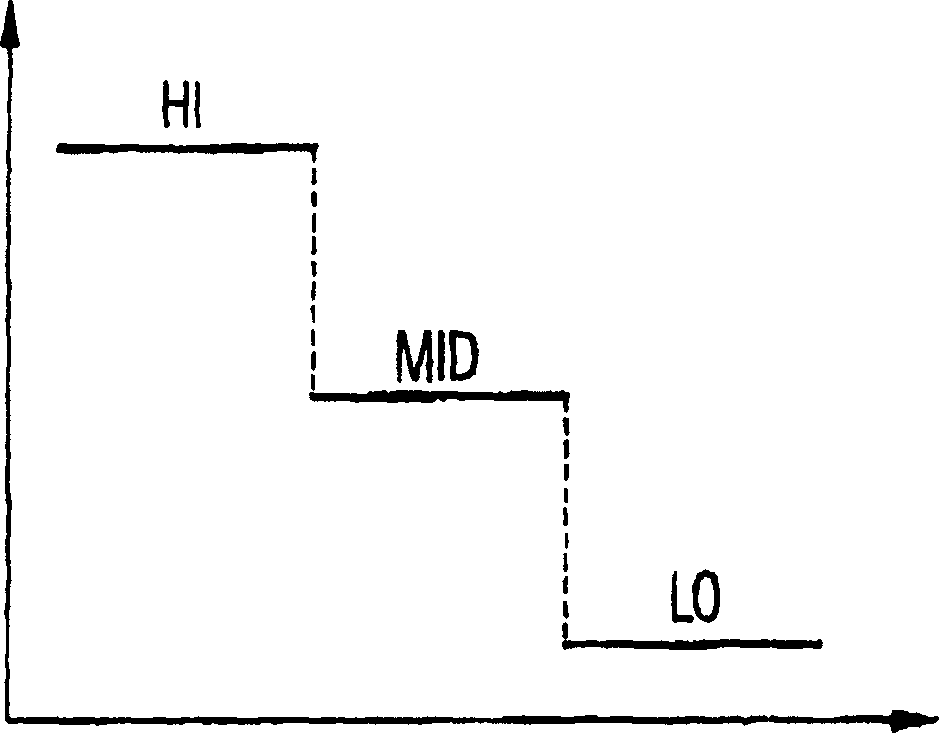

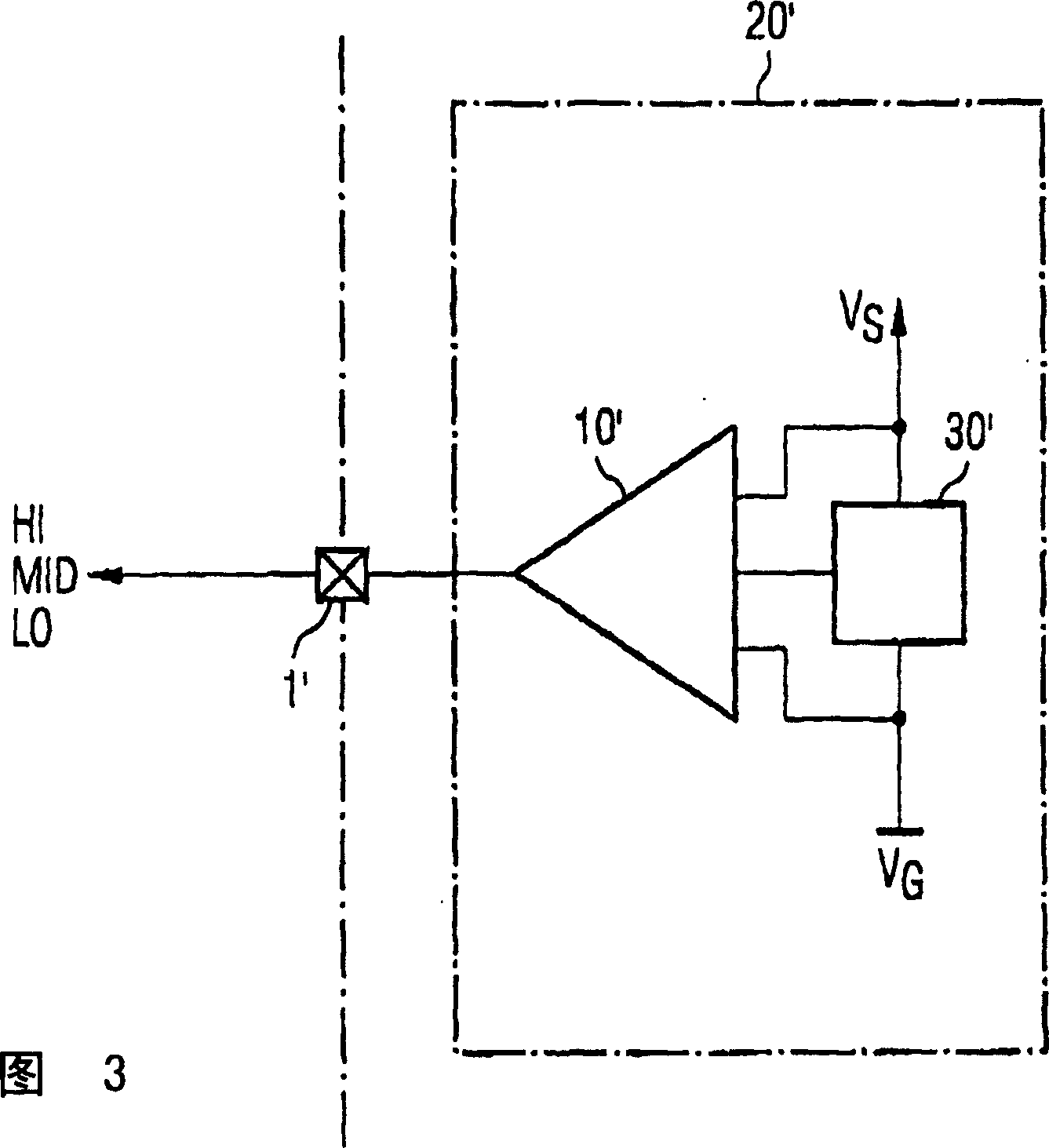

Method for producing ternary signal and circuit device

InactiveCN1617449AQuantity reductionLow costLogic circuits coupling/interface using field-effect transistorsElectronic switchingElectrical conductorTernary signal

According to a method for generating a ternary signal, a first signal level (LO) is generated by the signal output (1), wherein the signal output (1) is connected to a first potential (V1). A second signal level (MID) is generated, and wherein the signal output is connected to a second potential (V2). And in order to generate a third signal level (HI), the signal output terminal (1) is connected to a third potential (V3) through a resistance device, so when the signal output terminal (1) is connected from the first When a potential (V1) and the second potential (V2) are decoupled, the electrical three signal level (HI) will be generated, wherein the first potential (V1) can be a ground potential, and the second potential ( V2 ) can be an operating voltage of a semiconductor module, and the third potential ( V3 ) can be an external operating voltage.

Owner:INFINEON TECH AG

Carbon nanotube-based ternary comparator

ActiveUS20160268512A1Reduce areaReduce power consumptionMultiple input and output pulse circuitsSolid-state devicesCarbon nanotubeEngineering

A carbon nanotube-based ternary comparator including a first decoder, a second decoder, and a comparison circuit. The comparison circuit includes: a first comparison unit for producing a greater-than-or-equal-to signal, and a second comparison unit for producing a less-than-or-equal-to signal. A first two-bit ternary signal is input into the signal input terminal of the first decoder. A first three-bit binary signal and a phase inverted signal of the first three-bit binary signal are output from a signal output terminal of the first decoder. A second two-bit ternary signal is input into the signal input terminal of the second decoder. A second three-bit binary signal and a phase inverted signal of the second three-bit binary signal are output from the signal output terminal of the second decoder.

Owner:NINGBO UNIV

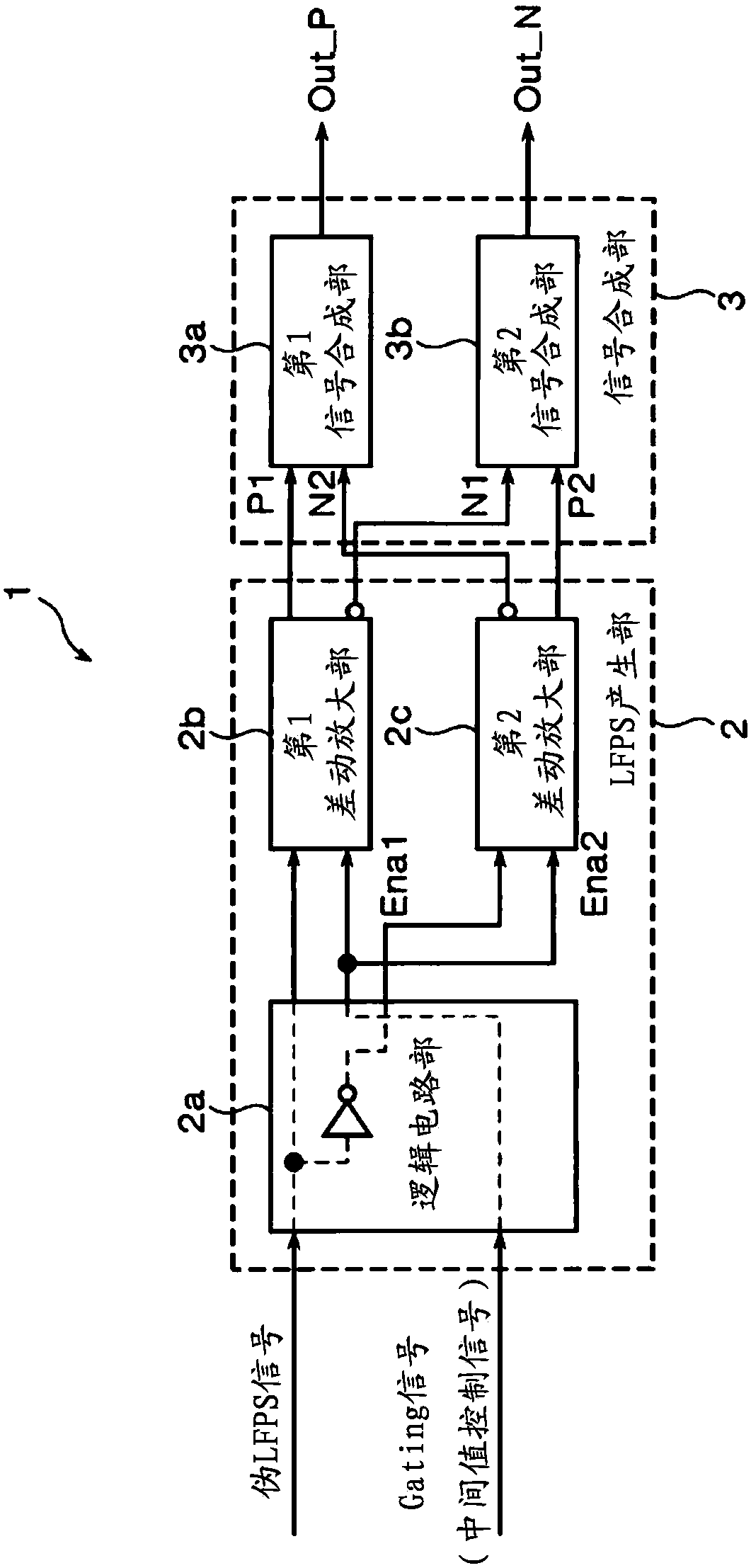

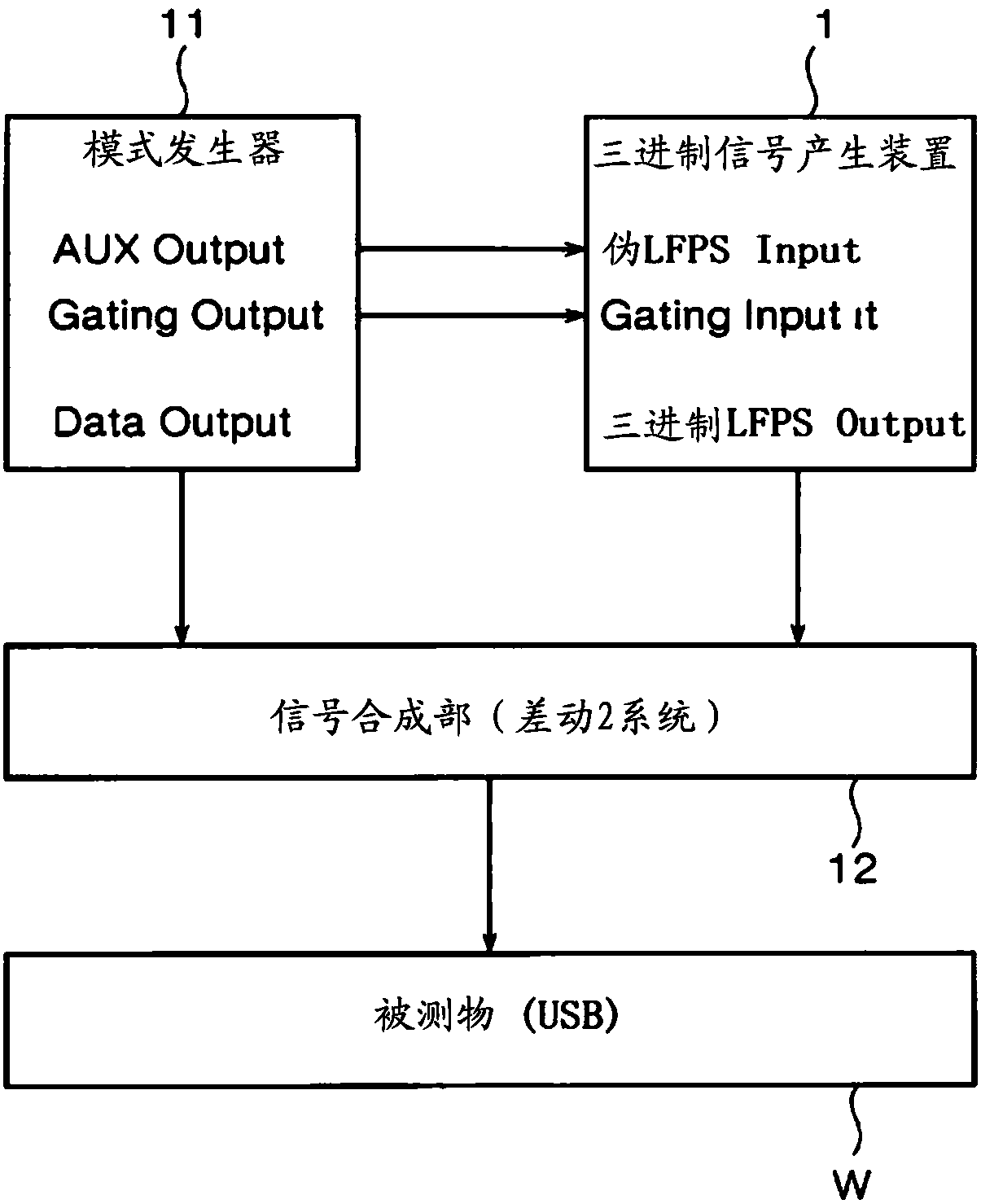

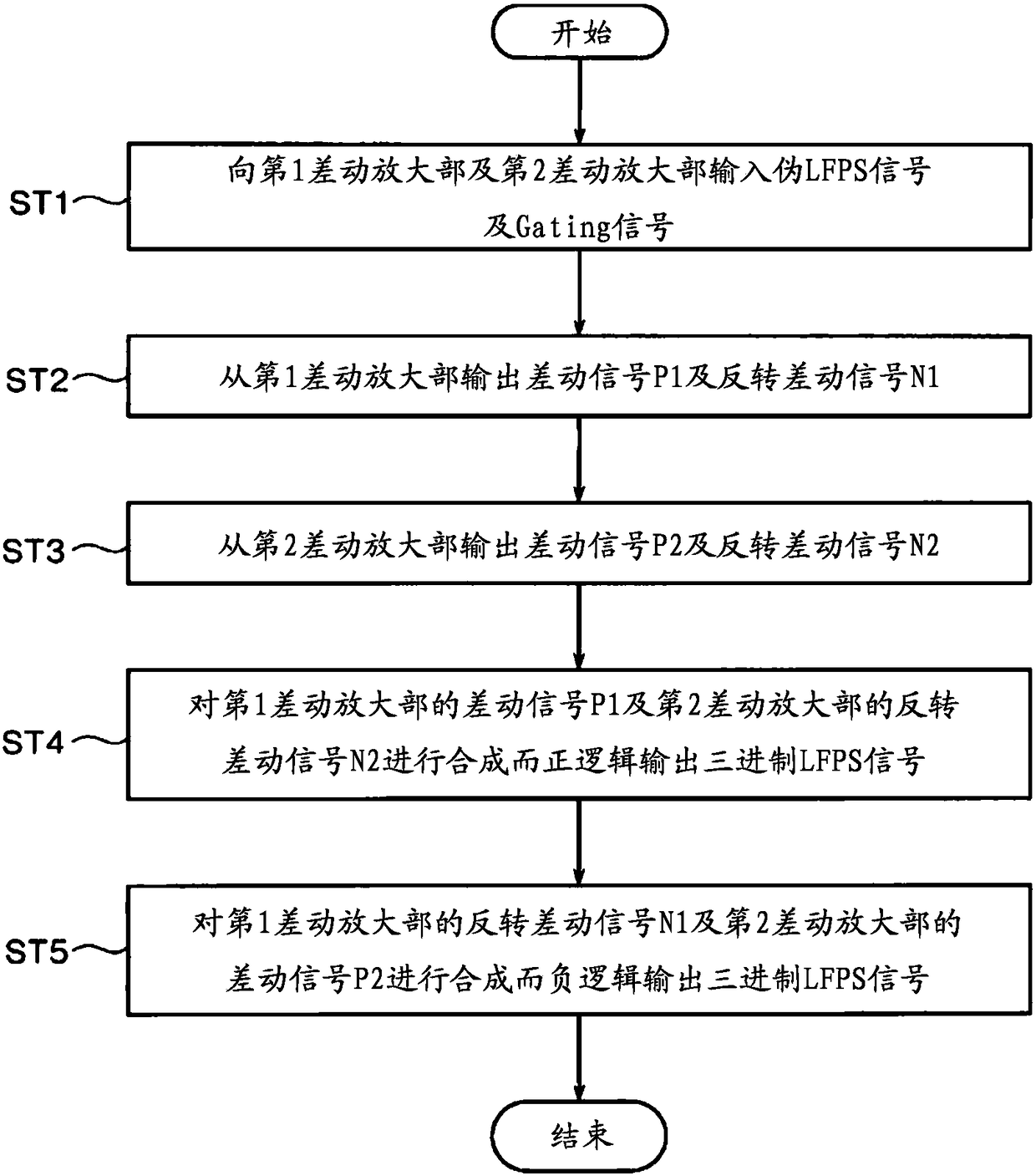

Three-valued signal generation device and three-valued signal generation method

A three-valued signal generation device (1) includes a first differential amplifier (2b) that outputs a differential signal, a second differential amplifier (2c) that outputs a differential signal andan inverted differential signal in accordance with a level based on a reference voltage of an inverted pseudo LFPS signal, which is obtained by inverting a logic level of the pseudo LFPS signal, a first signal synthesis unit (3a) that synthesizes the differential signal from the first differential amplifier (2b) and the inverted differential signal from the second differential amplifier (2c) to perform positive logic output of a three-valued LFPS signal, and a second signal synthesis unit (3b) that synthesizes the inverted differential signal from the first differential amplifier (2b) and thedifferential signal from the second differential amplifier (2c) to perform negative logic output of the three-valued LFPS signal.

Owner:ANRITSU CORP

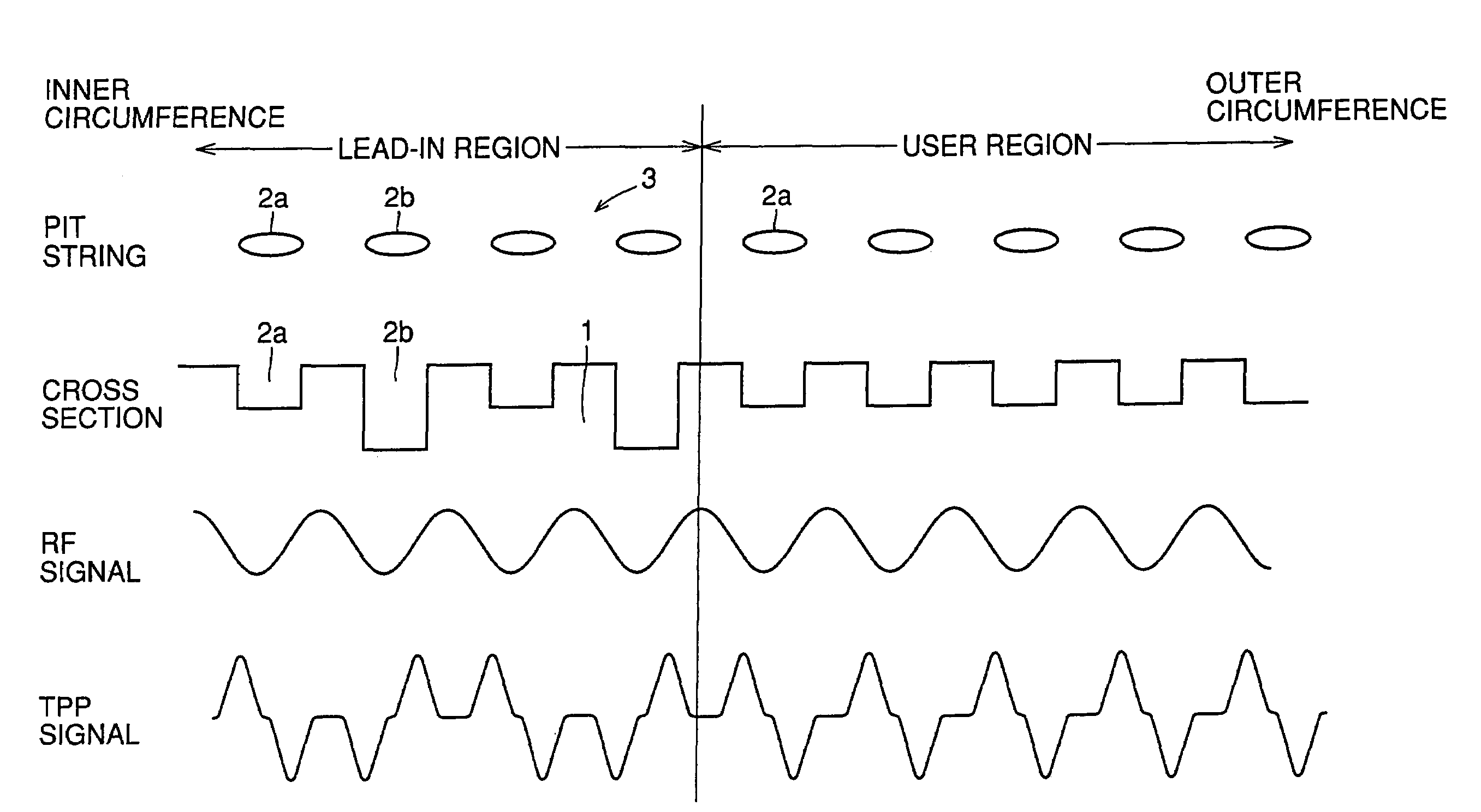

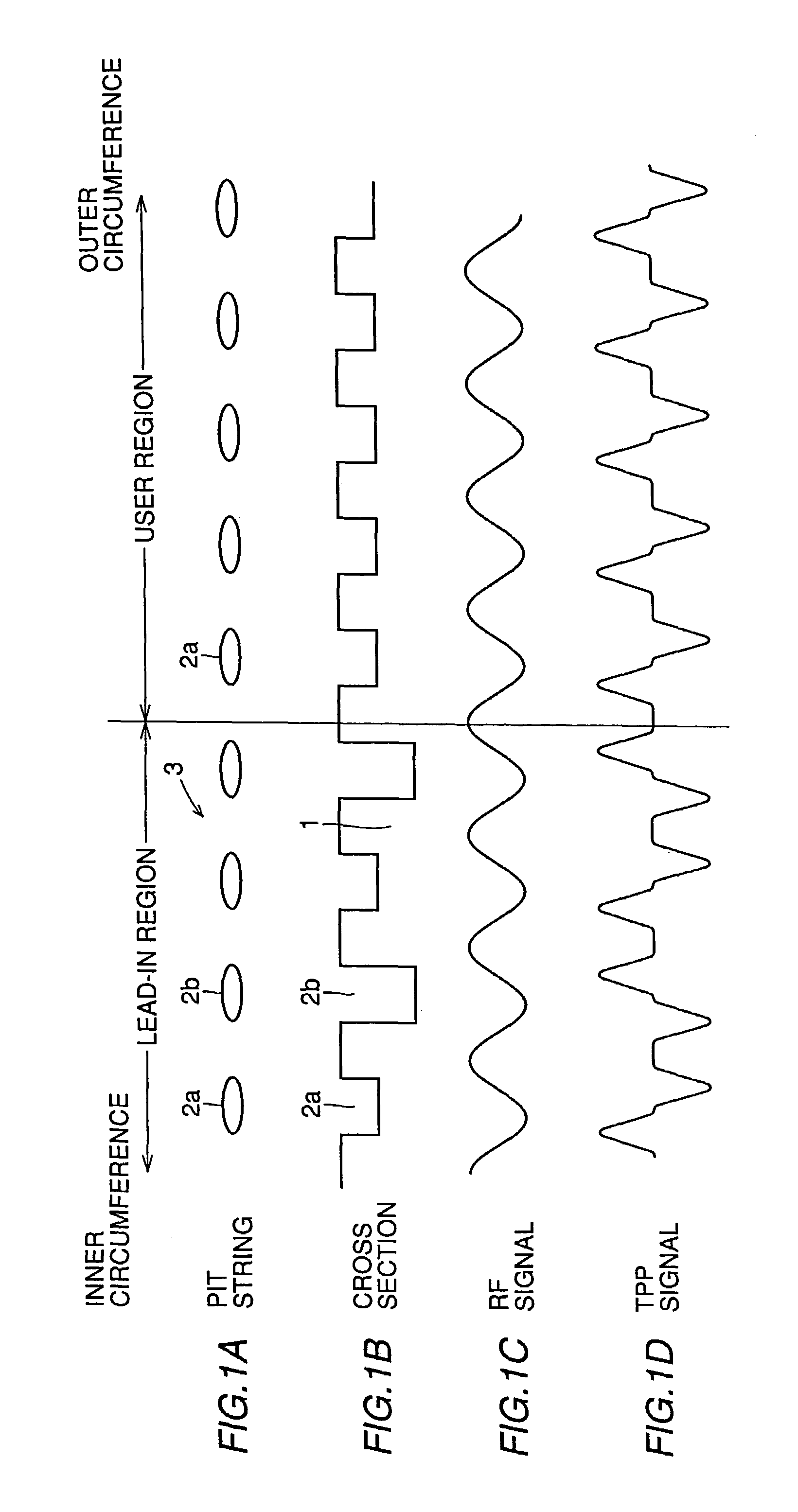

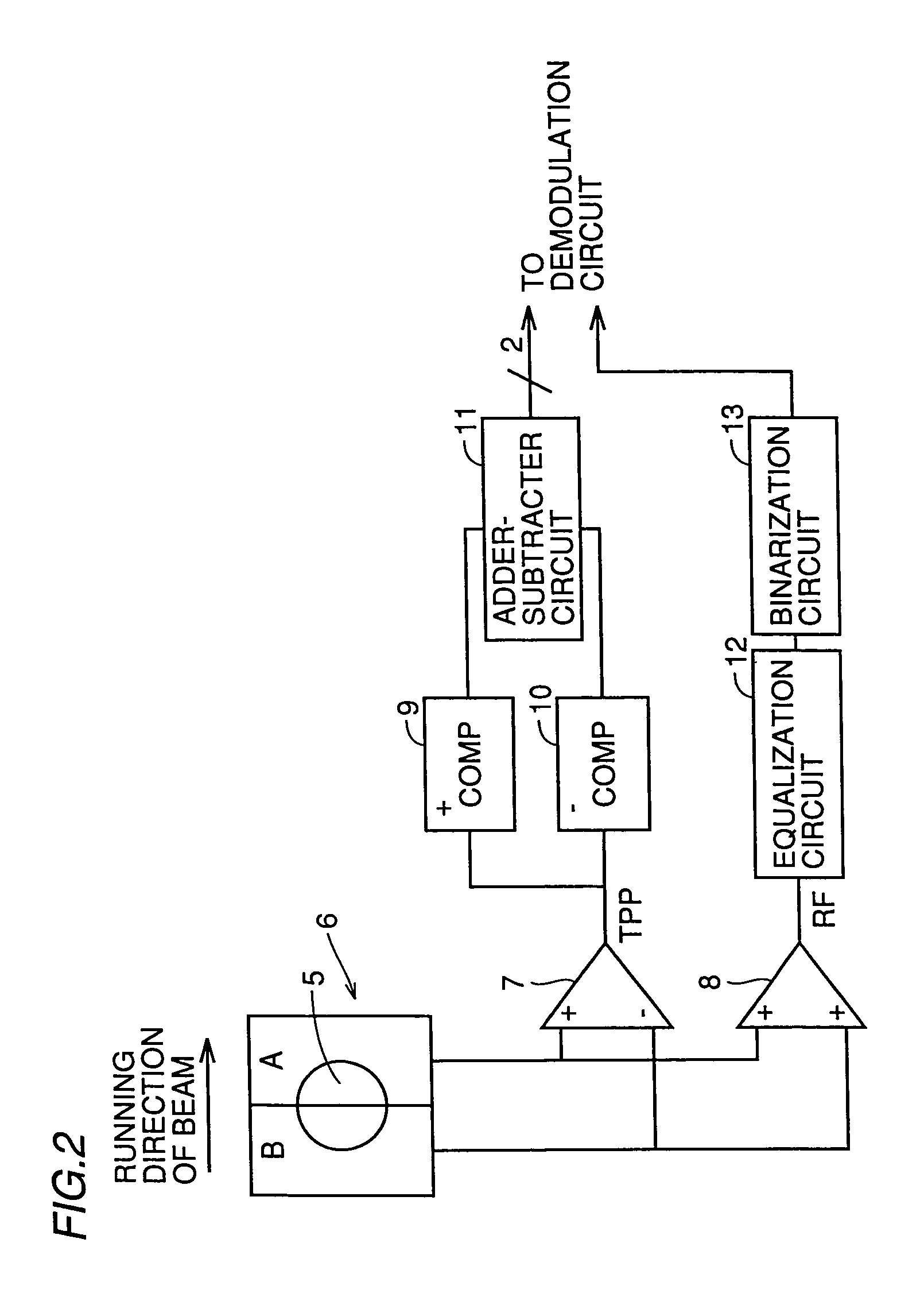

Optical recording medium recorded with information in depth direction, and method and apparatus of reproduction therefrom

InactiveUS7580329B2Enlarging the lead-in regionIncrease capacityFilamentary/web record carriersRecord information storageAudio power amplifierLight beam

An optical disk has a lead-in region provided at the inner circumference side and a user region provided at the outer circumference side. Pit string 3 of pits of different depths is formed in the lead in region. Light beam reflected from the pit string is detected by detector and TPP and RF signals are output by differential amplifier and addition amplifier. A ternary signal is restored from pits based on the TPP and RF signals. Information is recorded by pits of the same depth in the user region. Recording information in the depth direction in the lead-in region increases the recording capacity thereof. The information recorded in the depth direction in the lead-in region cannot be transferred to a user region of another optical disk.

Owner:SHARP KK

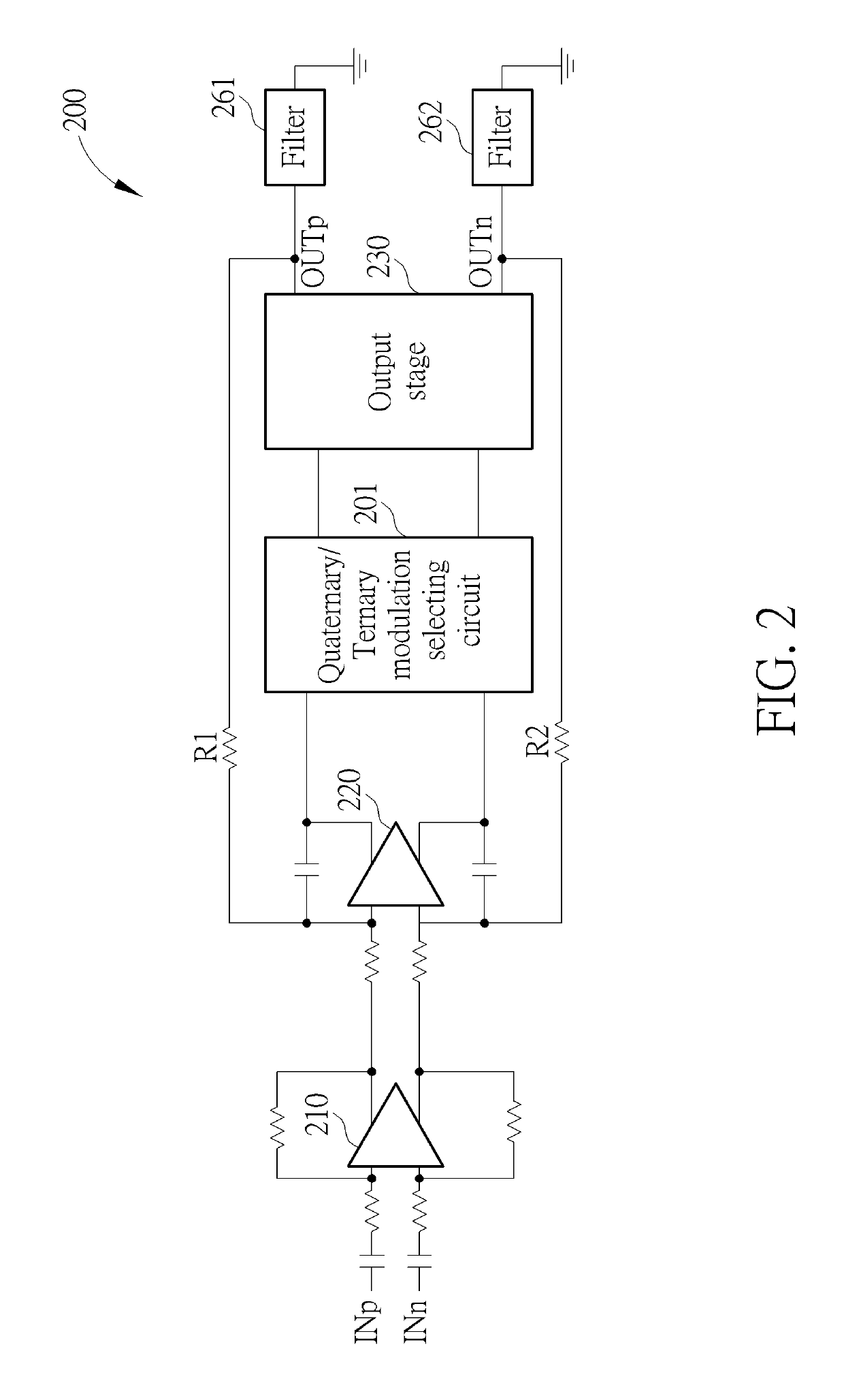

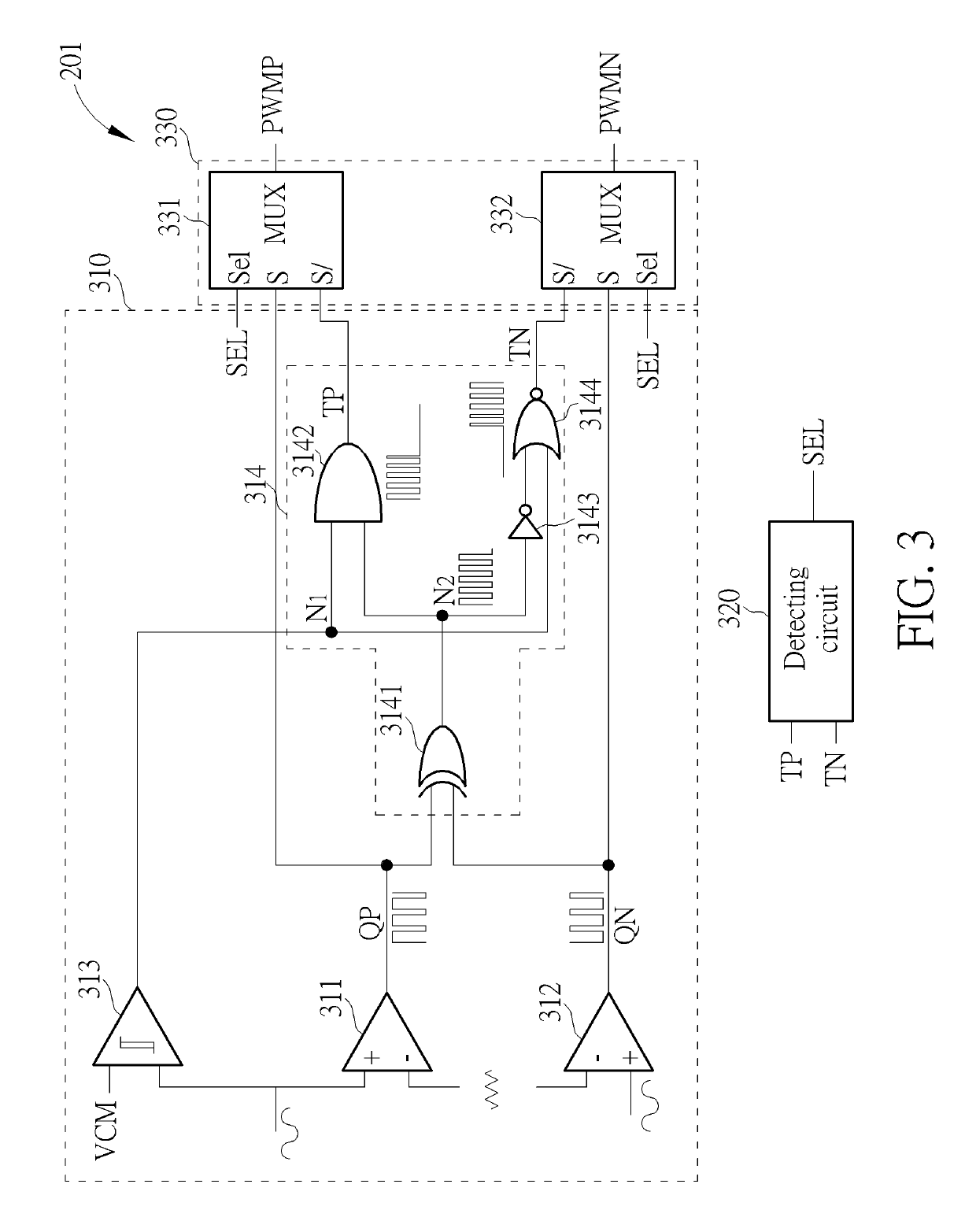

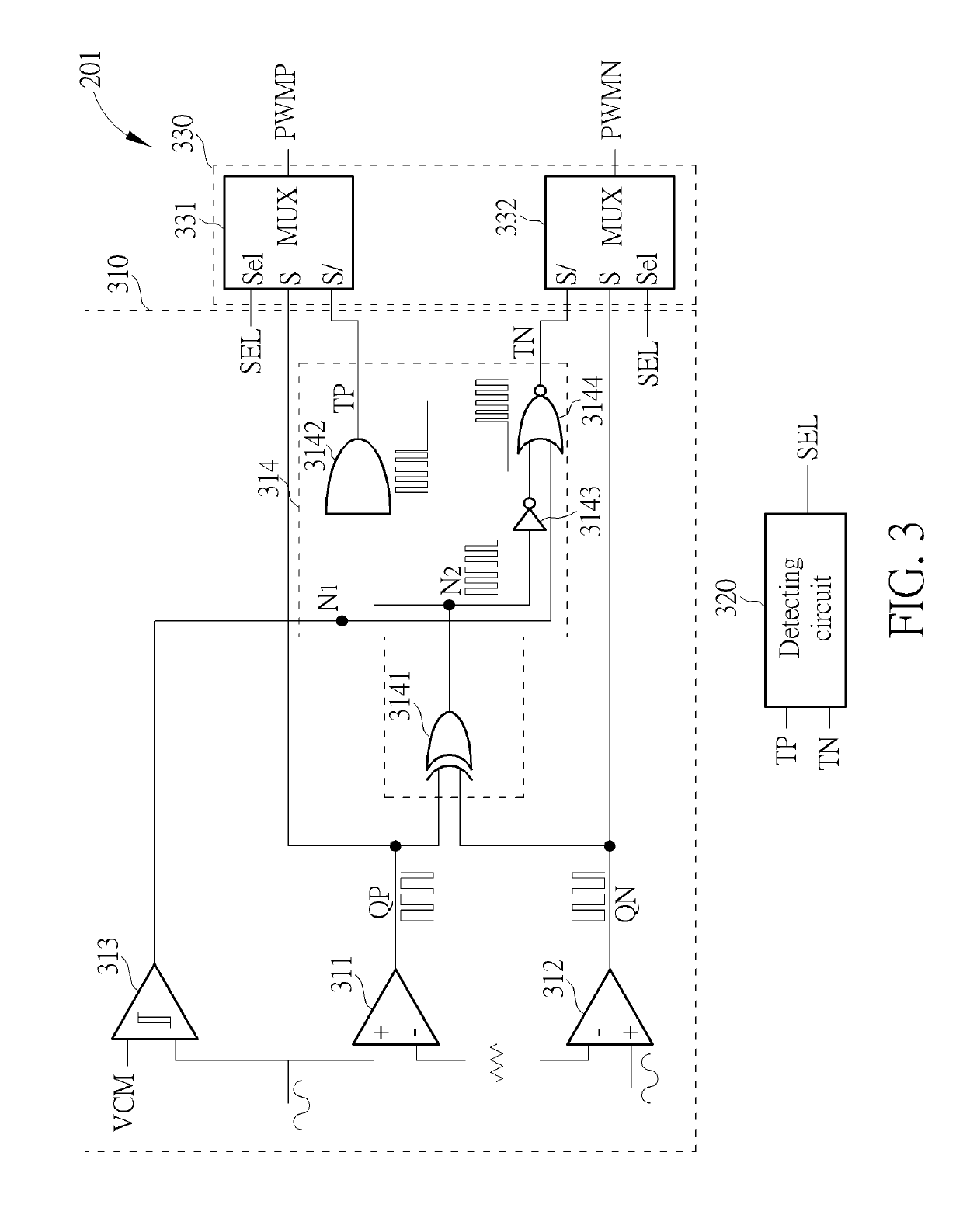

Quaternary/ternary modulation selecting circuit and associated method

ActiveUS10404227B1Amplifier modifications to reduce non-linear distortionMultiple input and output pulse circuitsAudio power amplifierEngineering

A quaternary / ternary modulation selecting circuit of an amplifier includes: a signal generating circuit, a detecting circuit, and a selecting circuit. The signal generating circuit is arranged to generate a ternary signal and a quaternary signal. The detecting circuit coupled to the signal generating circuit is arranged to generate a mode selecting signal according to at least the ternary signal. The selecting circuit coupled to the signal generating circuit and the detecting circuit is arranged to select and output one of the ternary signal and the quaternary signal to an output stage of the amplifier according to the mode selecting signal.

Owner:ELITE SEMICON MEMORY TECH INC

Pulse synthesizing circuit

ActiveUS9287867B2Improve versatilityEasily signalExclusive-OR circuitsMultistate logicEngineeringElectric potential energy

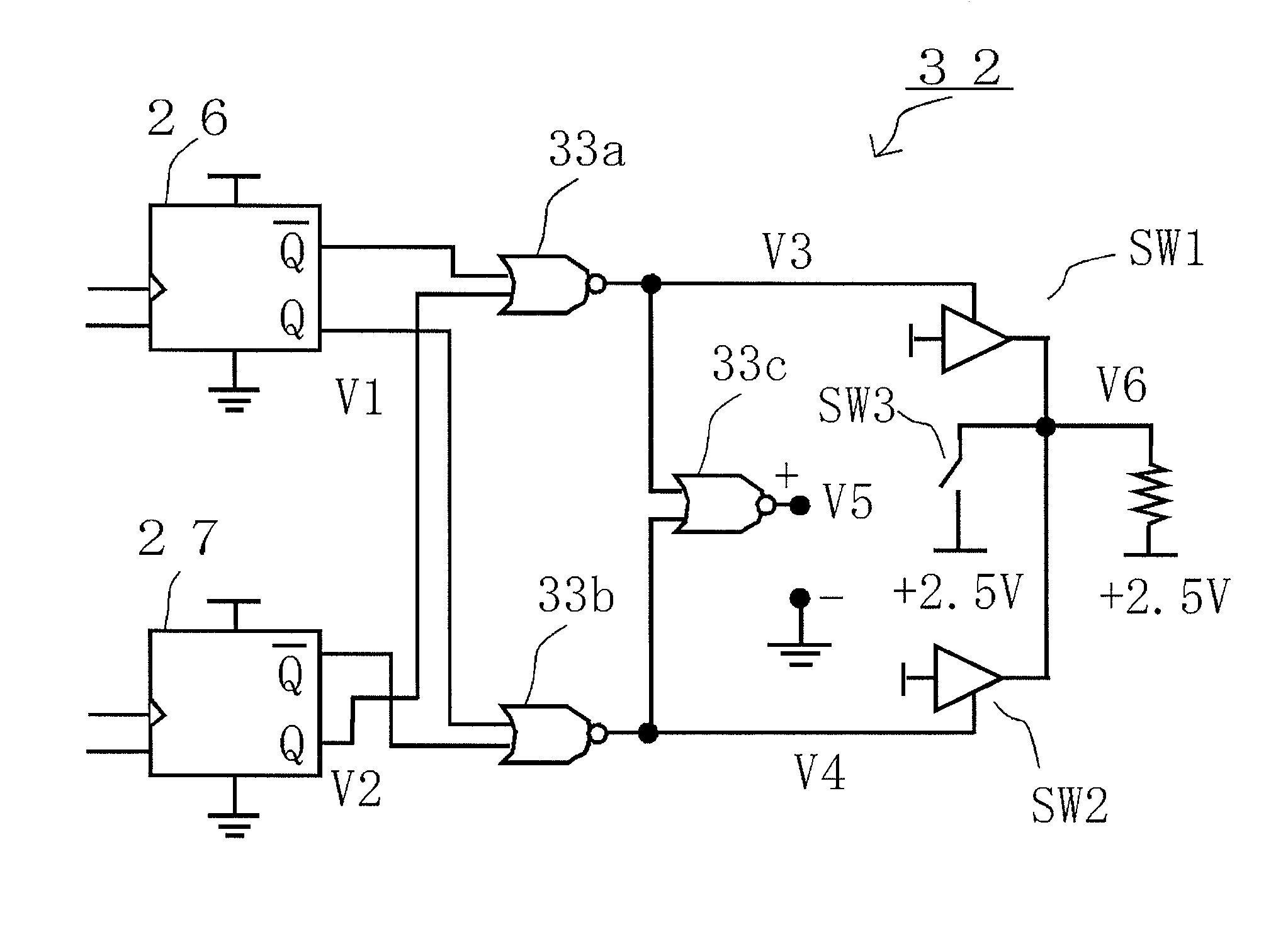

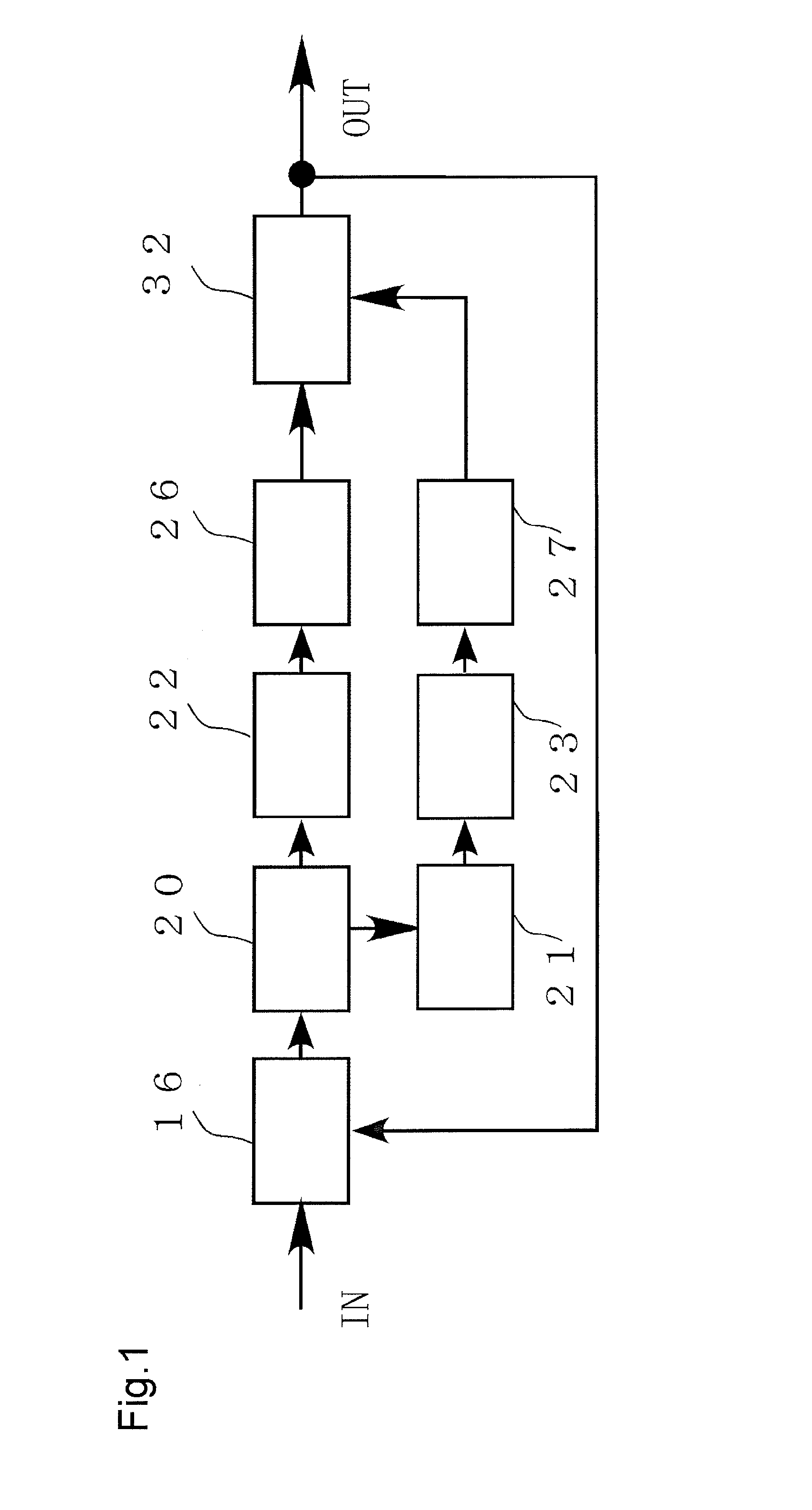

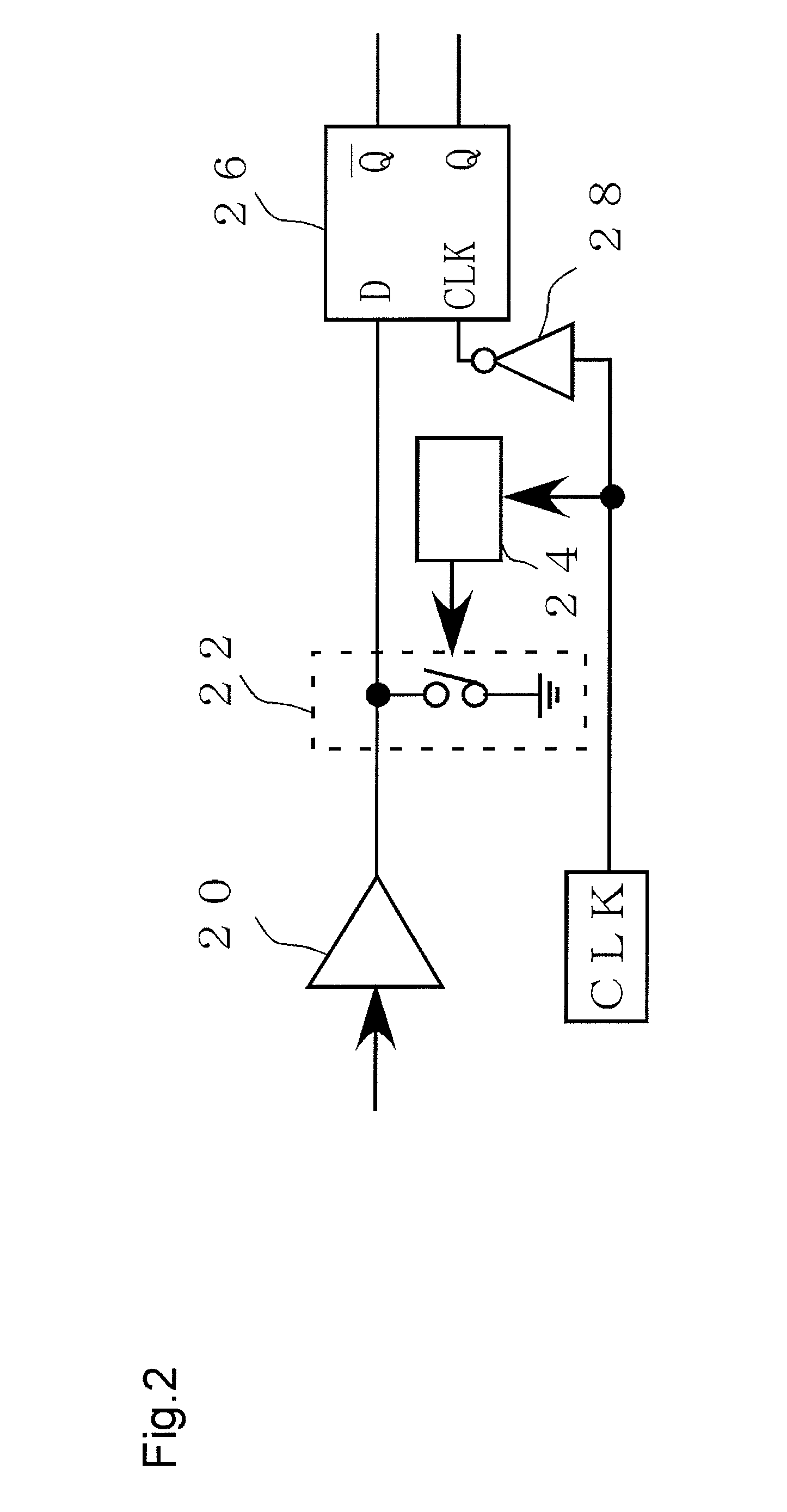

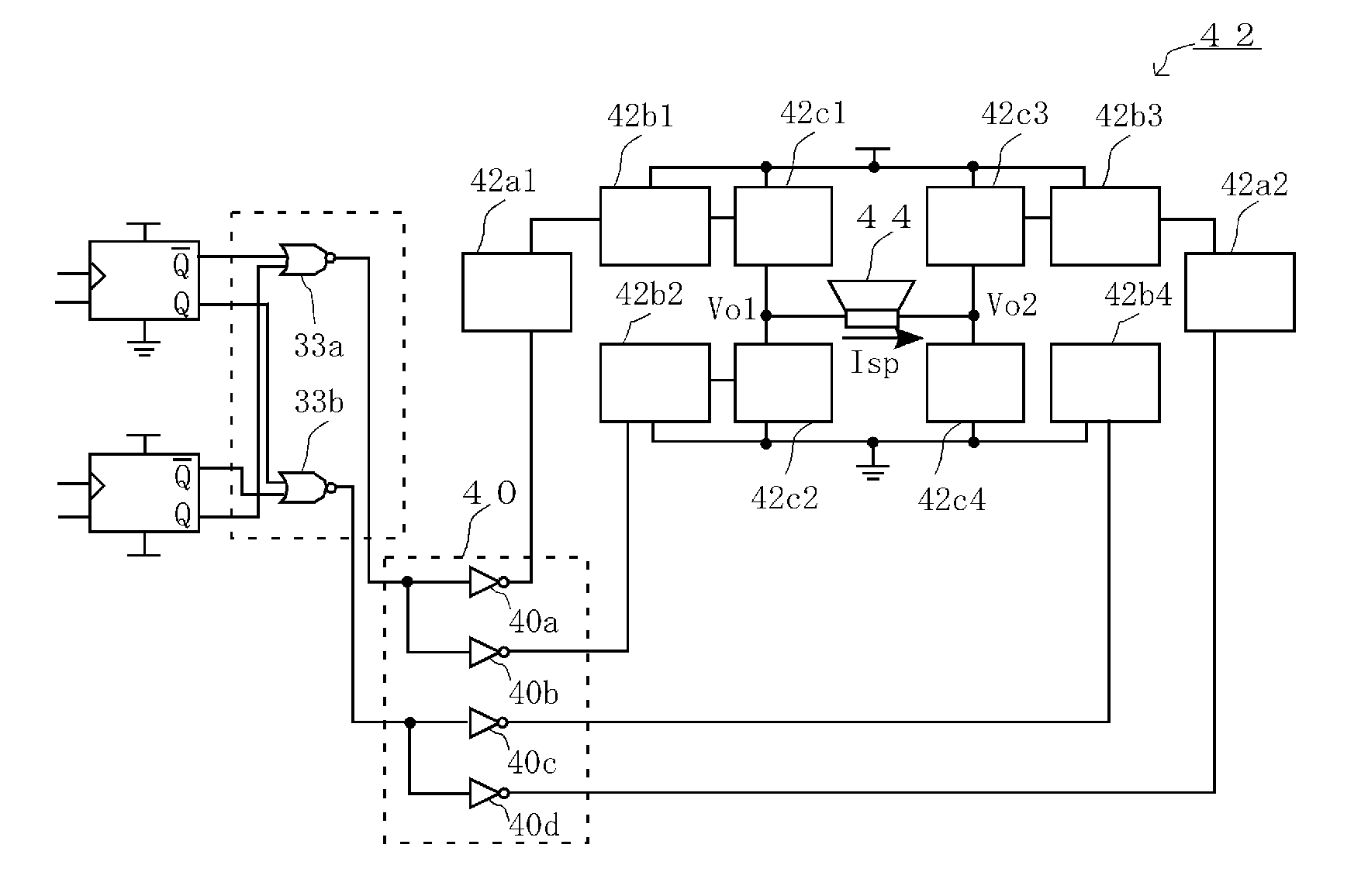

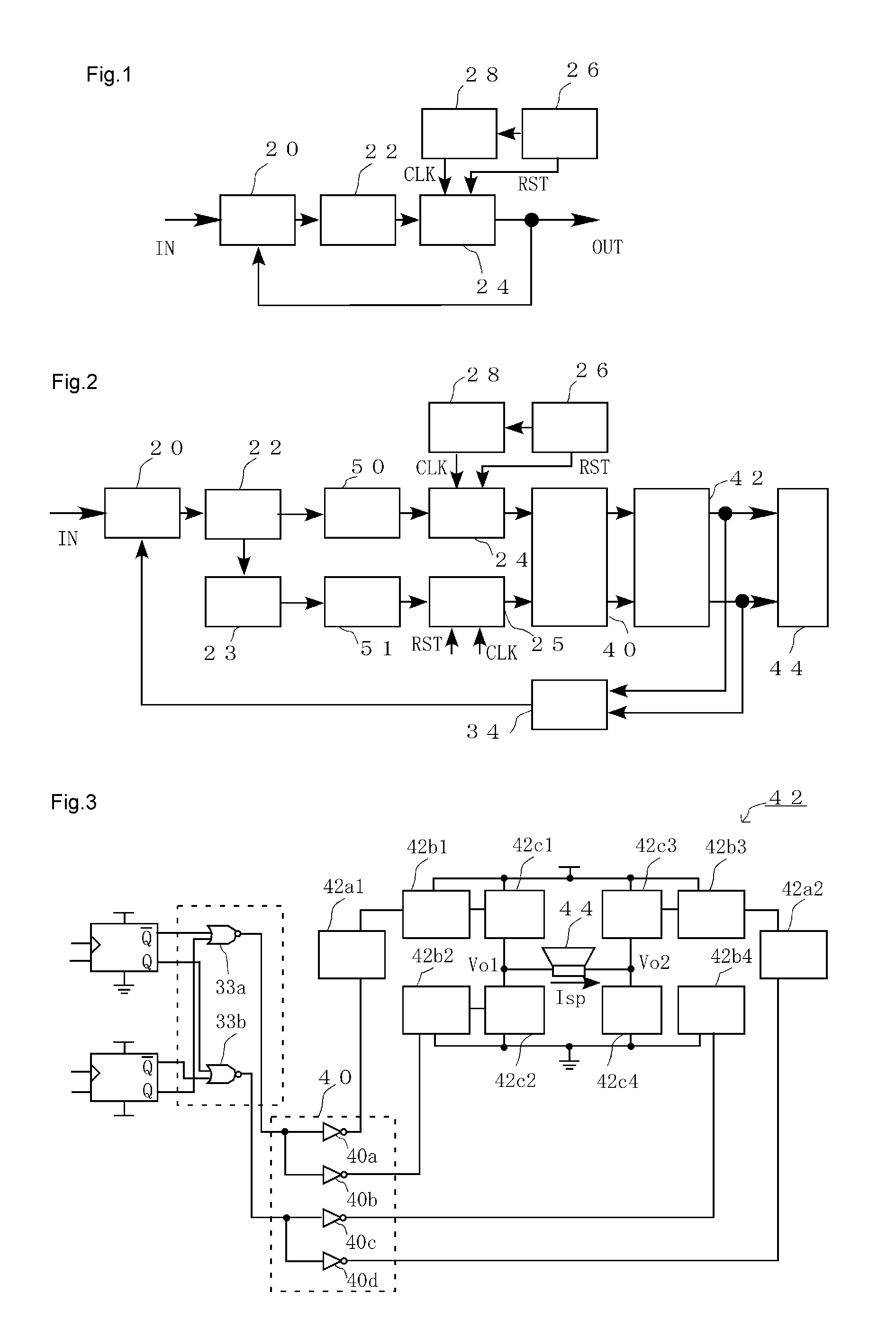

A circuit having versatility synthesizes one-bit digital signals to generate a ternary signal. The pulse synthesizing circuit synthesizes one-bit digital signals from two DFFs to generate a ternary signal. The pulse synthesizing circuit has a first NOR gate, a second NOR gate, a third NOR gate, and three switches. The first switch is connected to a first electric potential, the second switch is connected to a second electric potential, and the third switch is connected to a third electric potential. The first to third switches are turned on / off according to logical values of the signals from the two DFFs, and any of the first electric potential, the second electric potential, and the third electric potential is set as an output potential so that a ternary signal is generated.

Owner:ONKYO TECH KK

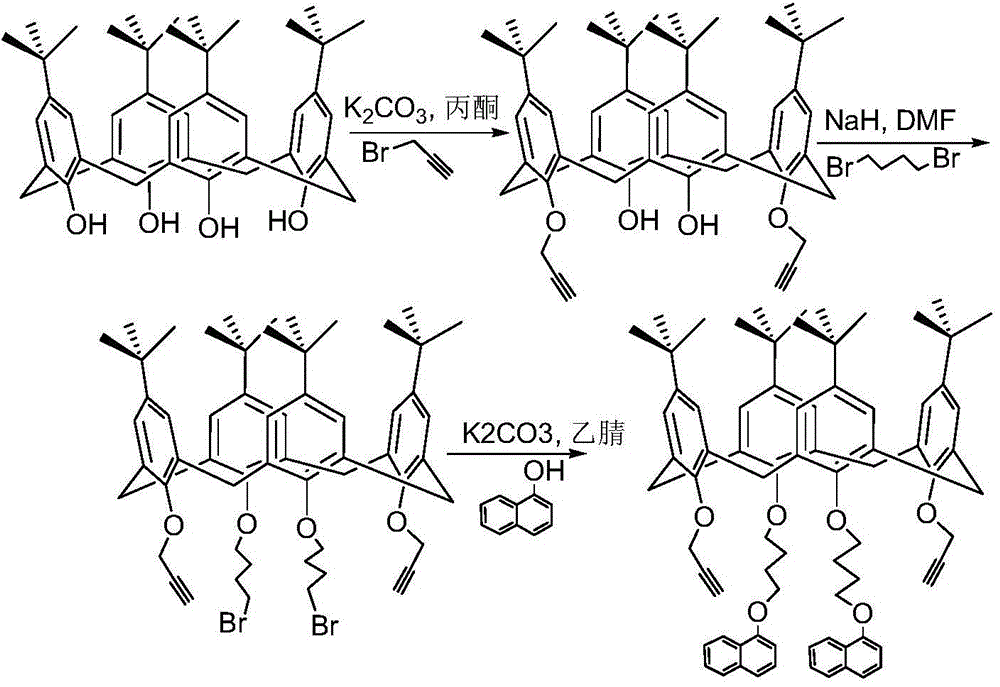

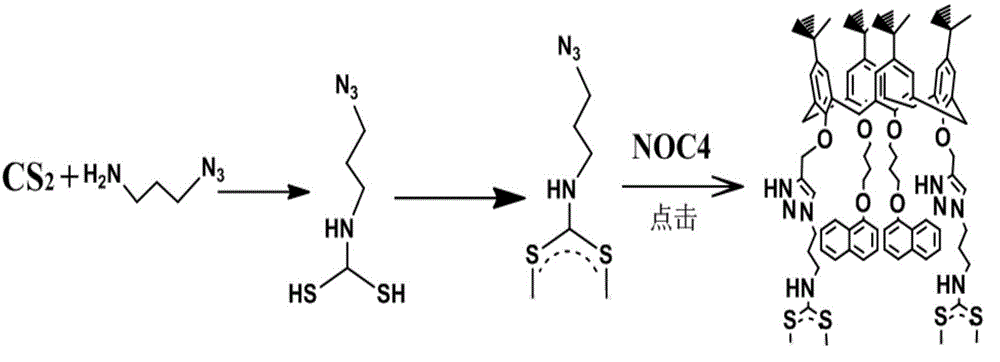

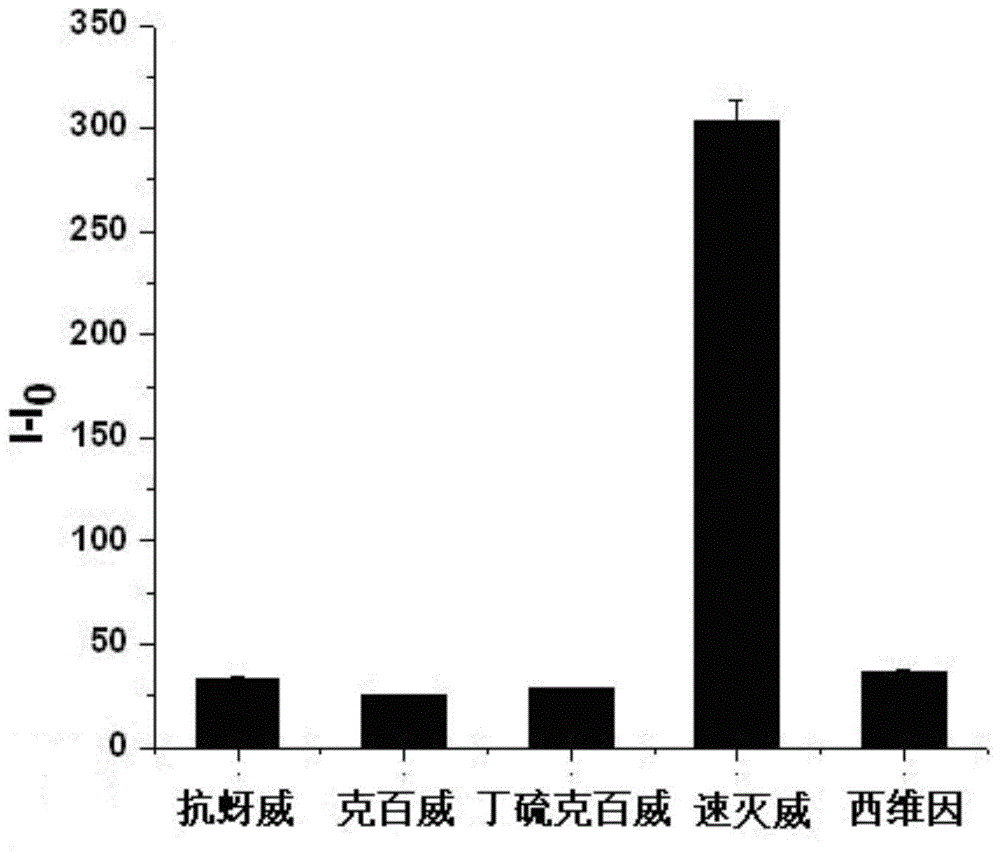

Meta-tolyl-N-methylcarbamate ternary signal sensing material as well as preparation method and application thereof

InactiveCN104865294APlay a role in enrichmentHigh detection sensitivitySurface/boundary effectFluorescence/phosphorescenceClick chemistrySodium hydride

The invention discloses a meta-tolyl-N-methylcarbamate ternary signal sensing material as well as a preparation method and application thereof, and belongs to the field of pesticide detection. The ternary signal sensing material adopts a dinaphthyl calix[4]arene modified gold interface, and is prepared by the method which comprises the following steps: using calix[4]arene as a raw material to be reacted with propargyl bromide and 1,2-dibromobutane respectively under the action of potassium carbonate and sodium hydride, and enabling the obtained product to be reacted with alpha-naphthol to obtain dinaphthyl calix[4]arene; modifying a gold material with an azide group, and then using a click chemistry method to modify the gold material with dinaphthyl calix[4]arene, so as to obtain the dinaphthyl calix[4]arene modified gold interface. Meta-tolyl-N-methylcarbamate can be detected by a fluorescent spectrometry with dinaphthyl calix[4]arene and can further be detected by an electrochemical impedance method and a contact angle method with the dinaphthyl calix[4]arene modified gold interface. Meta-tolyl-N-methylcarbamate is recognized by ternary signal output; the meta-tolyl-N-methylcarbamate ternary signal sensing material is reliable in result, high in sensitivity, reusable, and wide in application prospect in recognition and detection of pesticides.

Owner:HUAZHONG NORMAL UNIV

Circuit for generating ternary signal

InactiveUS7469016B2Low costMiniaturizationElectronic switchingElectric pulse generator circuitsControl signalInput control

A circuit for generating a ternary signal that receives a binary input-control signal and a binary reset signal and outputs a ternary signal. The circuit includes first to third transistors, each source terminal thereof is respectively connected to the three power supplies, and a sequential circuit that outputs control signals controlling the transistors. The sequential circuit outputs control signals that make the first and the third transistors be switched in a complementary manner in an initial state, and make the second and the third transistors be switched in a state that it is released from the initial state.

Owner:COLLABO INNOVATIONS INC

Quaternary/ternary modulation selecting circuit and associated method

ActiveUS20190288652A1Amplifier modifications to reduce non-linear distortionMultiple input and output pulse circuitsAudio power amplifierEngineering

A quaternary / ternary modulation selecting circuit of an amplifier includes: a signal generating circuit, a detecting circuit, and a selecting circuit. The signal generating circuit is arranged to generate a ternary signal and a quaternary signal. The detecting circuit coupled to the signal generating circuit is arranged to generate a mode selecting signal according to at least the ternary signal. The selecting circuit coupled to the signal generating circuit and the detecting circuit is arranged to select and output one of the ternary signal and the quaternary signal to an output stage of the amplifier according to the mode selecting signal.

Owner:ELITE SEMICON MEMORY TECH INC

Signal modulation circuit

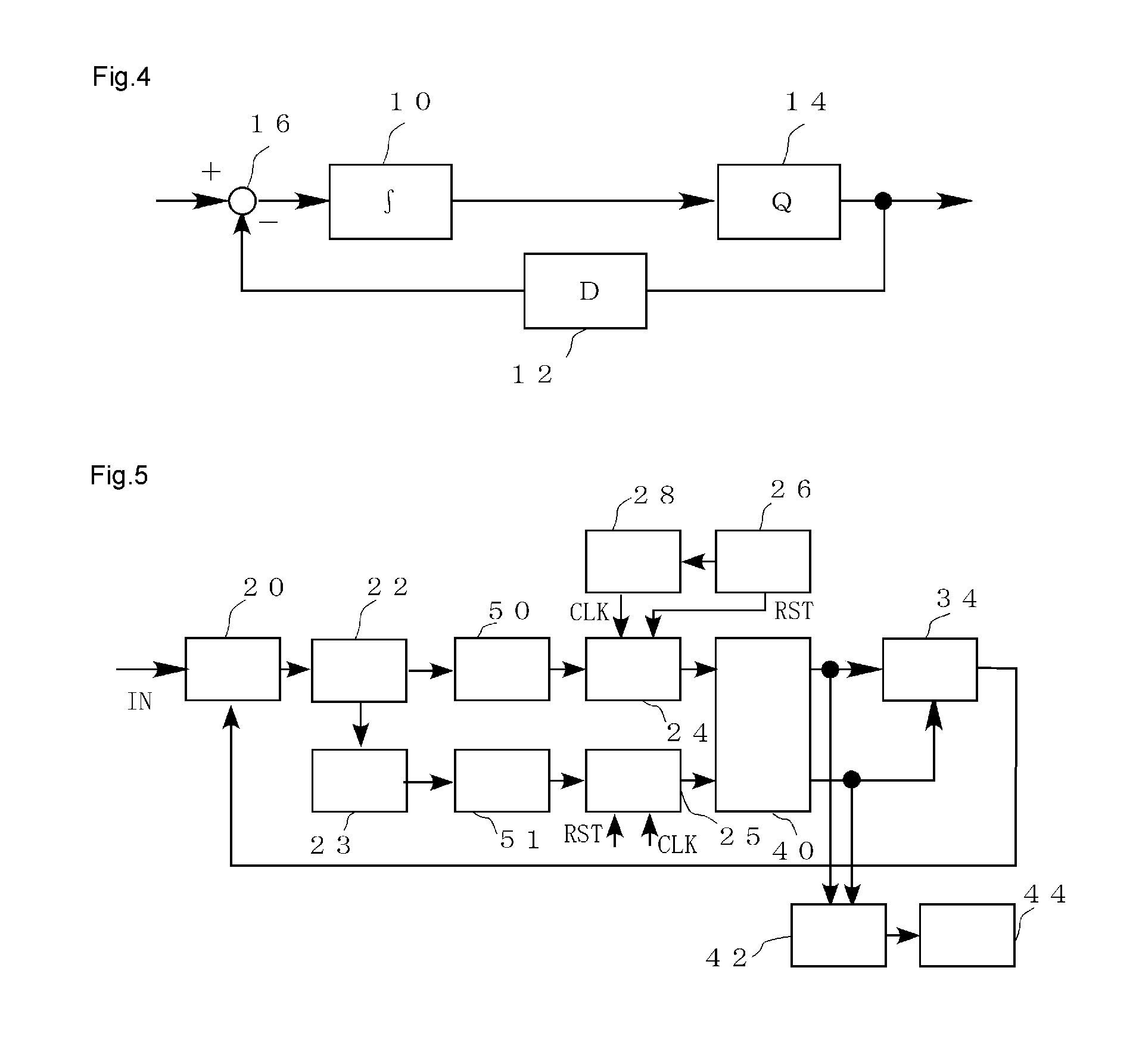

ActiveUS20150207519A1Reduce the impactReduce distortion problemsAnalogue conversionDriver circuitIntegrator

Provided is a circuit which can correct an output state in real time and reduce influences of distortion / noise components generated by a delay device. A signal modulation circuit includes a subtractor, an integrator, a phase inverting circuit, a DFF for while inserting a zero level at timing synchronous with the clock signal, delaying and quantizing the signal, a ternary signal generating circuit for generating a ternary signal for selectively driving a load connected to a single power supply into ternary conductive states including a positive current on-state, a negative current on-state, and an off-state, a driver circuit for generating a driving signal for driving a load, and a feedback circuit for feeding back the driving signal from the driver circuit to the input signal.

Owner:ONKYO KK

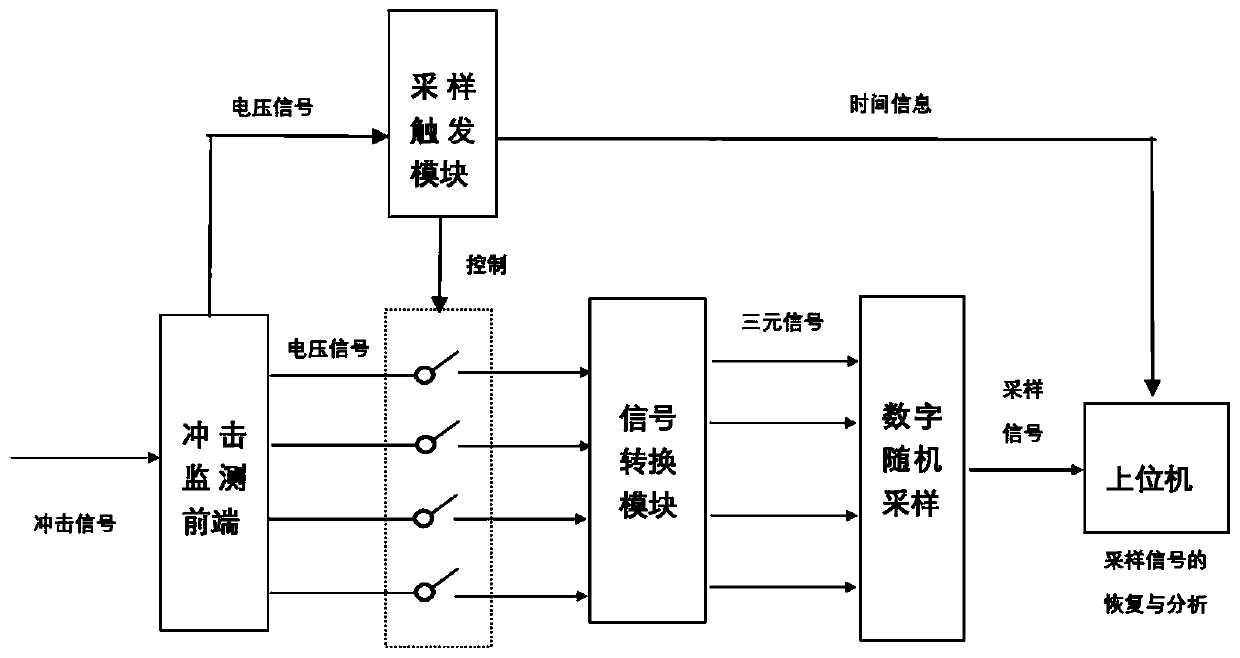

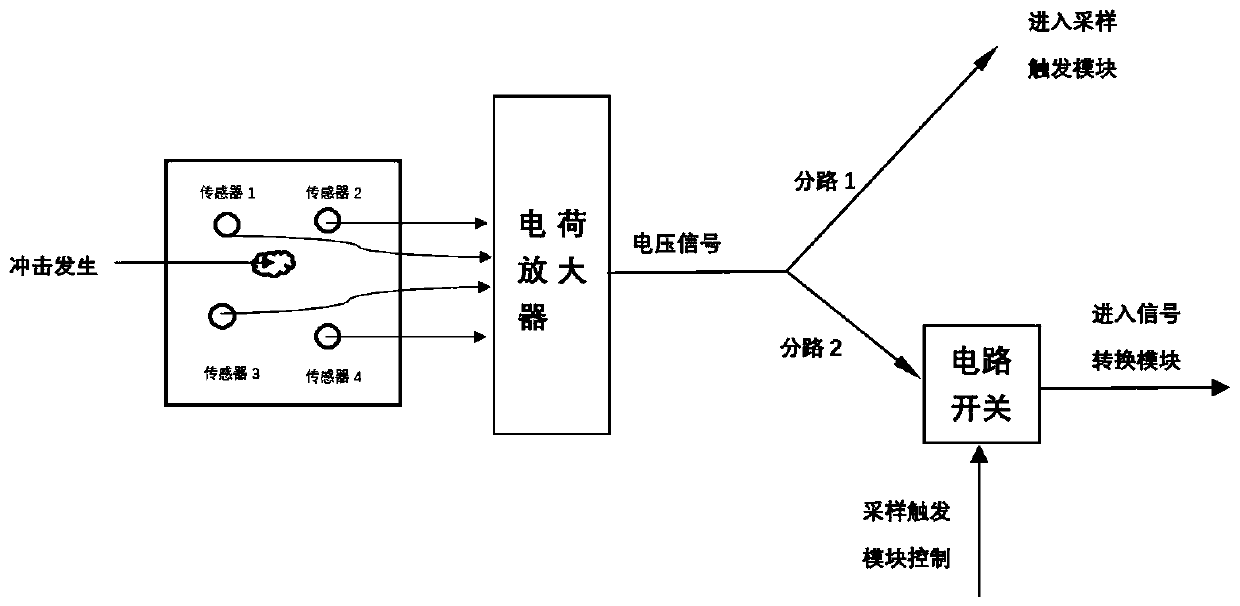

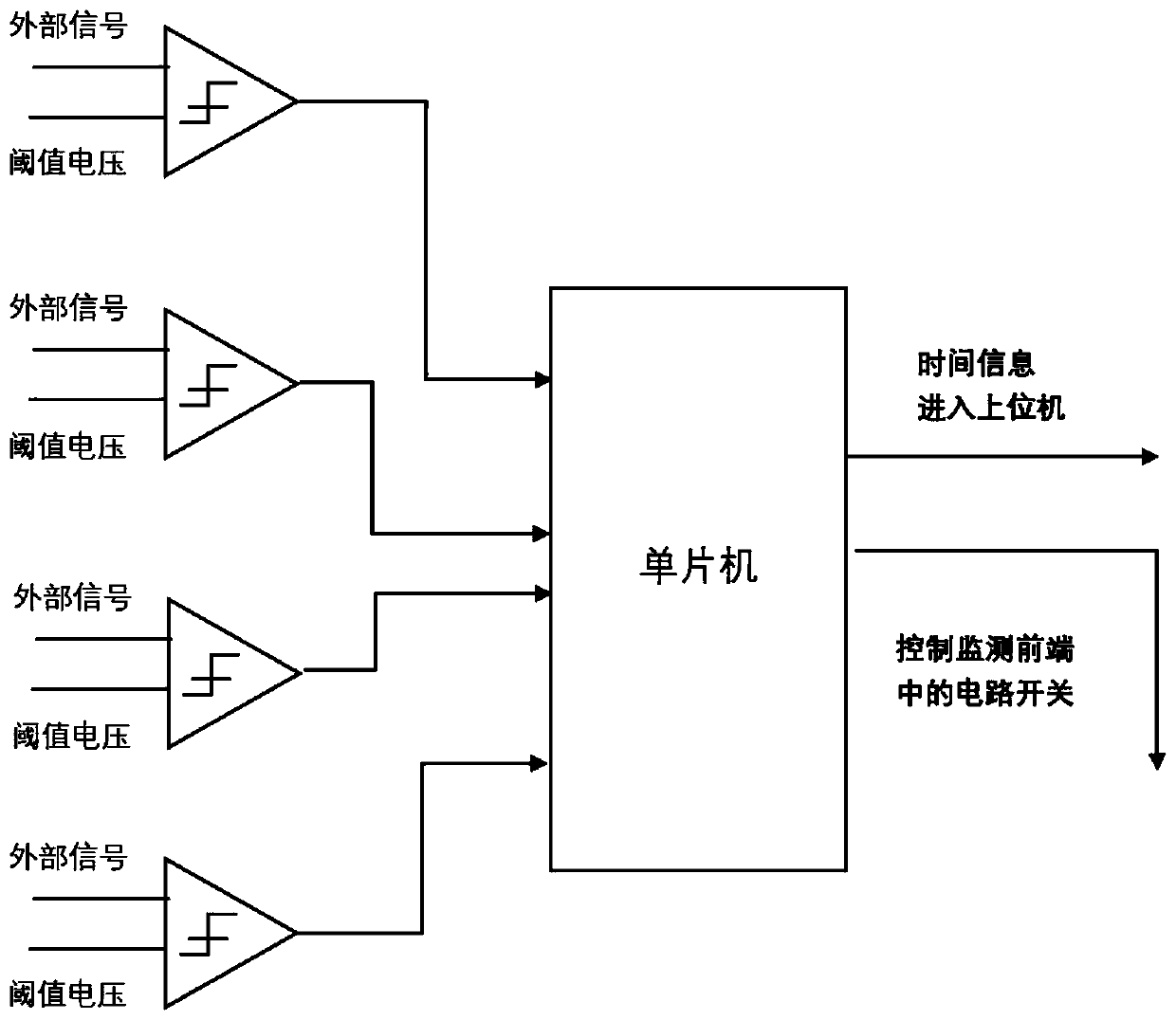

Impact monitoring system using digital random demodulation and split recovery algorithm

ActiveCN110686846ARealize real-time monitoringGuaranteed real-time monitoringCode conversionForce measurement using piezo-electric devicesAlgorithmAnalog signal

The invention proposes an impact monitoring system using a digital random demodulation and split recovery algorithm, and the system comprises an impact monitoring front end, a sampling trigger module,a signal conversion module, a digital random sampler, a host computer and other modules, wherein the impact monitoring front end and the sampling trigger module realize the real-time monitoring of animpact signal, and record the required information for the processing at the next layer structure; the signal conversion module converts the received voltage analog signal into a ternary signal basedon the level change of its amplitude and inputs the ternary signal into the digital random sampler; the digital random sampler performs compressed sampling on the ternary signal by digital random demodulation; and the upper computer implements algorithm recovery that can process the sampled signals in parallel, and accurately inverts the original impact signal waveform at high speed.

Owner:HOHAI UNIV CHANGZHOU