Semiconductor device formed on insulating layer and method of manufacturing the same

a technology of semiconductor devices and insulating layers, applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of affecting the manufacturing process, the transistor is turned, and the disadvantage of the proposed manufacturing process, and achieve the effect of easy manufacturing of semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

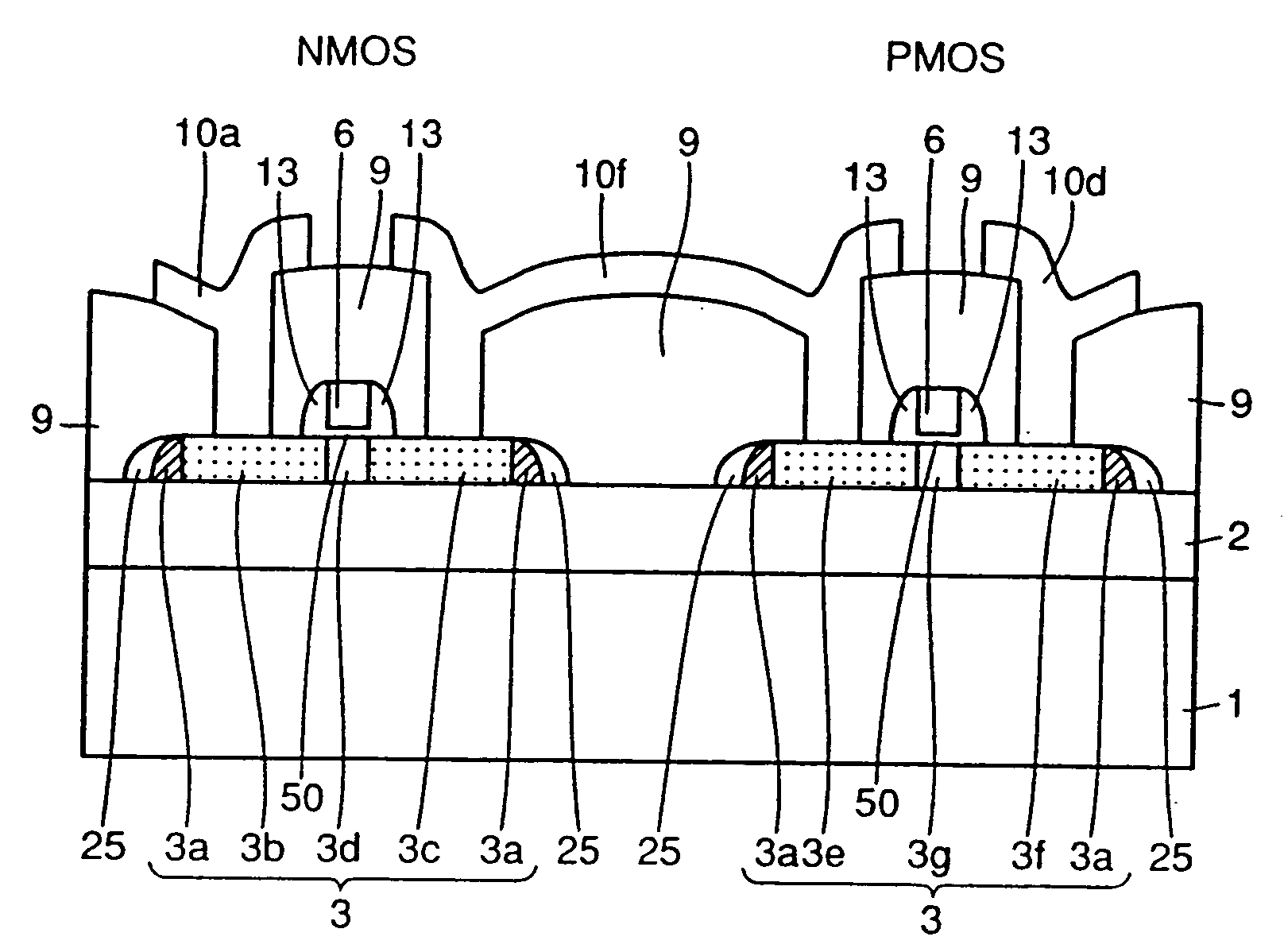

first embodiment

[0151] In this first embodiment, upper side portions of each SOI layer 3 are rounded. Thereby, it is possible to prevent concentration of an electric field at the upper side portions of SOI layers 3. Consequently, lowering of a threshold voltage of a parasitic transistor can be prevented, which suppresses turn-on of the parasitic transistor. As a result, subthreshold characteristics of a regular MOS transistor are prevented from being adversely affected by the parasitic transistor. The lower portion of the side surface of SOI layer 3 extends substantially perpendicularly to a main surface of the buried oxide film 2, so that such a structure can be prevented that a thin portion is formed at the lower side portion of SOI layer 3. Thereby, it is possible to prevent lowering of the threshold voltage of parasitic transistor which may be caused by reduction of the thickness of SOI layer 3 at the vicinity of its side surface.

[0152] In this first embodiment, buried oxide film 2 is provided ...

second embodiment

[0170] Referring to FIGS. 24 to 32, a process of manufacturing the semiconductor device of the second embodiment will be described below.

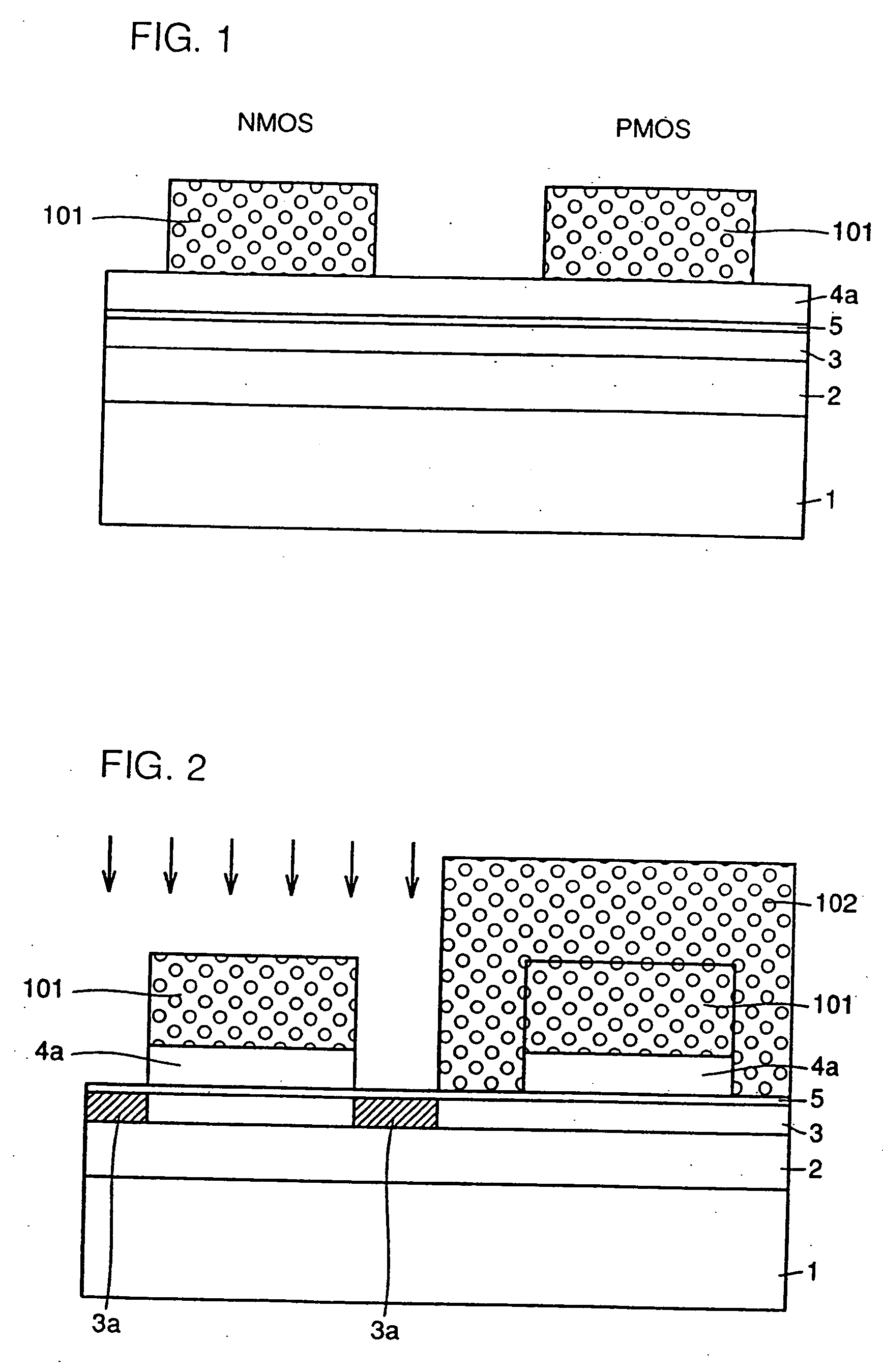

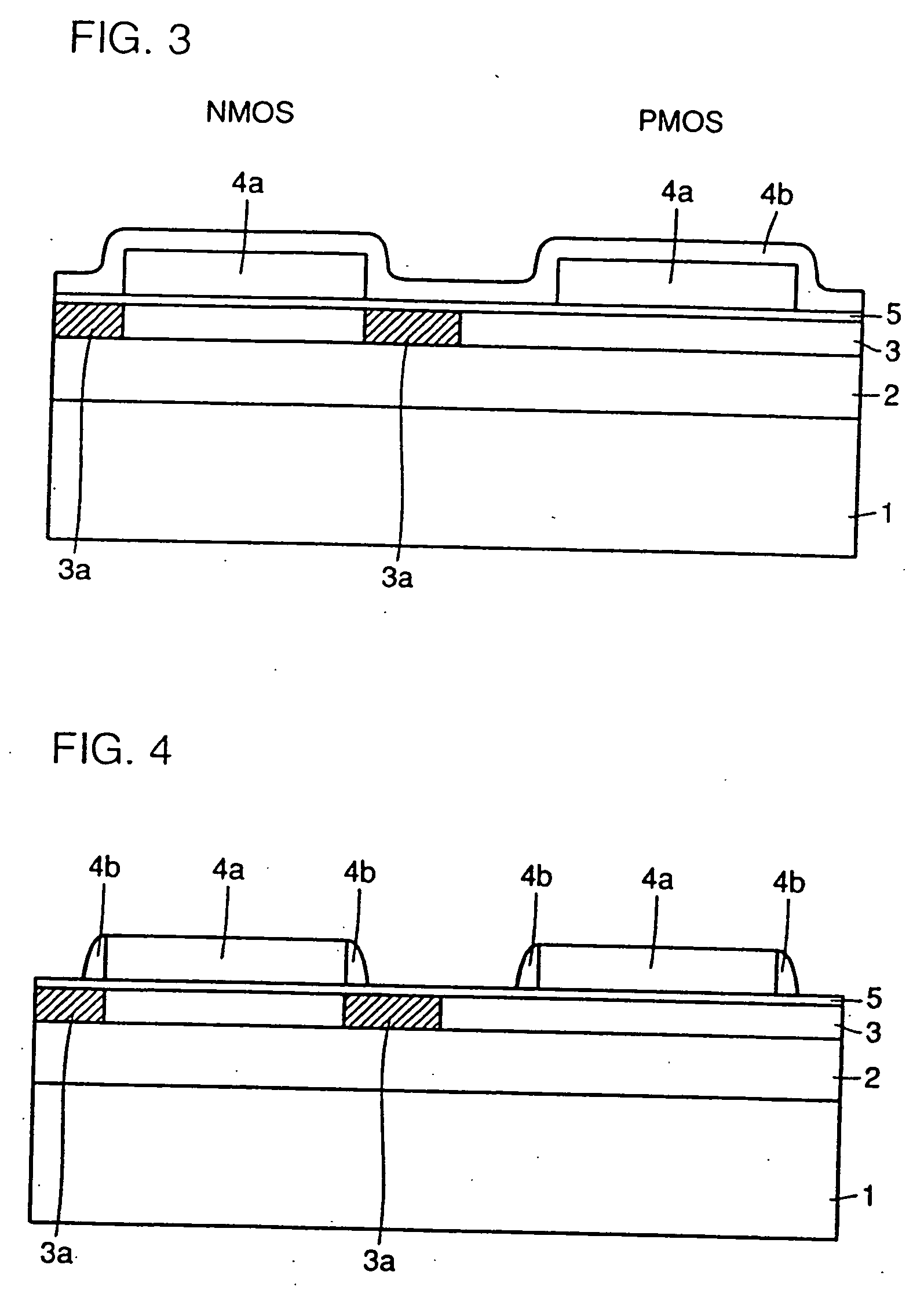

[0171] Referring first to FIG. 24, buried oxide film 2 is formed on silicon substrate 1, and then SOI layer 3 is formed on buried oxide film 2. Oxide film 5 having a thickness of about 100 Å is formed on SOI layer 3. Oxide film 5 may be formed by the CVD method under the temperature condition of about 800° C., or by oxidizing the surface of SOI layer 3 under the temperature condition of about 800° C. Nitride film 4a having a thickness of about 1000 Å is formed on oxide film 5 by the CVD method under the temperature condition of about 700° C. A resist 101 is formed at predetermined regions on nitride film 4a. Using resist 101 as a mask, nitride film 4a is etched to pattern the same.

[0172] Then, resist 102 covering the PMOS region is formed as shown in FIG. 25. Using resists 102 and 101 as a mask, boron ions (B+) are implanted into SOI layer 3 at th...

fourth embodiment

[0178] Referring to FIGS. 47 and 48, a semiconductor device of a fourth embodiment is provided with thermal oxidation films 5a covering side surfaces of SOI layer 3. There are formed oxide films 16 which are in contact with side surfaces of thermal oxidation films 5a and cover end surfaces of concavities 2b in buried oxide film 2. Thereby, it is possible to prevent such a disadvantage that gate electrode 6 extends up to the lower surface of SOI layer 3 due to formation of gate electrode 6 at the end of concavity 2b during the manufacturing process. As a result, it is possible to prevent concentration of an electric field which may be caused by the above extension of gate electrode 6.

[0179] Referring to FIGS. 40 to 47, a process of manufacturing the semiconductor device of the fourth embodiment will be described below. Referring to FIG. 40, buried oxide film 2 is formed on silicon substrate 1, and then SOI layer 3 is formed on buried oxide film 2. Oxide film 5 is formed on SOI layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More