Wafer packing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

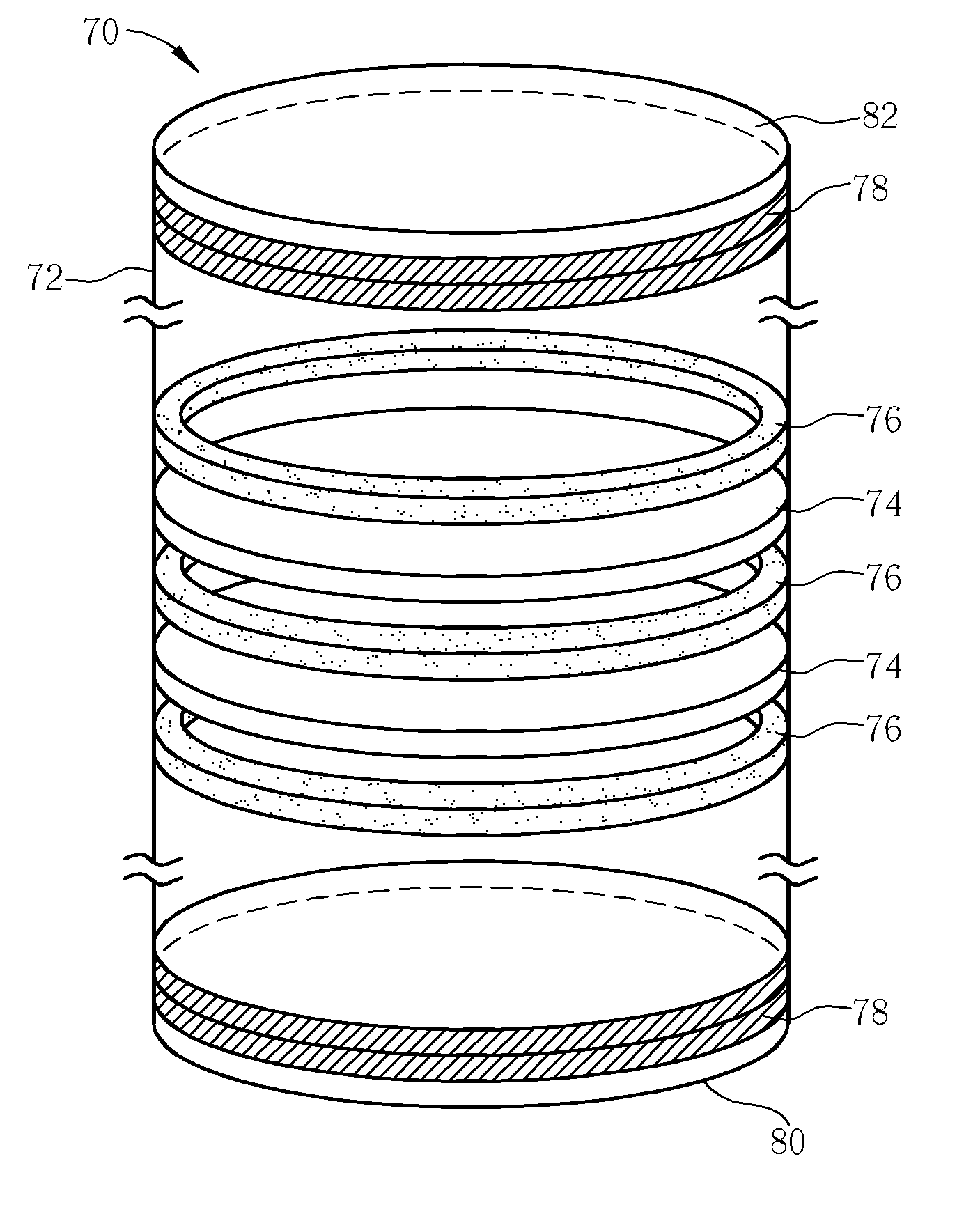

[0015] Please refer to FIG. 4 that is a schematic diagram of a wafer packing 70 according to the present invention. The wafer packing 70 includes a cassette 72, at least two sponges 78, and a plurality of hollow support pads 76 for depositing a plurality of wafers 74. First, at least one of the sponges 78 is put on a bottom of the cassette 72, and at least one hollow support pad 76 and a wafer 74 are alternately put on the sponges 78. Other hollow support pads 76 and other wafers 74 are continuously and repeatedly stacked in alternation on the bottom wafer 74 until the cassette is filled with 25 wafers 74, although this quantity is not limiting as other quantities are equally possible. Then, a lid 82 of the cassette 72 covers and completes the batch of wafer packing 70. A quantity of wafer packings 70 is stored in a carton (not shown) for shipment. In addition, the hollow support pads 76 touch a non-complete wafer area of the wafers 74, so the complete wafer area of the wafers 74 ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More