High density integrated circuit apparatus, test probe and methods of use thereof

a technology of integrated circuits and test probes, which is applied in the direction of soldering apparatus, instruments, and semiconductor/solid-state device details, etc., can solve the problems of high cost of fabrication of integrated circuit probes, easy damage of wires, so as to achieve high-performance functional testing and high temperature burn

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

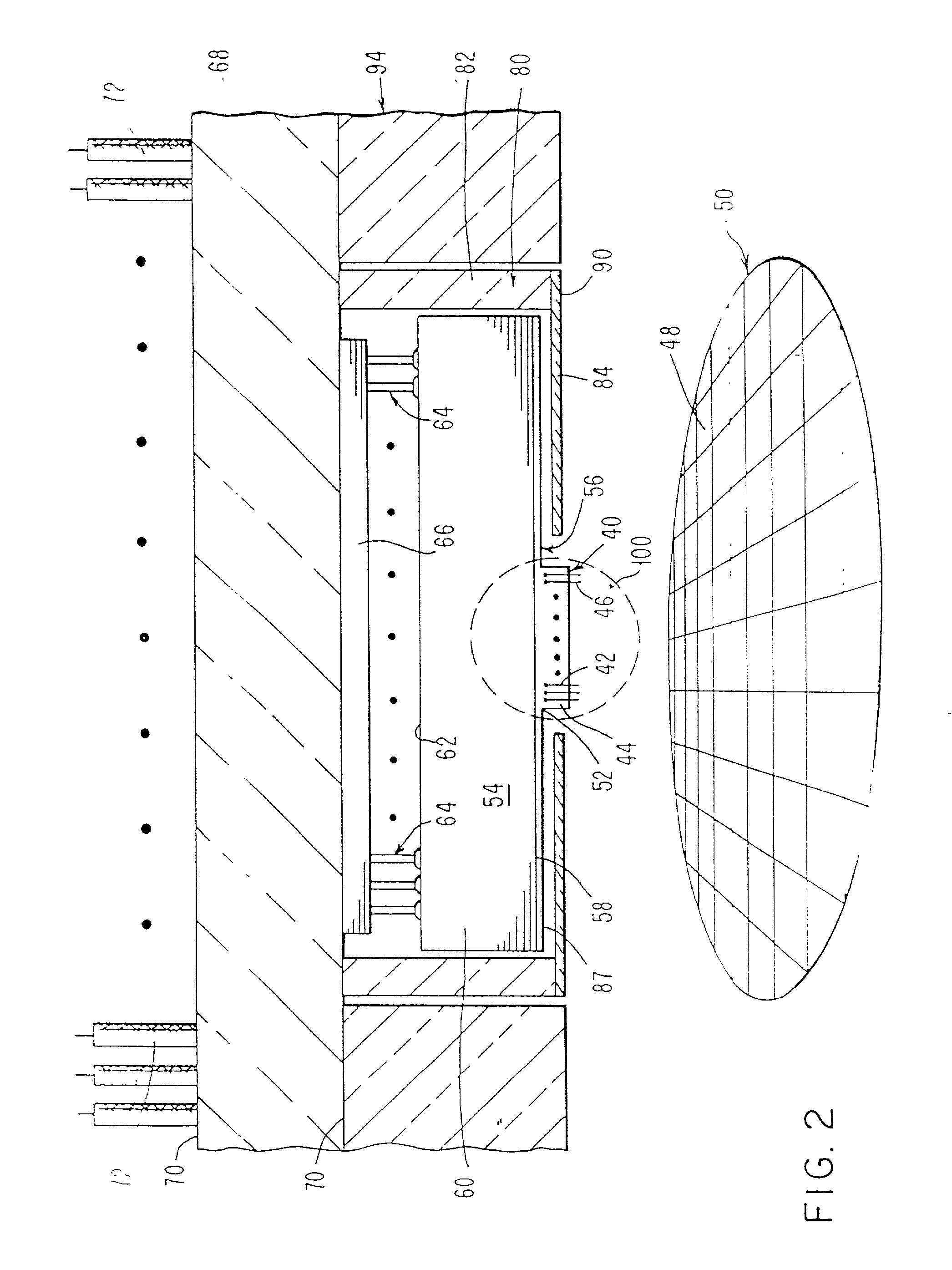

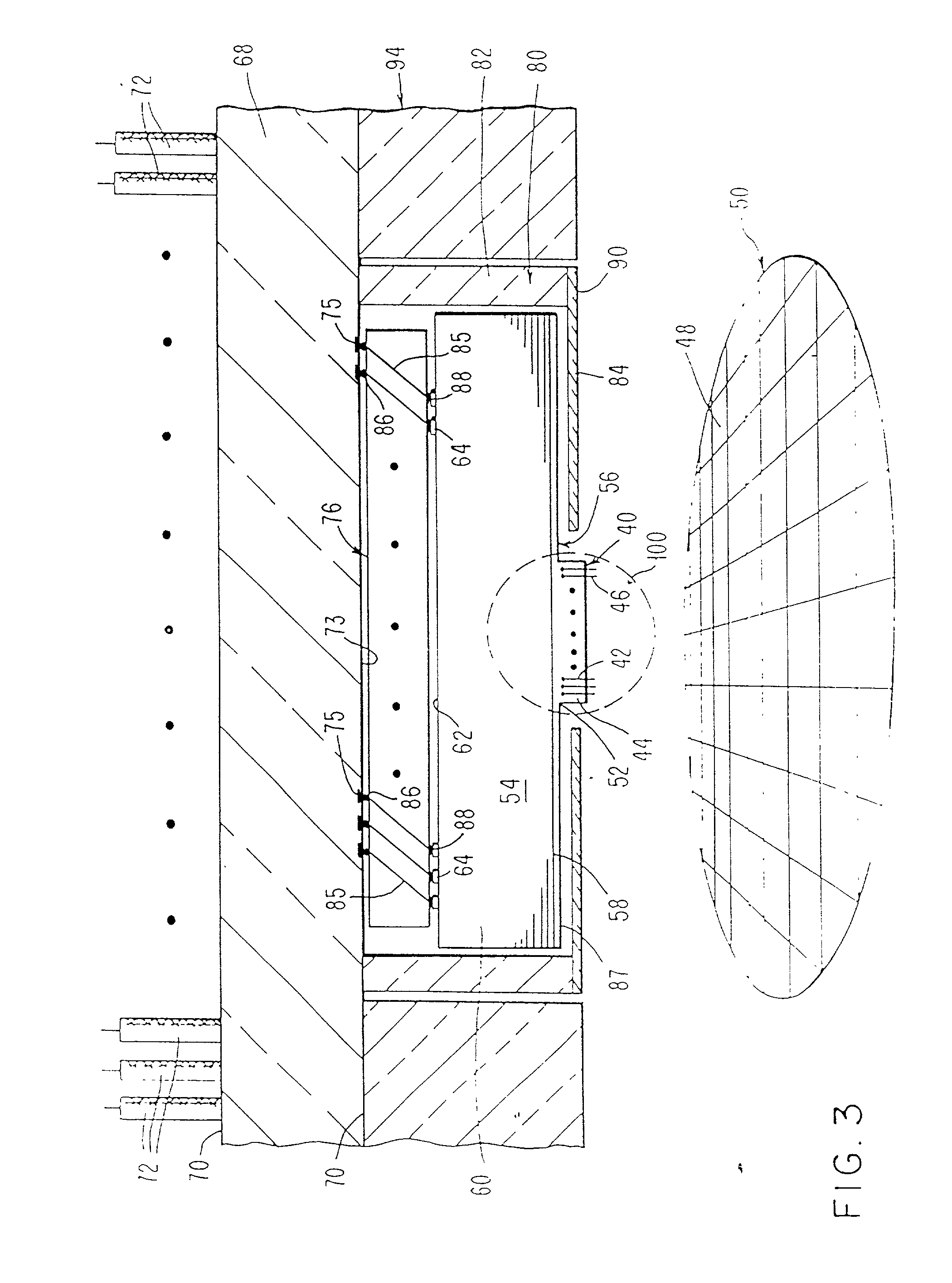

[0033] Turning now to the figures, FIGS. 2 and 3 show two embodiments of the test assembly according to the present invention. Numerals common between FIGS. 2 and 3 represent the same thing. Probe head 40 is formed from a plurality of elongated electrically conducting members 42 embedded in a material 44 which is preferably an elastomeric material 44. The elongated conducting members 42 have ends 46 for probing contact locations on integrated circuit devices 48 of wafer 50. In the preferred embodiment, the workpiece is an integrated circuit such as a semiconductor chip or a semiconductor wafer having a plurality of chips. The workpiece can be any other electronic device. The opposite ends 52 of elongated electrical conductors 42 are in electrical contact with space transformer (or fan-out substrate) 54. In the preferred embodiment, space transformer 54 is a multilevel metal / ceramic substrate, a multilevel metal / polymer substrate or a printed circuit board which are typically used as...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Temperature | aaaaa | aaaaa |

| Elastomeric | aaaaa | aaaaa |

| Density | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More