Chip-scale package

a chip-scale and package technology, applied in the field of semiconductor package, can solve the problems of poor poor distribution of the build-up dielectric layer, etc., and achieve the effect of improving the reliability of the chip-scale packag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

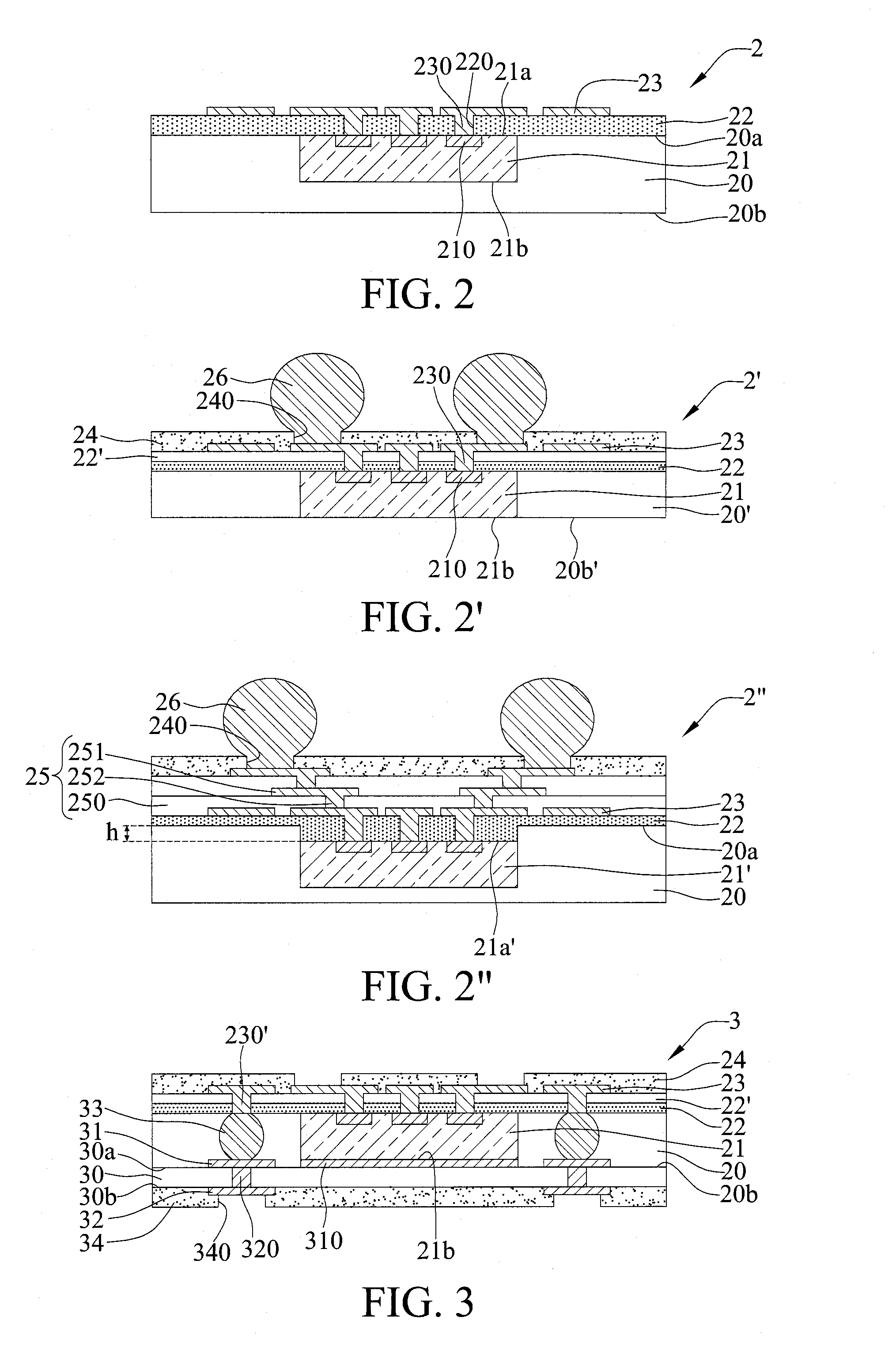

[0025]Referring to FIG. 2, a chip-scale package 2 of a first embodiment is shown according to the present invention. The chip-scale package 2 comprises an encapsulating layer 20 having a first surface 20a and a second surface 20b opposing the first surface 20a, at least one chip 21 embedded into the first surface 20a of the encapsulating layer 20 and exposed from the first surface 20a of the encapsulating layer 20, a buffering dielectric layer 22 formed on the first surface 20a of the encapsulating layer 20 and the chip 21, and a circuit layer 23 formed on the buffering dielectric layer.

[0026]The encapsulating layer 20 may be made of packaging resin or soft material. In the first embodiment, the soft material is Ajinomoto build-up film (ABF), bismaleimide-triacine (BT), polyimide (PI), polymerized siloxanes (silicone) or epoxy resin.

[0027]The chip 21 has an inactive surface 21b and an active surface 21a opposing the inactive surface 21b and exposed from the first surface 20a of the ...

second embodiment

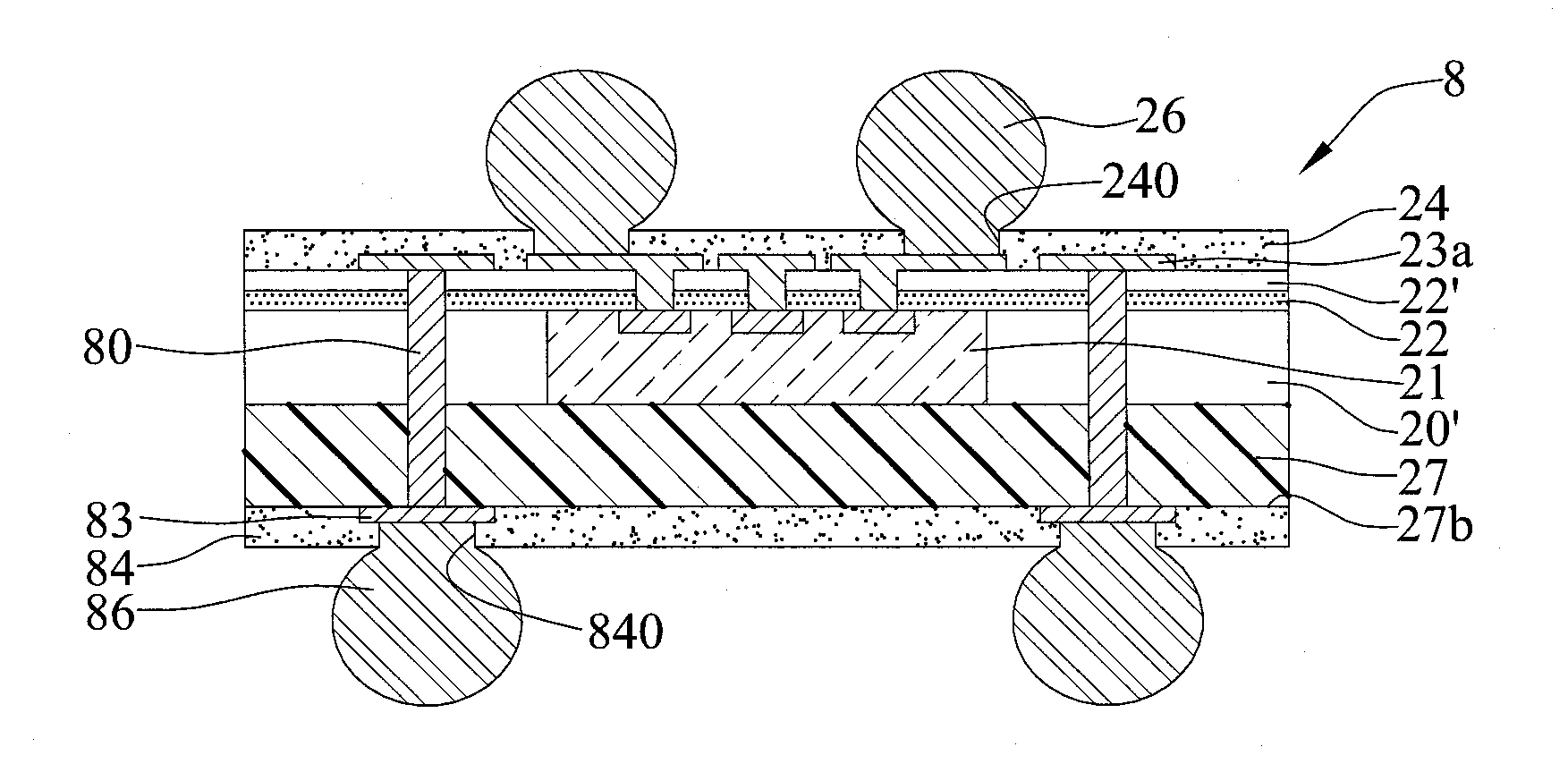

[0037]Referring to FIG. 3, the second embodiment differs from the first embodiment only in that a substrate 30 is further disposed in the second embodiment.

[0038]In the package 3, a substrate 30 is disposed on the second surface 20b of the encapsulating layer 20 and the inactive surface 21b of the chip 21.

[0039]The substrate 30 has a top surface 30a and a bottom surface 30b. Circuits 31 and 32 connected to each other are formed on the top surface 30a and the bottom surface 30b, respectively. The top surface 30a is attached to the second surface 20b of the encapsulating layer 20 and the inactive surface 21b of the chip 21. The circuit 31 on the top surface 30a is embedded into the encapsulating layer 20. A plurality of conductive elements 33 are disposed on the circuit 31 on the top surface 30a and electrically connected to the conductive blind vias 230′ of the circuit layer 23.

[0040]In the second embodiment, the circuits 31 and 32 are electrically connected to each other by conducti...

third embodiment

[0044]Referring to FIGS. 4 and 4′ the third embodiment differs from the first embodiment only in that conductive bumps 40 and 40′ are further disposed in the chip-scale package of the third embodiment.

[0045]In the package 4, 4′, conductive bumps 40, 40′ are disposed in the encapsulating layer 20. The conductive bumps 40, 40′ have top ends combined with the buffering dielectric layer 22 and bottom ends exposed from the second surface 20b, 20b′ of the encapsulating layer 20, 20′, to further combine with conductive elements (e.g., metal wire, solder, solder balls) 46. The circuit layer 23 is electrically connected through the conductive blind vias 230′ to the top ends of the conductive bumps 40, 40′.

[0046]In the fourth embodiment, the conductive bumps 40, 40′ are made of copper.

[0047]As shown in FIG. 4, a metal layer 41 is formed on the bottom ends of the conductive bumps 40, for the conductive elements 46 to be coupled therewith.

[0048]The bottom ends of the conductive bumps 40 are exp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More