Volatile Memory with a Decreased Consumption and an Improved Storage Capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

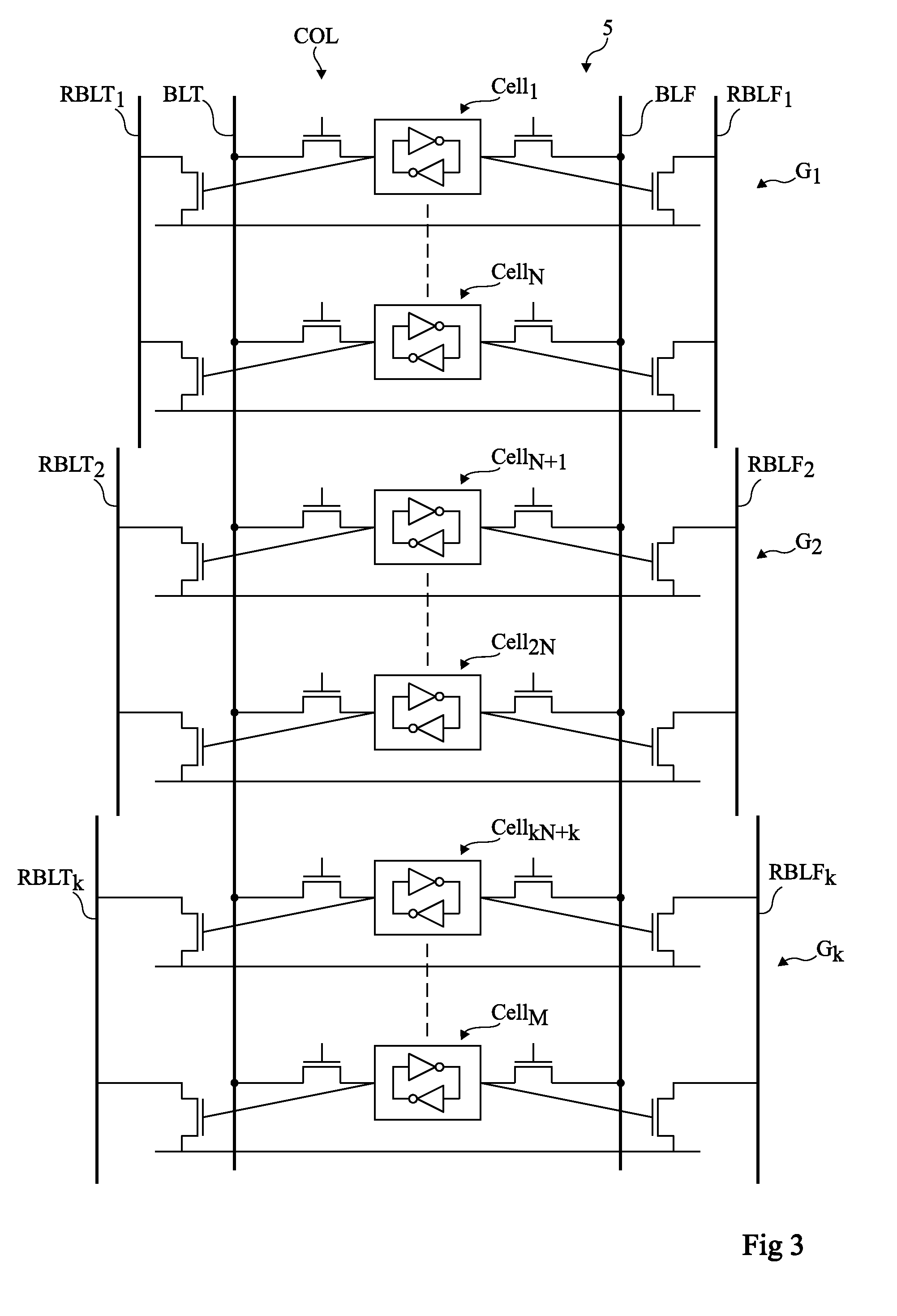

[0051]For clarity, the same elements have been designated with the same reference numerals in the different drawings. In the following description, expression “conduction terminal” of a MOS transistor indifferently designates the MOS transistor source or drain.

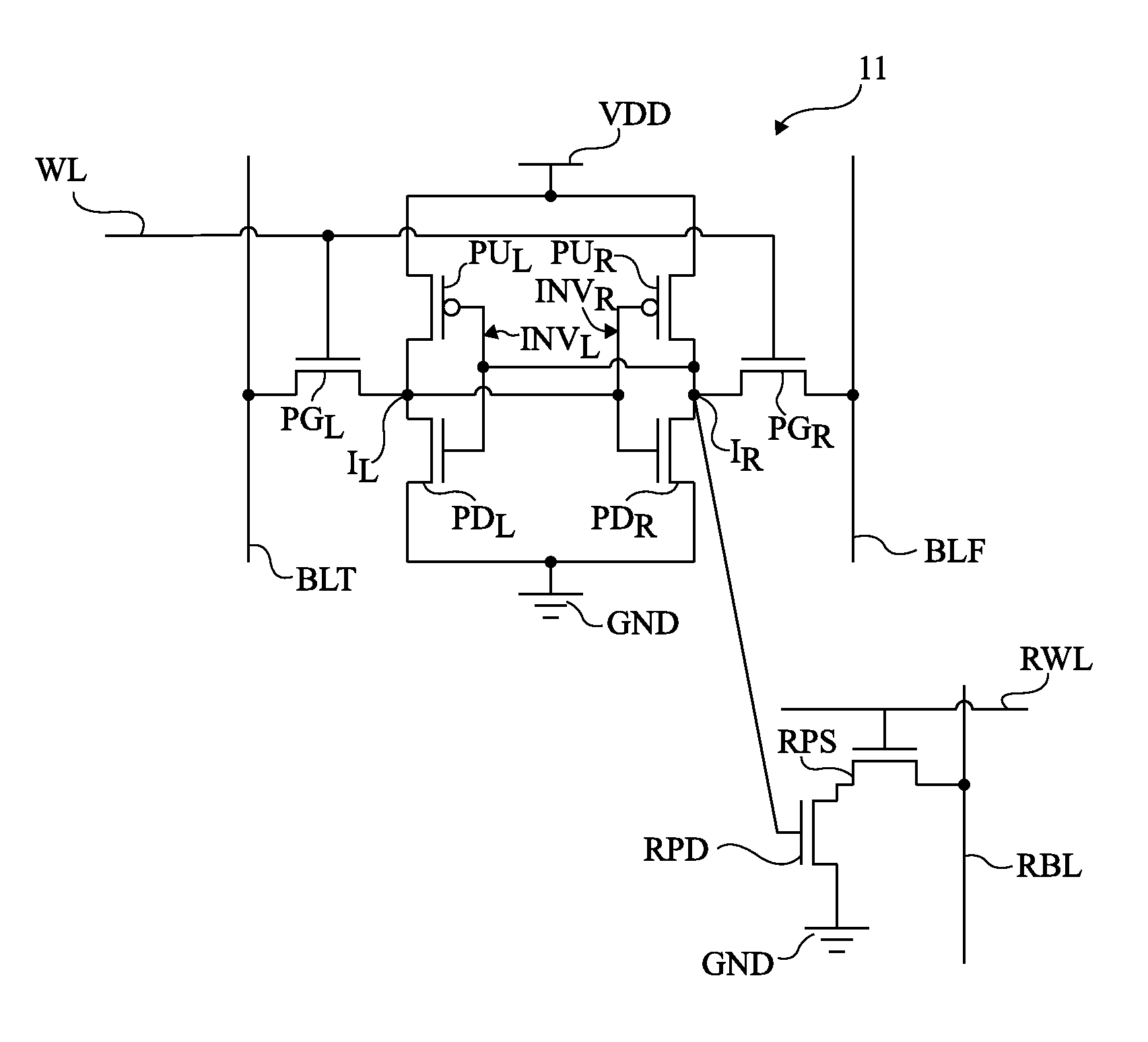

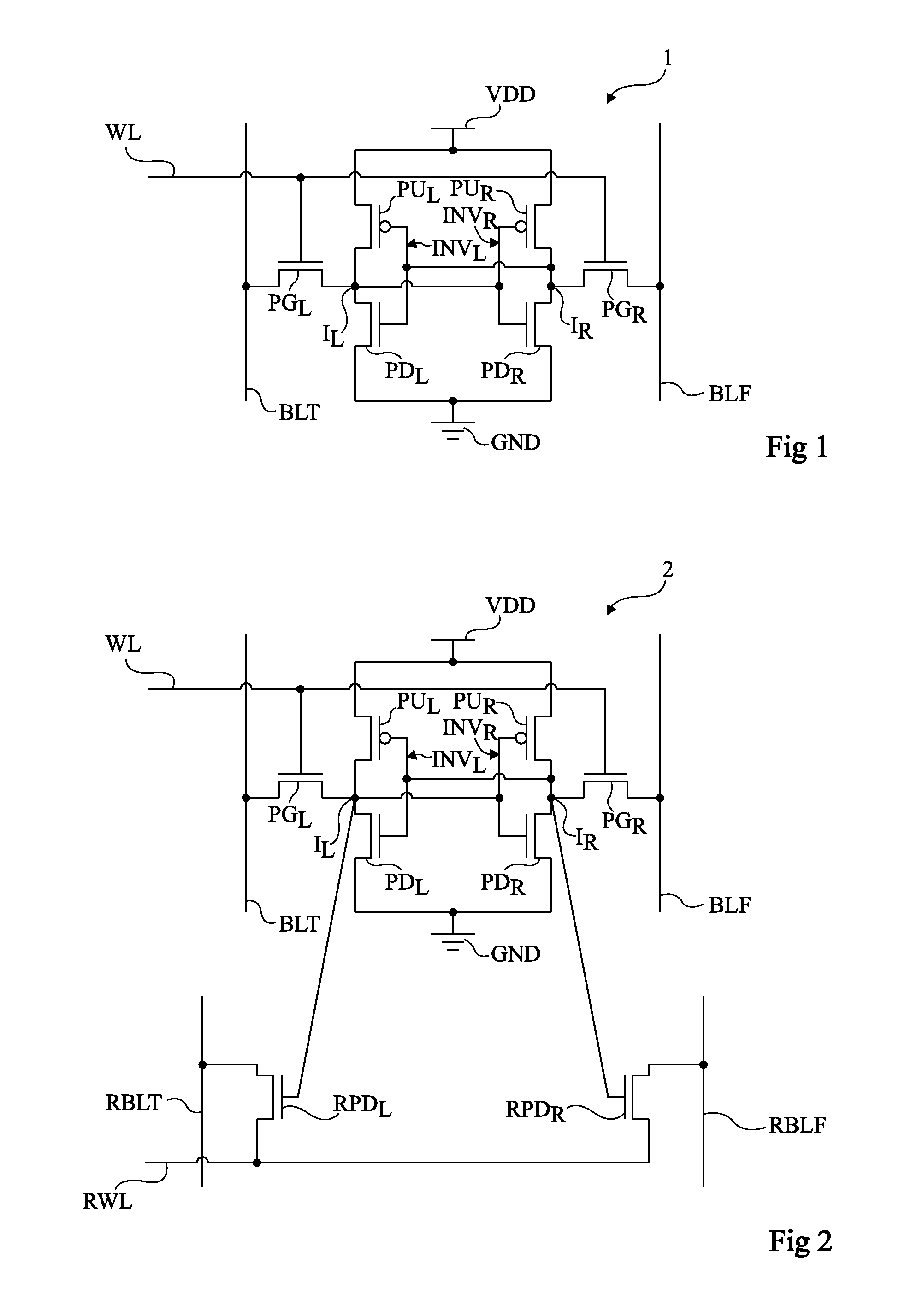

[0052]The embodiments described hereafter may be implemented with a memory cell comprising read bit lines dedicated to read operations and separate from the write bit lines. In this type of cells, the read and write paths are separate.

[0053]As an example, the present embodiment may be implemented with the memory cell example described in FIG. 2. However, the embodiment of the present invention may be implemented in other examples of memory cells, and especially the memory cells described in publication “A 0.5-V 25-MHz 1-mW 256-Kb MTCMOS / SOI SRAM for Solar-Power-Operated Portable Personal Digital Equipment-Sure Write Operation by Using Step-Down Negatively Overdriven Bitline Scheme” by Nobutaro Shibatao, Hiroshi Kiya, et al. (I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More