Performance-imbalance-monitoring processor features

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

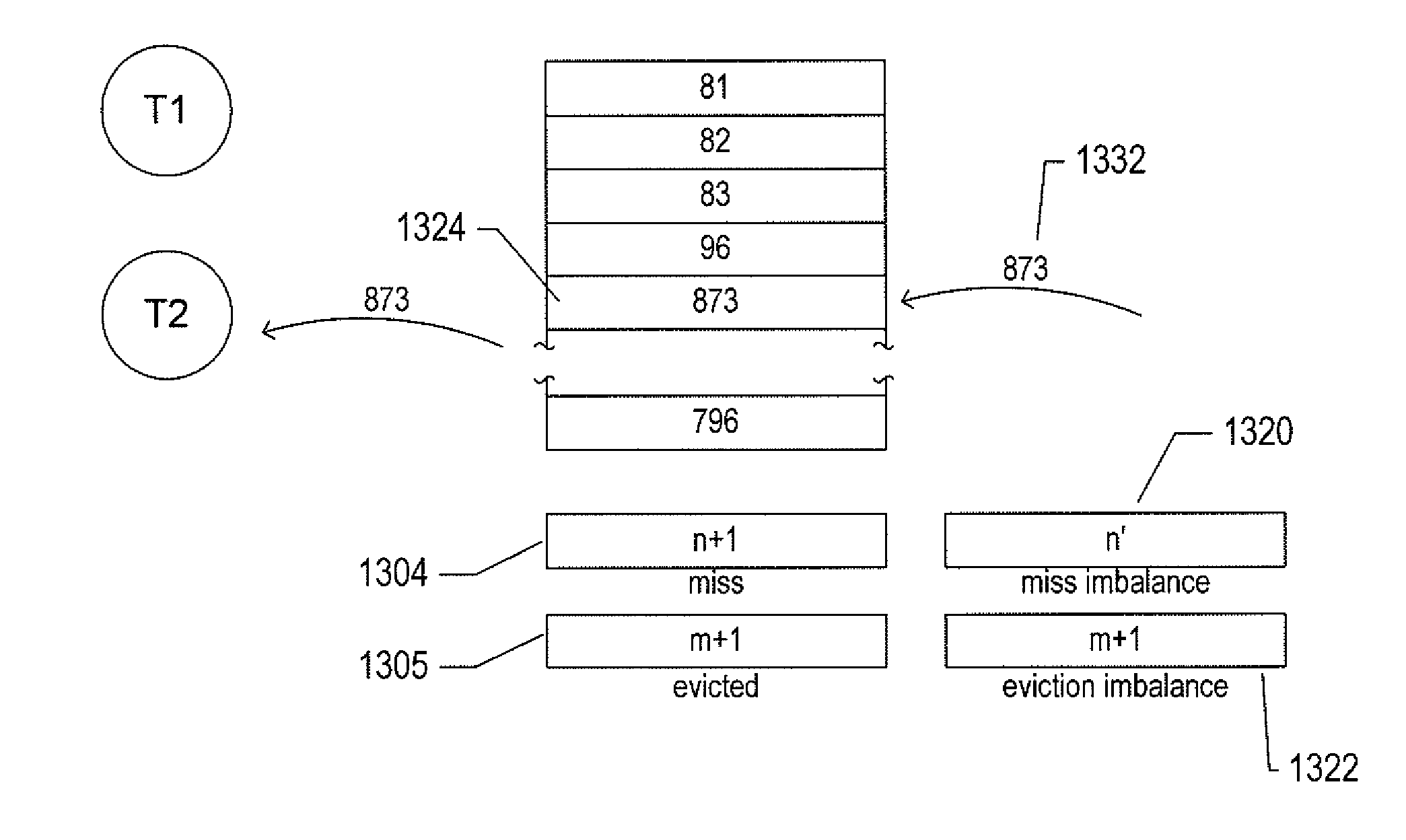

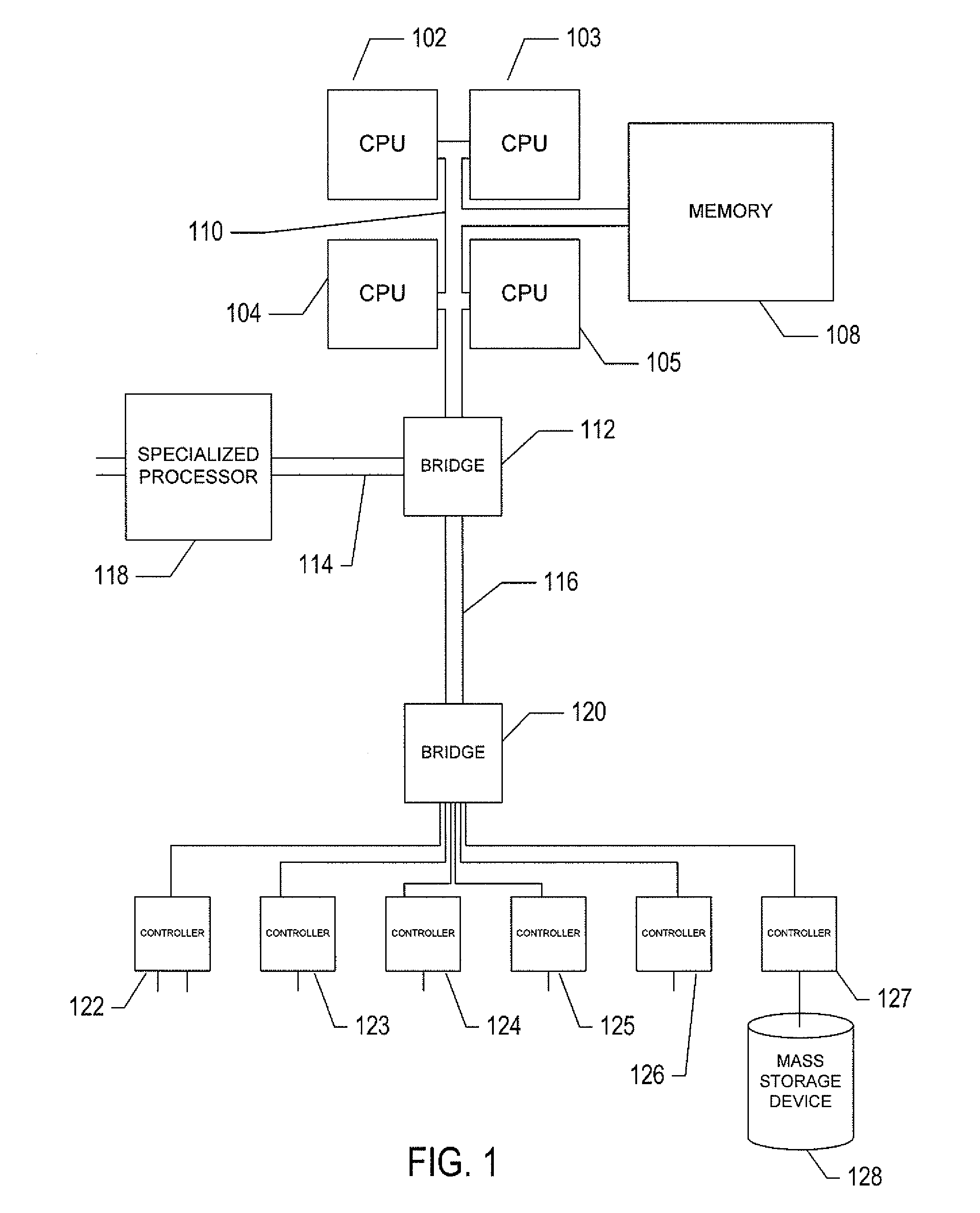

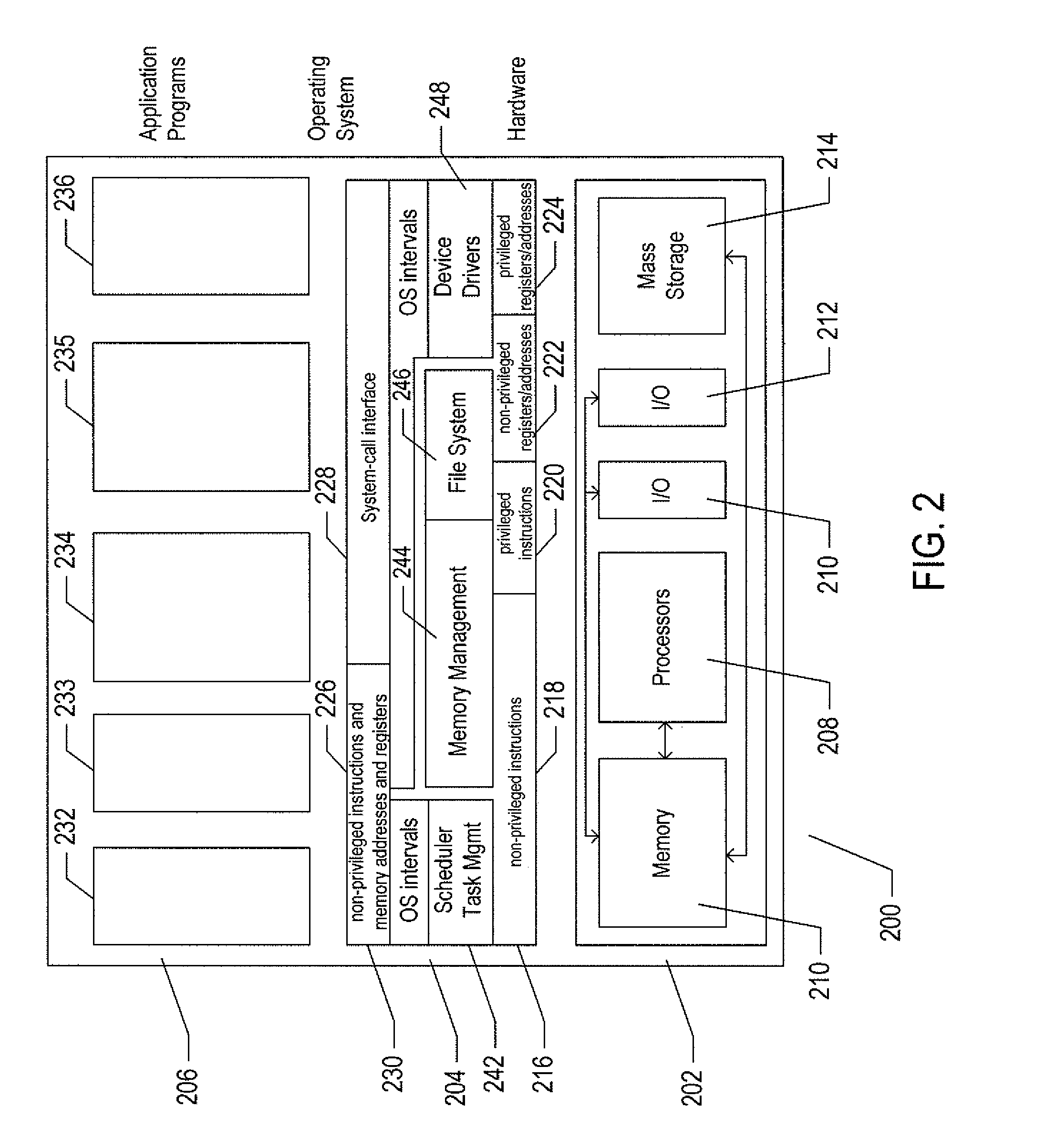

[0021]The current application discloses a new type of performance-imbalance-monitoring register included as an architected feature of a simultaneous multi-threading (“SMT”) processor or SMT-processor core. Performance-imbalance-monitoring registers allow a virtual-machine monitor, operating system, and / or various types of performance-monitoring software applications to detect performance-degrading conflicts between simultaneously executing hardware threads within an SMT processor or SMT-processor core. Performance-degrading conflicts can then be ameliorated by any of many different techniques. A virtual-machine monitor or operating system can, as one example, alter the assignments of virtual machines, tasks, and other computational entities or threads within SMT processors and SMT-processor cores in order to create or eliminate performance-degrading conflicts. Alternatively, problematic applications, tasks, virtual machines, or other computational entities may either be scheduled fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More