Multi-Core Processor System

a processor system and multi-core technology, applied in the field of processor technologies, can solve the problems that the inter-core hardware message queue structure of the cmp in the prior art cannot meet the inter-core message exchange and task scheduling with higher performance, and achieve the effect of improving efficiency and performance of the multi-core processor system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

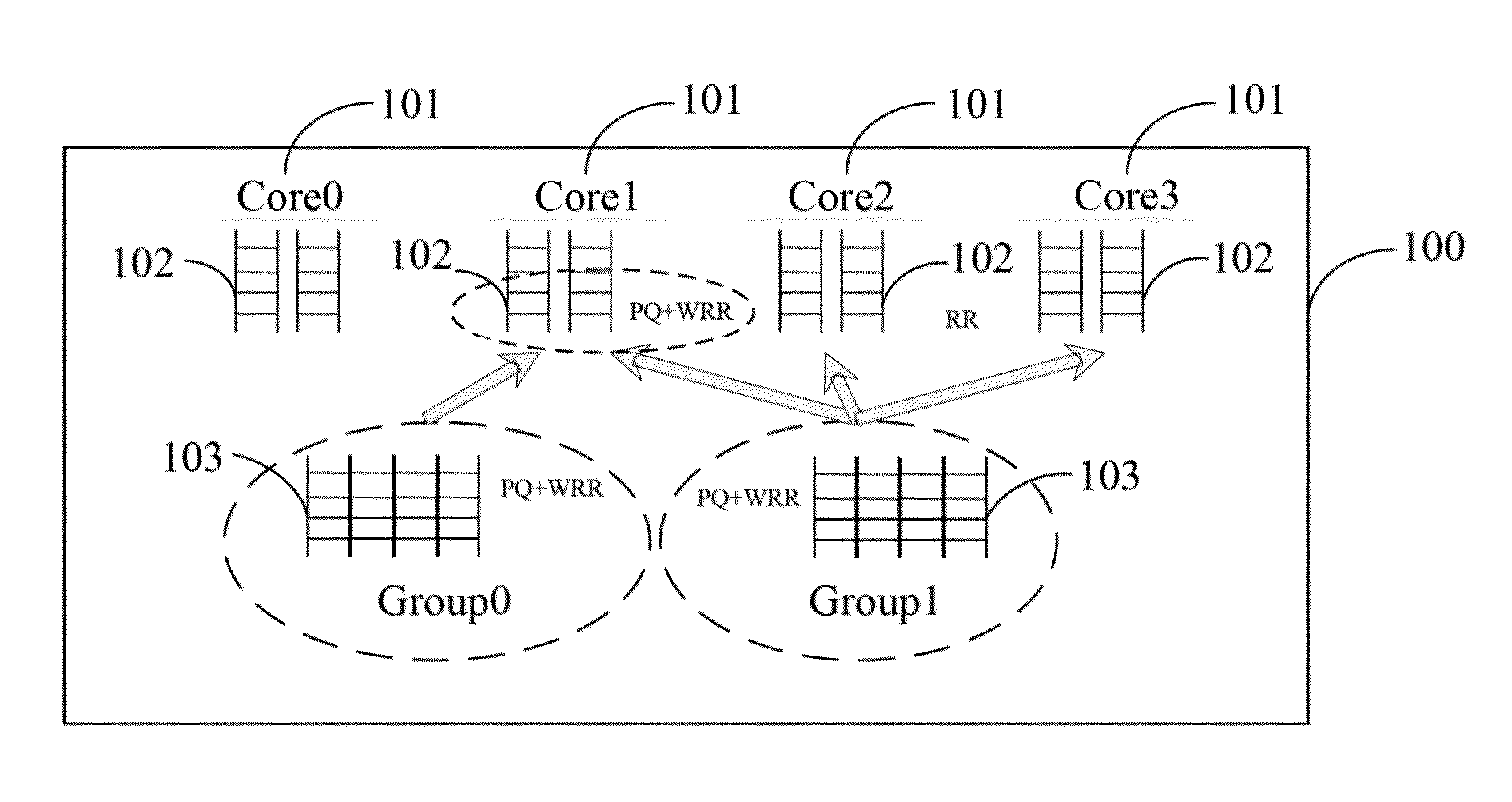

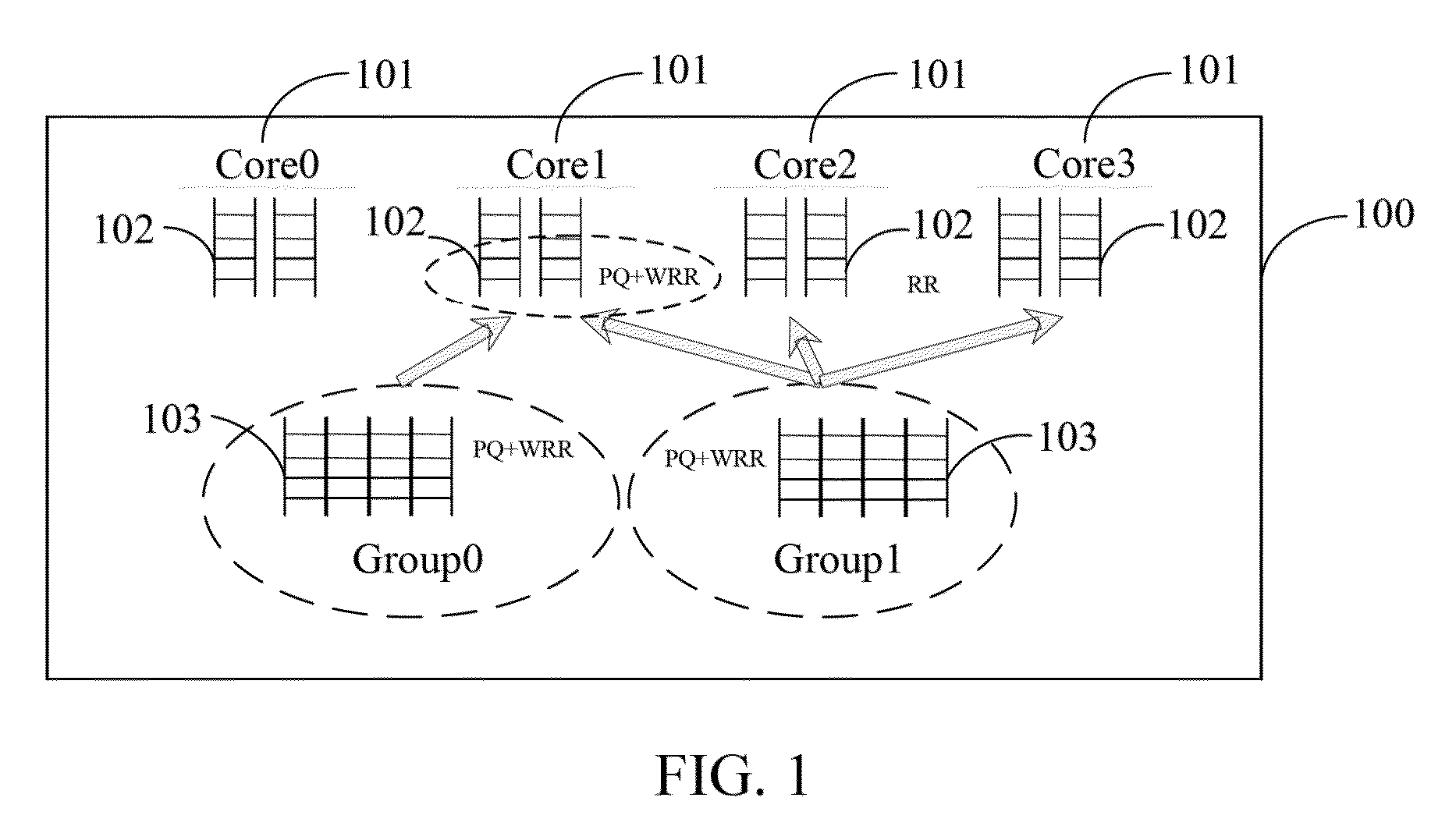

[0012]An embodiment of the present invention provides a multi-core processor system. The system includes multiple central processor units and multiple groups of level-one hardware message queues, where each central processor unit is separately connected to a group of level-one hardware message queues and is configured to process messages in the level-one hardware message queues, where each group of level-one hardware message queues includes multiple level-one hardware message queues. In each group of level-one hardware message queues, a level-one hardware message queue having a higher priority is scheduled preferentially, and level-one hardware message queues having the same priority are scheduled in a round-robin manner according to round robin scheduling weights.

[0013]Another embodiment of the present invention further provides a multi-core processor system. The system includes multiple central processor units, multiple groups of level-one hardware message queues, and multiple gro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More