3D stacked IC device with stepped substack interlayer connectors

a technology of interlayer connectors and ic devices, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of increasing the number of lithographic steps, increasing the cost of interconnection implementation, and increasing the number of layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020]A detailed description of embodiments of the present invention is provided with reference to the FIGS. 1-31.

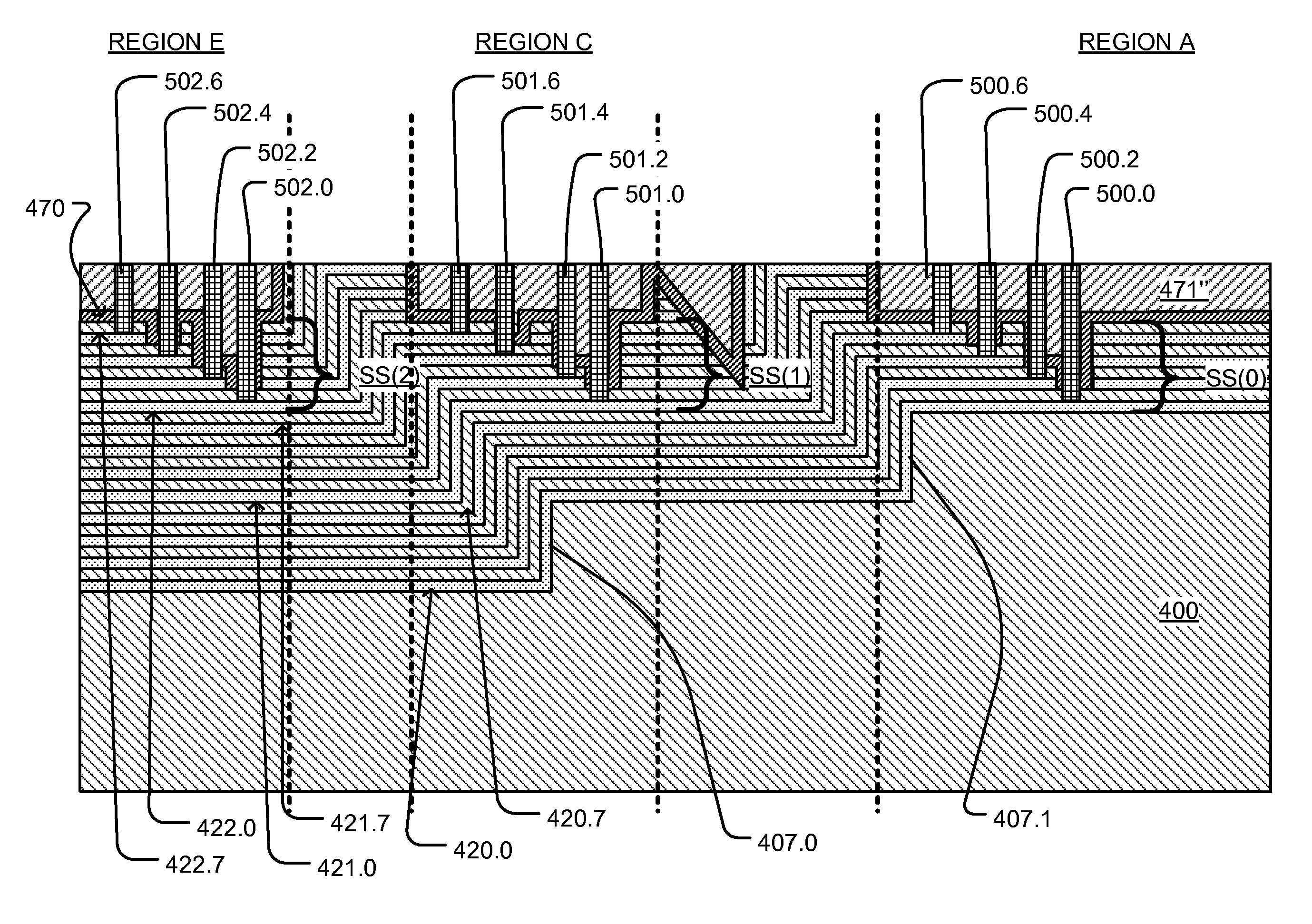

[0021]FIG. 1 is a perspective illustration of a three-dimensional (3D) NAND-flash memory device which includes contact pads at which interlayer connectors contact the corresponding active layers. The device illustrated in FIG. 1 includes stacks of active lines in active layers of the array, alternating with insulating lines. Insulating material is removed from the drawing to expose additional structure. For example, insulating lines are removed between the semiconductor lines in the stacks, and between the stacks of semiconductor lines. This structure is described herein in some detail, as an example of a three-dimensional (3D) memory array which can be manufactured in a recessed area, or pit, on a semiconductor substrate, in combination with peripheral circuits on the substrate outside of the pit. In some embodiments, the structure shown in FIG. 1 is not manufactured in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More