Atomic memory operations on an n-way linked list

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038]A variety of examples are presented in this Detailed Description. These examples may be referred to as exemplary. Note that the term “exemplary,” as used in this Detailed Description, simply means an example, instance, or illustration. This term is not used to mean that a particular example is superior, commendable, or otherwise deserving of imitation over other examples.

[0039]Accessing an N-Way Linked List

[0040]An N-way linked list according to various embodiments includes elements for storing data, two or more sub-lists, and a handle. The handle may include tail elements, head elements, or both for each of the sub-lists. The handle may be an array of handles for individual sub-lists. In addition, parameters that track the number of elements added or removed from the various sub-lists may be associated with an N-way linked list. Exemplary “ITAIL” and “RTAIL” parameters for tracking the addition and removal of elements are described below.

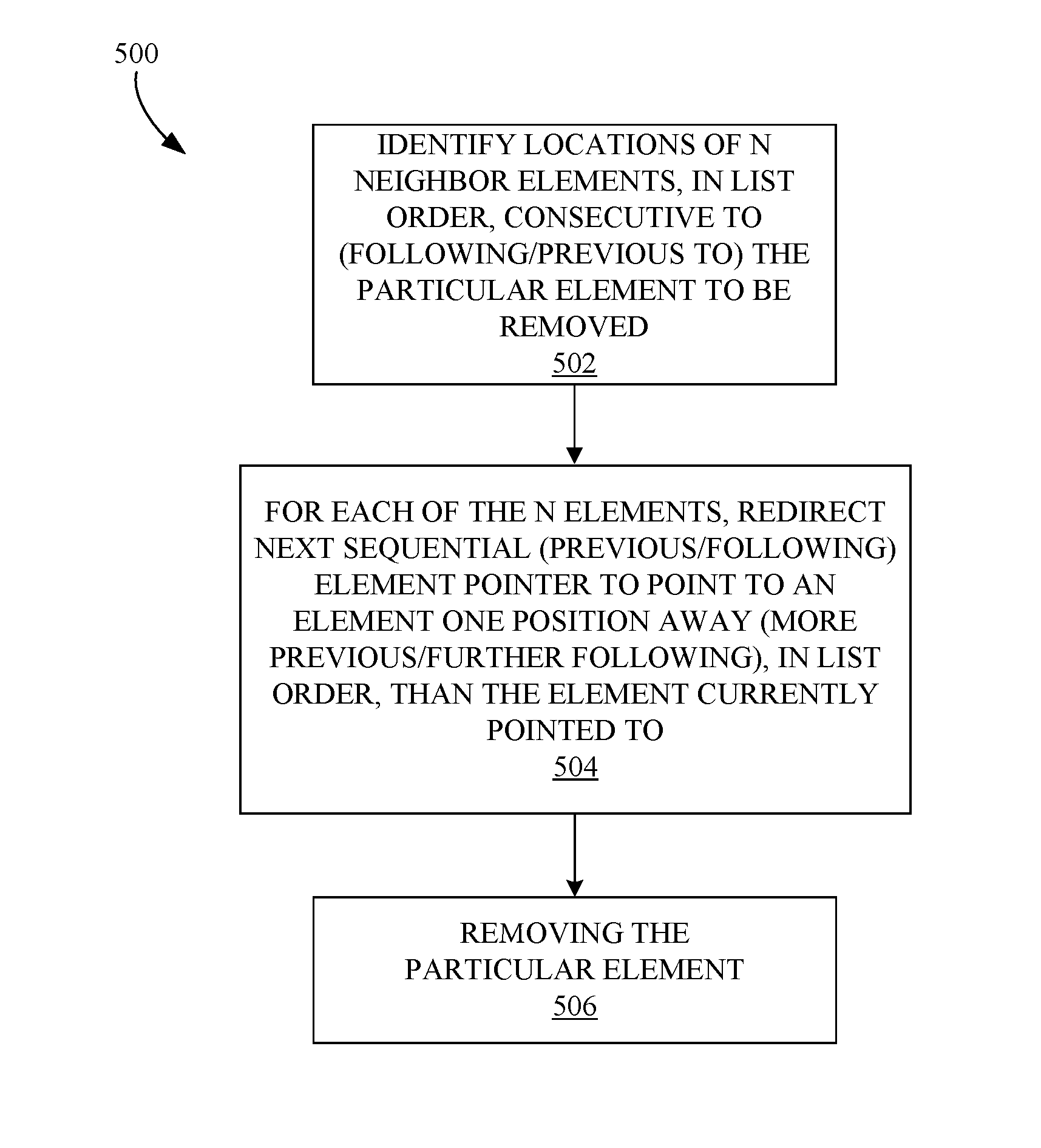

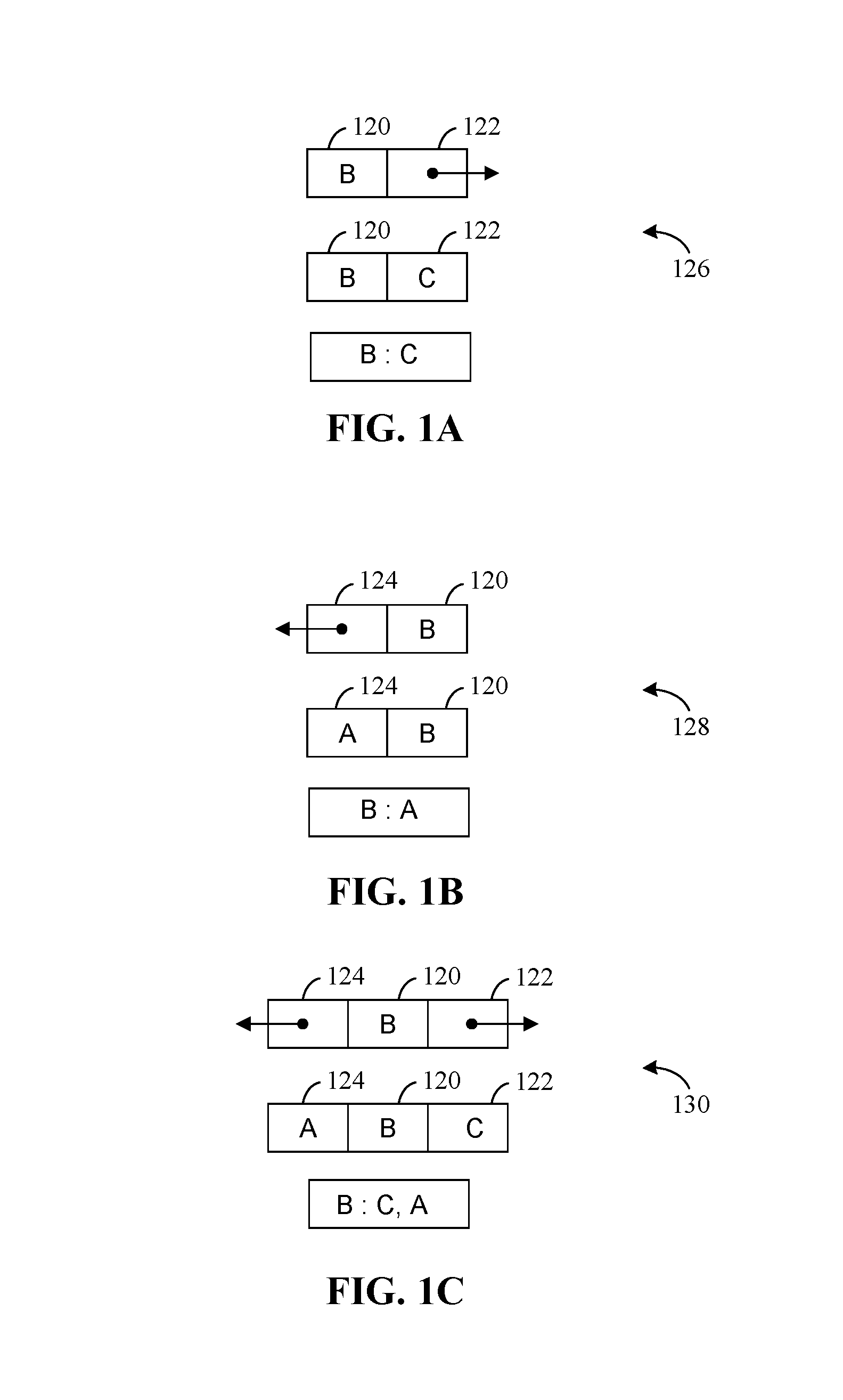

[0041]Referring to FIGS. 1A-1C, an ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More