VERIFY SCHEME FOR ReRAM

a verification scheme and memory array technology, applied in the field of high density memory arrays, can solve the problems of less reliable devices over repeated use, and achieve the effect of less stress and more reliabl

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

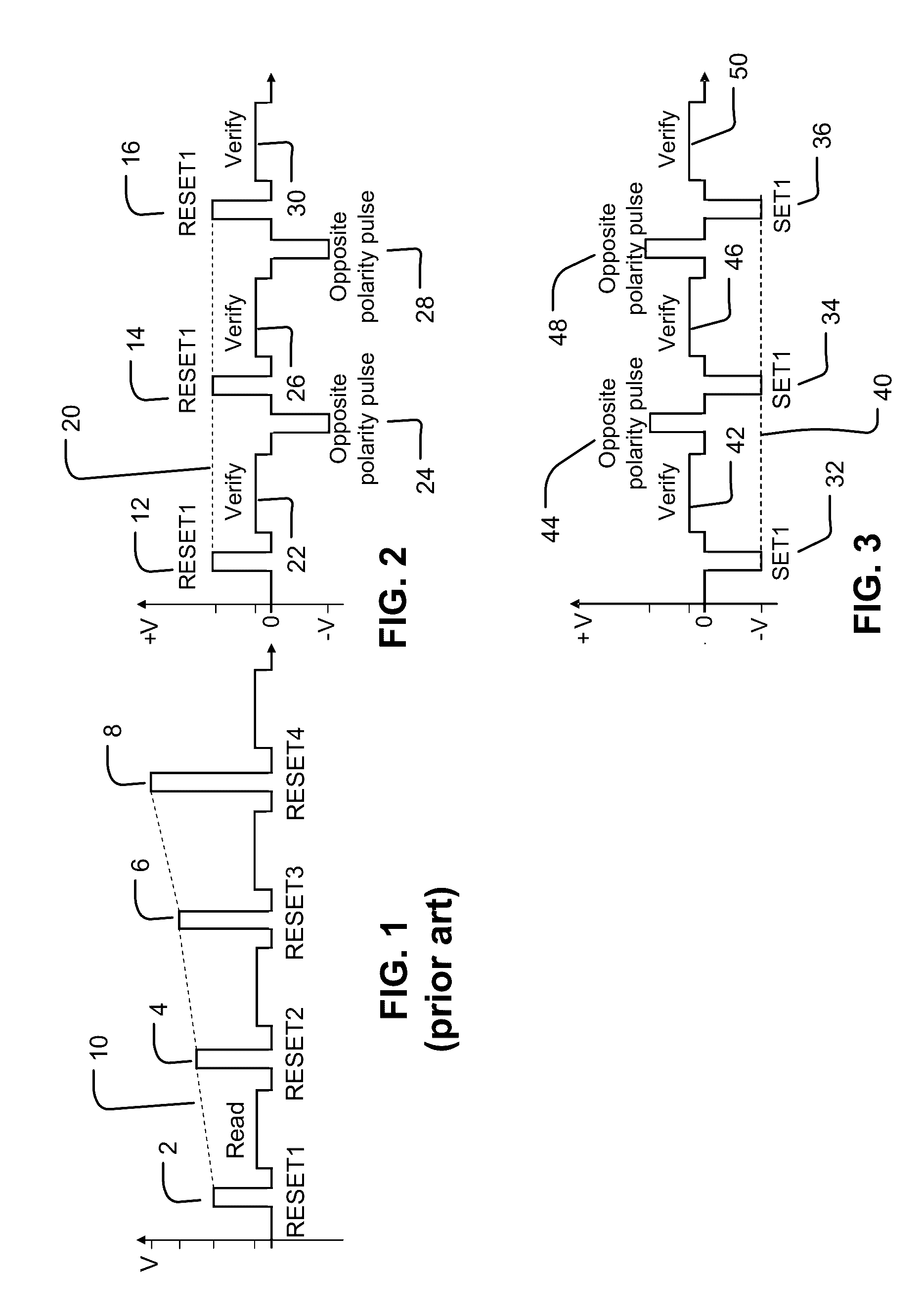

[0046]FIG. 1 is a graph of voltage versus time, showing a series of reset programming operation pulses with increasing amplitudes, in response to failed program verify operations.

[0047]A selected memory cell undergoes multiple cycles of programming reset and verify operations. In each cycle, a programming reset operation occurs, followed by a verify operation which reads the selected memory cell.

[0048]With the shown graph, four cycles of programming reset and verify operations are shown as 2, 4, 6, and 8. With each subsequent cycle, the magnitude of the programming reset pulse increases after a failed verify, to perform incremental step pulse programming (ISPP). The programming pulse names RESET1, RESET2, RESET3, and RESET4 indicate the increasing magnitudes. A positive slope trend line 10 connects the tops of the programming pulses, indicating the increasing magnitudes.

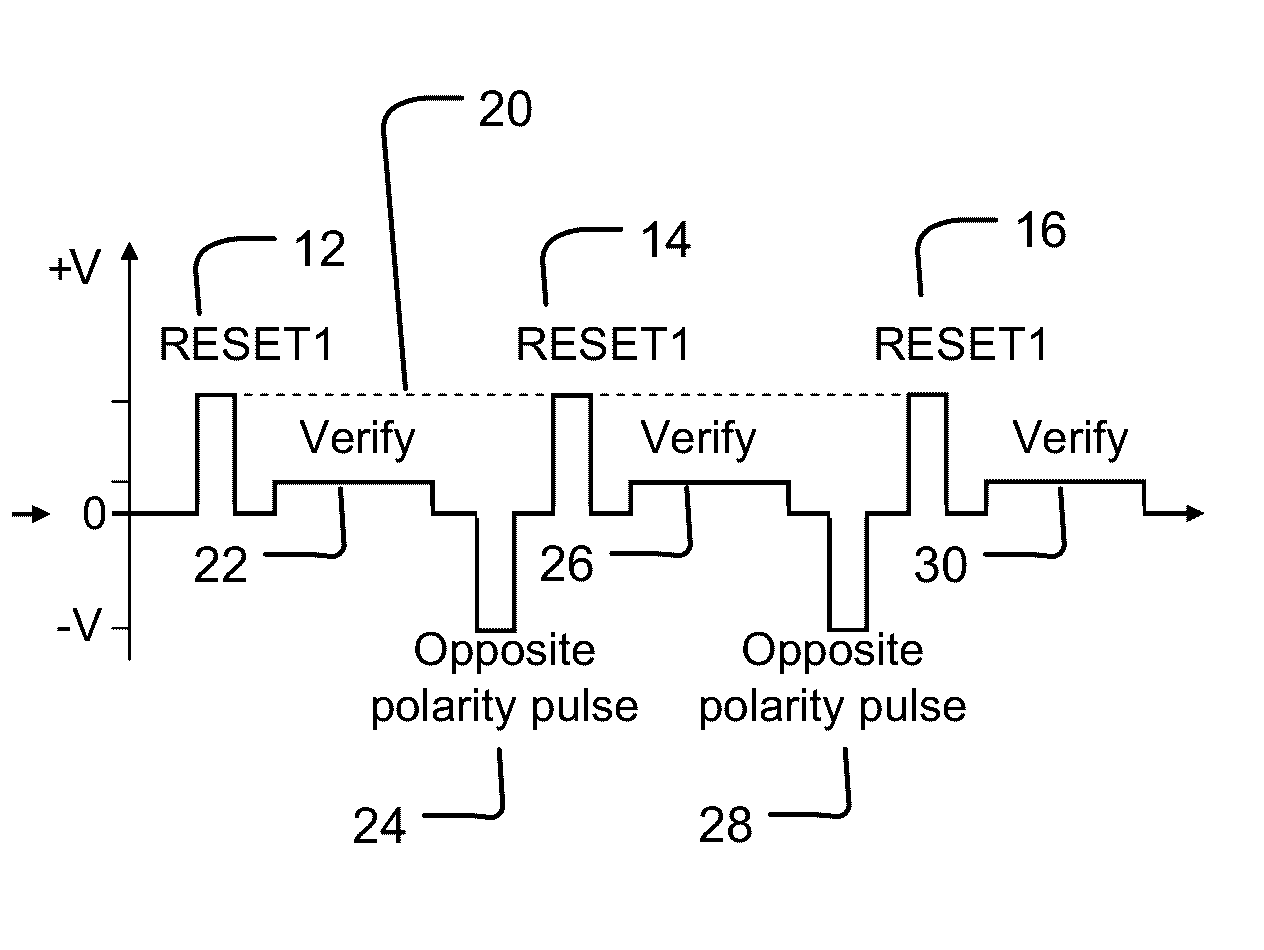

[0049]FIG. 2 is a graph of voltage versus time, showing, in response to failed program verify operations, (i) a se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More