Semiconductor device and manufacturing method for the same

a technology of semiconductor devices and manufacturing methods, applied in the field of semiconductor devices, can solve the problems of almost impossible to form a desired dimension of the fin, e.g., a width, a tendency to collapse/undesirably remove the fin structure, etc., and achieve the effect of improving the yield of the semiconductor device and reducing the collapse of the fin structur

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

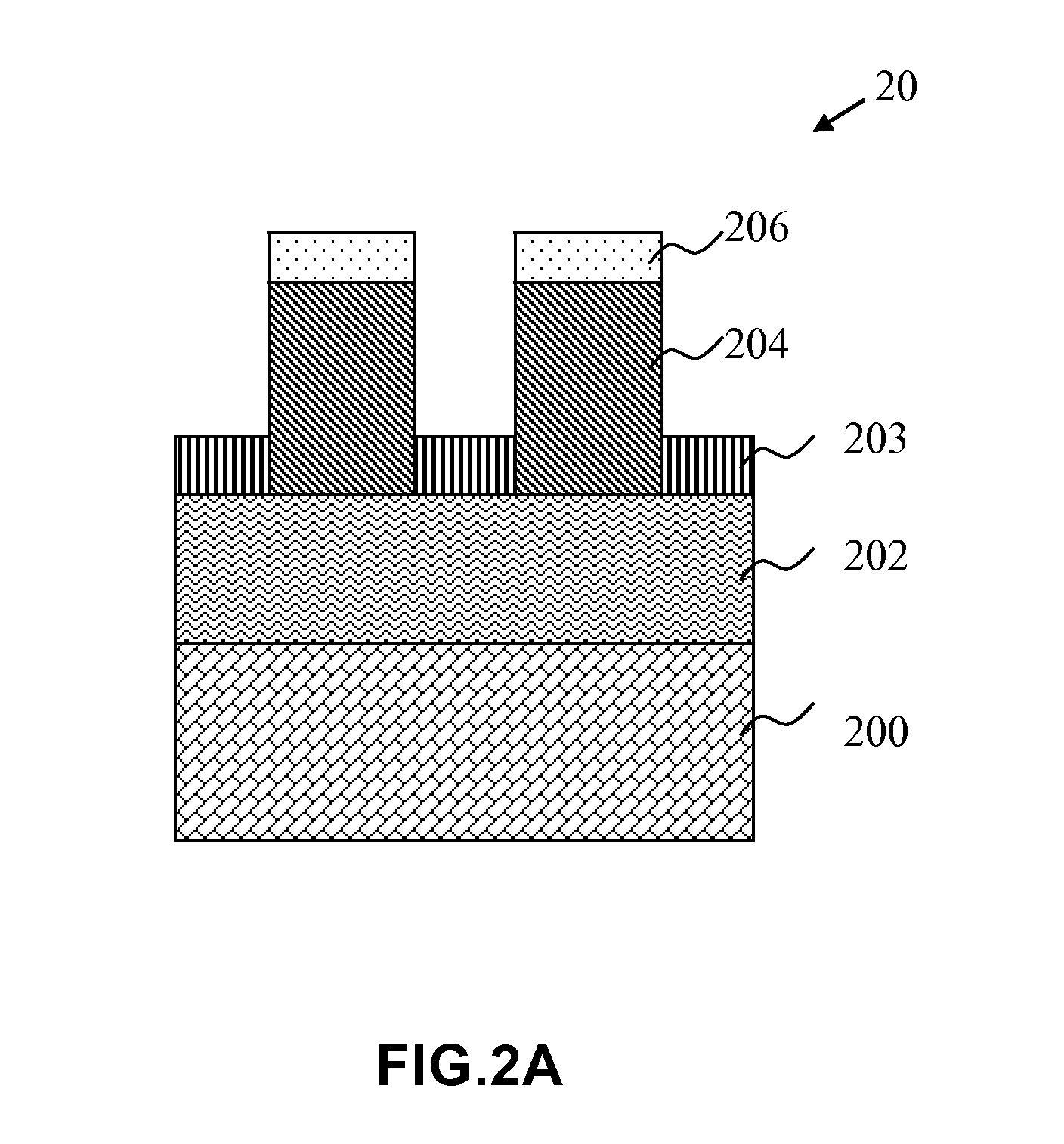

[0054]The detailed description set forth below in connection with the appended drawings is intended as a description of some of the example embodiments, and is not intended to completely describe all possible embodiments. That is, there is no intention to be bound by any expressed or implied theory presented in the preceding technical field, background, or the following detailed description of example embodiments. It is to be understood that the same or equivalent functions may be accomplished by different embodiments.

[0055]The terms “first”, “second”, and the like in the description and the claims, if any, may be used for distinguishing between similar elements and not necessarily for describing a particular sequential or chronological order. It is to be understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments described herein are, for example, capable of use in sequences other than those illustrated or otherwise described here...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More