Scheduling of scenario models for execution within different computer threads and scheduling of memory regions for use with the scenario models

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

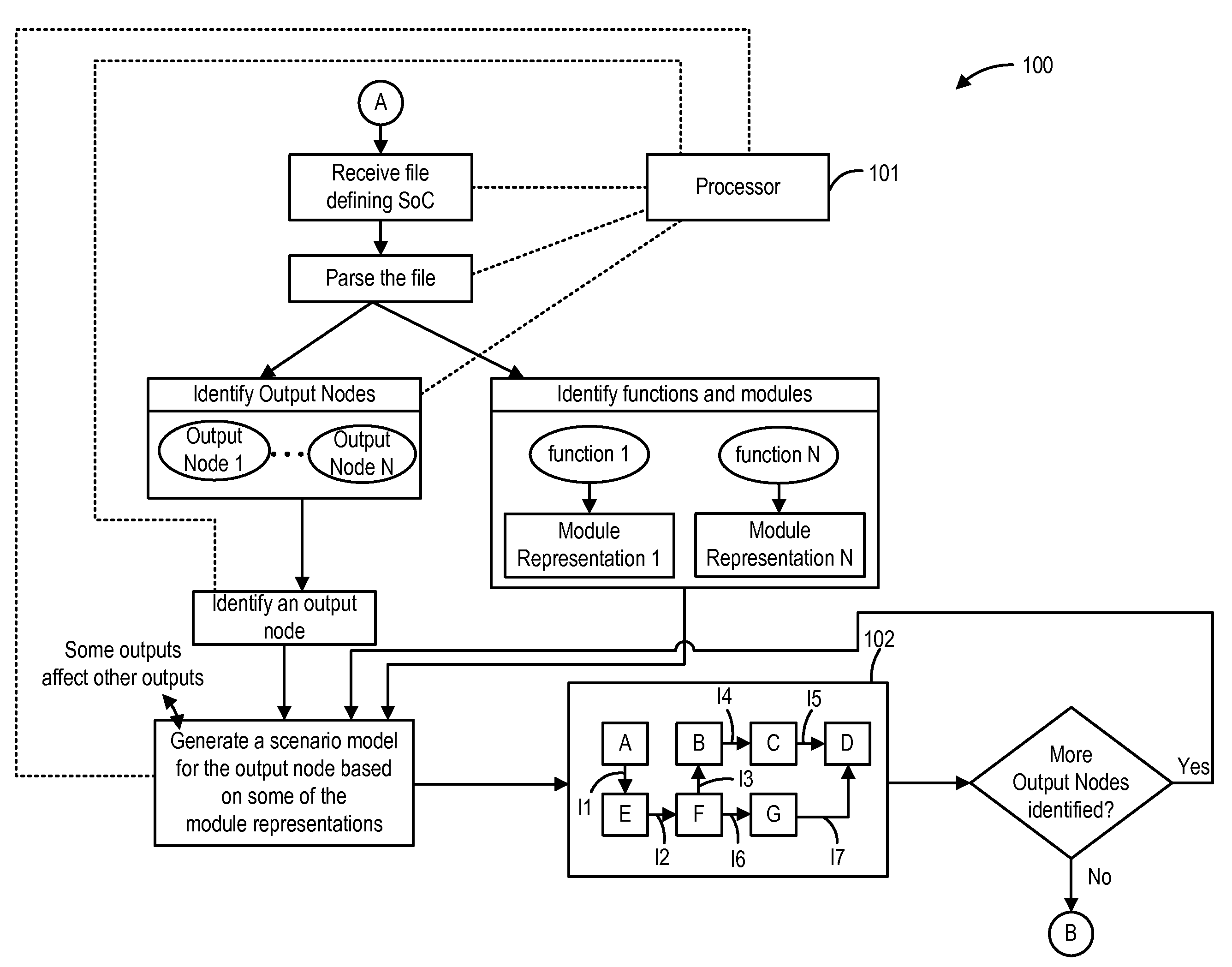

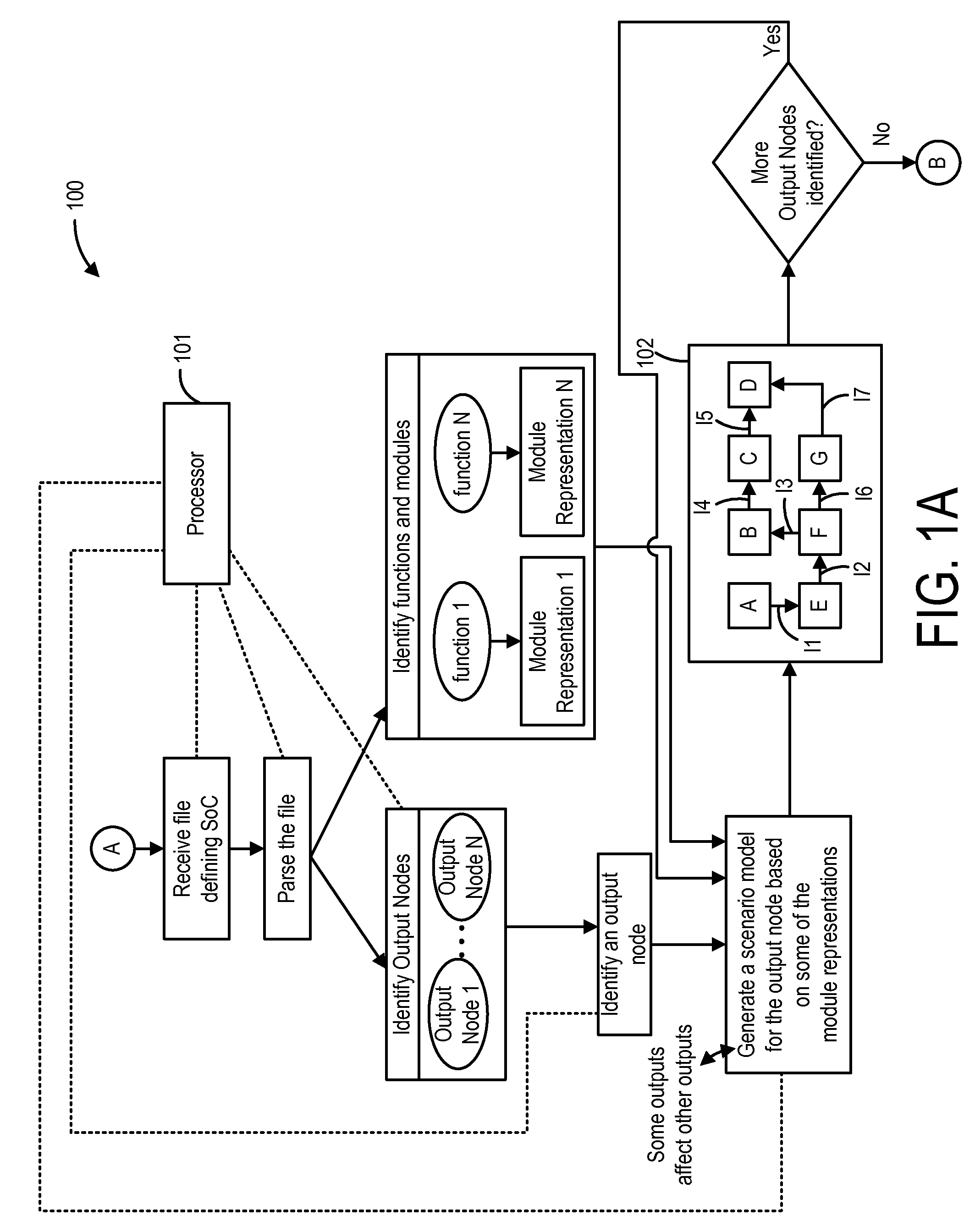

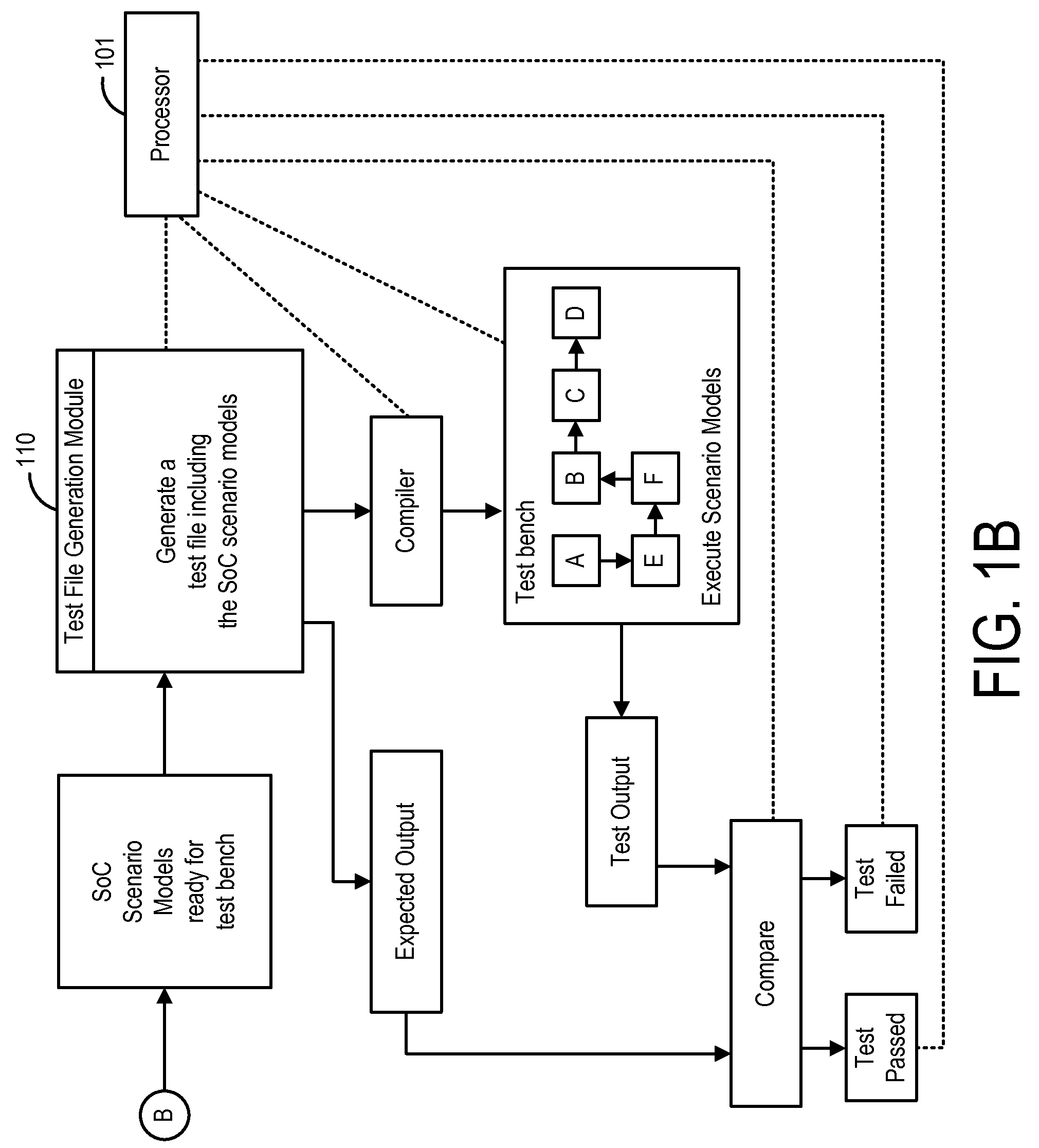

[0099]The following embodiments describe systems and methods for testing a system-on-a-chip (SoC) with scenario models and at different horizontal and vertical levels. It will be apparent that the present embodiments may be practiced without some or all of these specific details. In other instances, well known process operations have not been described in detail in order not to unnecessarily obscure the present embodiments.

[0100]In one embodiment, the SoC is an integrated circuit (IC) that integrates all components, e.g., a memory device, a processor, an input / output, a bus, etc., of a computer or another electronic system into a chip. For example, the SoC includes digital, analog, mixed-signal, and often radio-frequency functions-all on a chip substrate. In an embodiment, the SoC includes a microcontroller.

[0101]In an embodiment, instead of the SoC, a system-in-package (SIP) is used. The SIP includes a number of chips in a single package. In a number of embodiments, instead of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com