System for coupling programmable logic device to external circuitry which selects a logic standard and uses buffers to modify output and input signals accordingly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

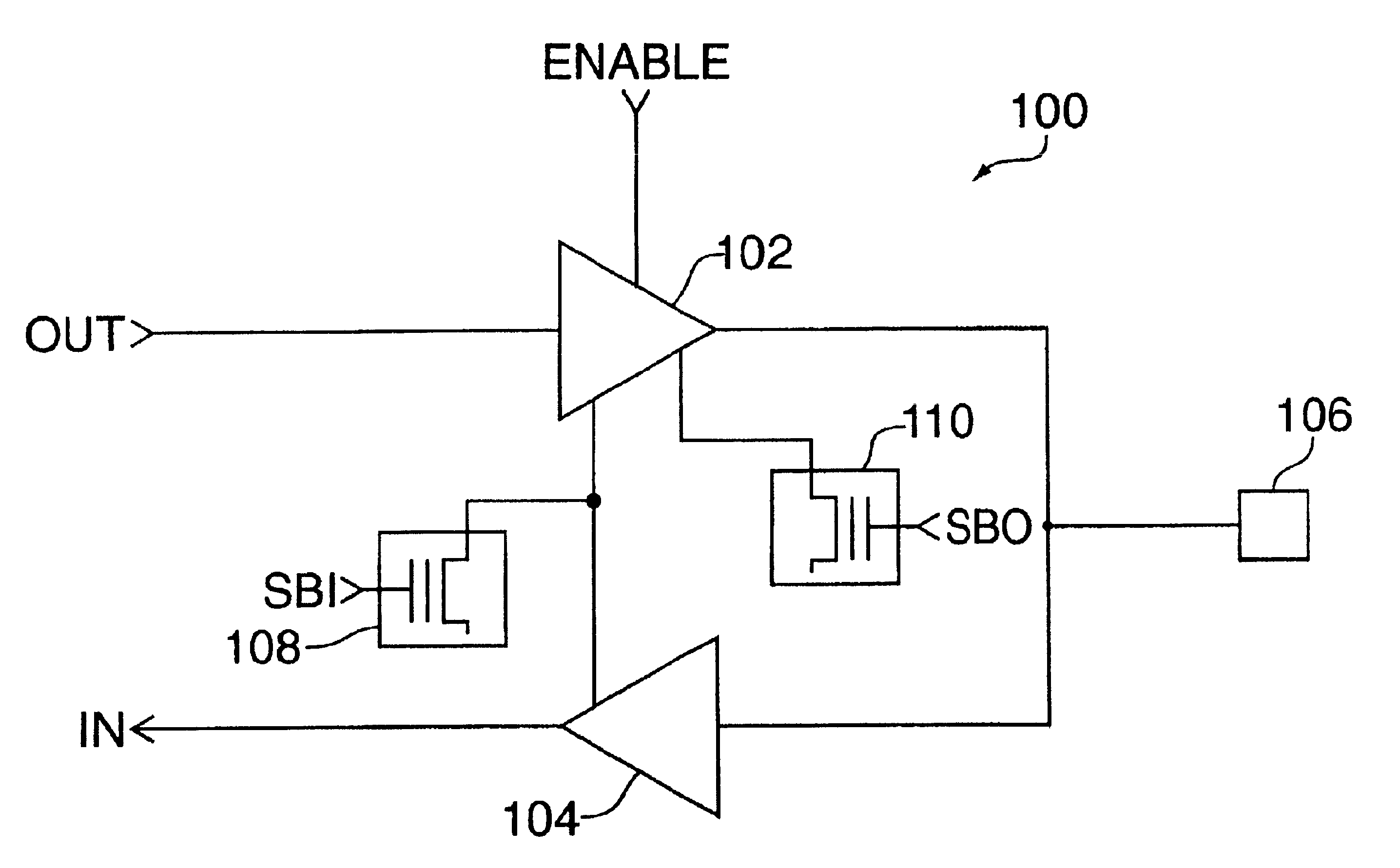

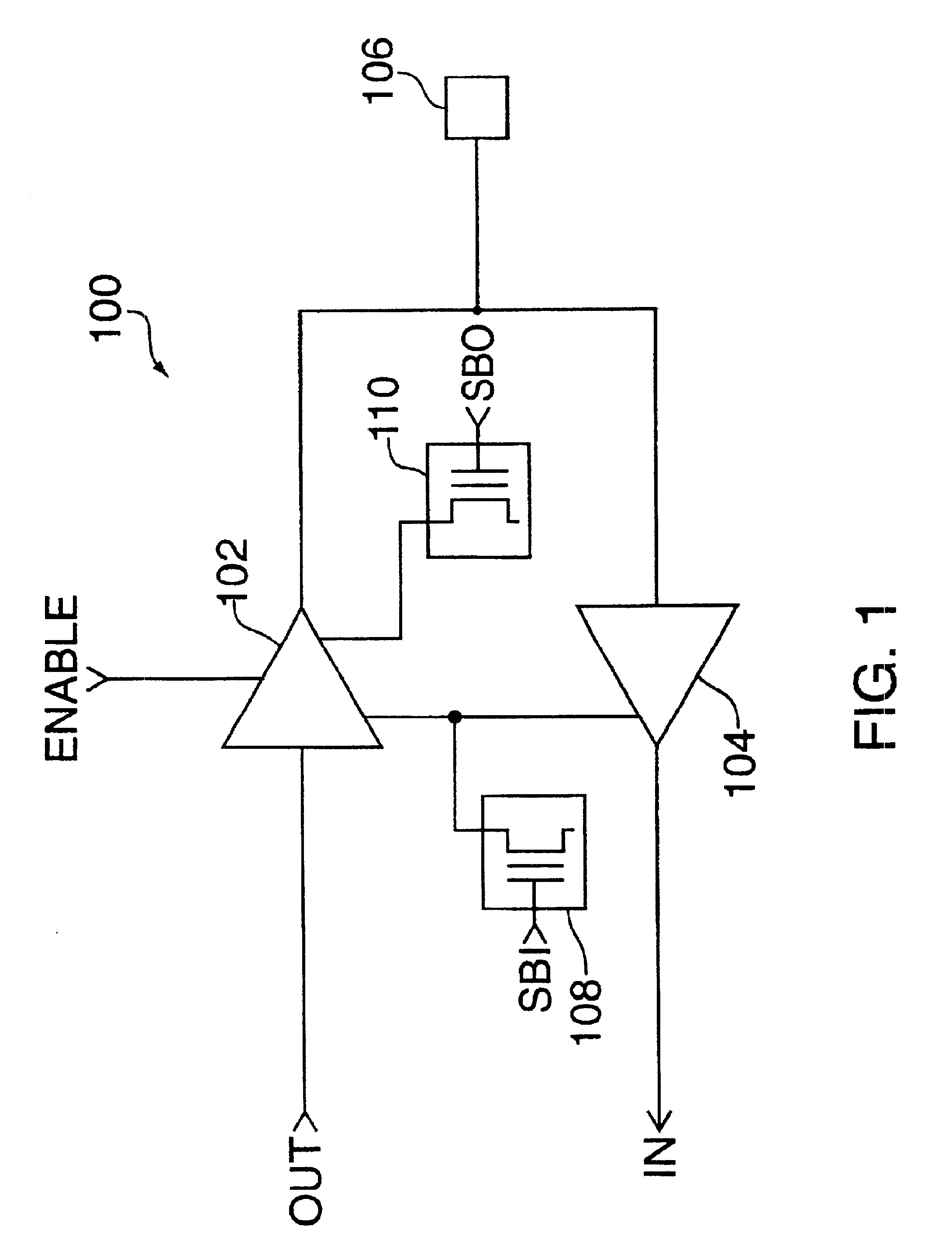

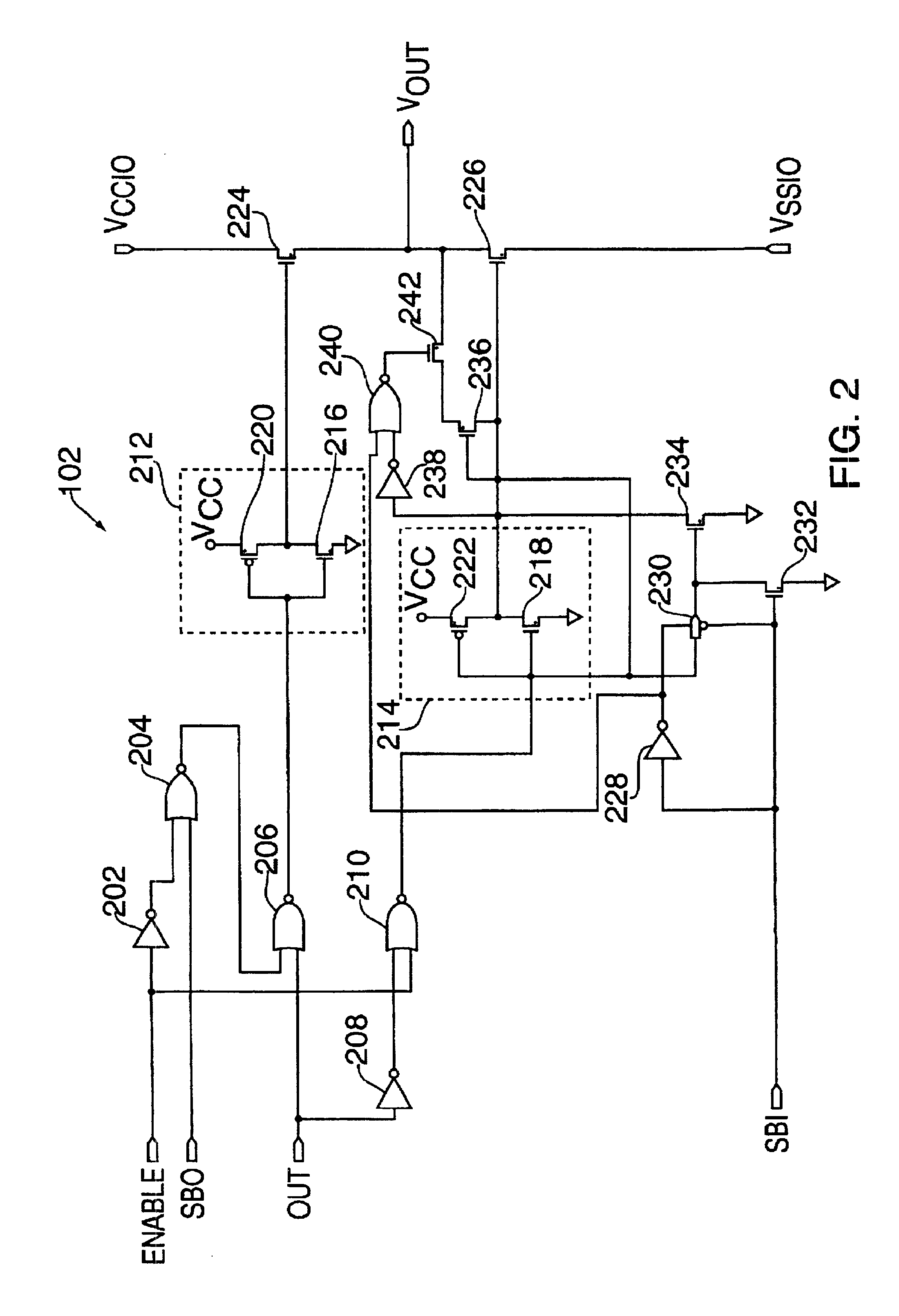

[0022]FIG. 1 shows a schematic block diagram of a programmable input / output (I / O) circuit 100 which incorporates principles of the present invention. I / O circuit 100 includes output driver 102, input driver 104, I / O pad 106, and programmable elements 108 and 110. Output driver 102, which has an input terminal to receive output signals from a programmable logic device (PLD) (not shown), provides an output signal (OUT) to I / O pad 106 at an appropriate voltage level that corresponds to a selected logic standard. Additionally, output driver 102 has three control lines which receive signals ENABLE, SB0 (Select Bit 0), and SB1 (Select Bit 1).

[0023]Input driver 104, which has an input terminal to receive signals from I / O pad 106 and output buffer 102, provides input signals to the PLD at the appropriate level of voltage, regardless of the voltage level of the signal receive on the input terminal. In addition, input driver 104 also receives control signal SB1 from programmable element 108. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More