Semiconductor device, semiconductor memory device and data processing system comprising semiconductor system

a semiconductor memory and memory device technology, applied in the field of semiconductor memory devices and data processing systems comprising semiconductor systems, can solve the problems of increasing reducing the data retention time of the memory cell, and increasing the boost voltage required for driving word lines, etc., to achieve excellent operating margin for the sense amplifier, reduce the write voltage of the memory cell, and high speed operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030]Typical examples of a technical idea solving the problems of the present invention will be shown. However, it goes without saying that the present invention is not limited to the examples of the technical idea and consists in the scope of the claimed invention.

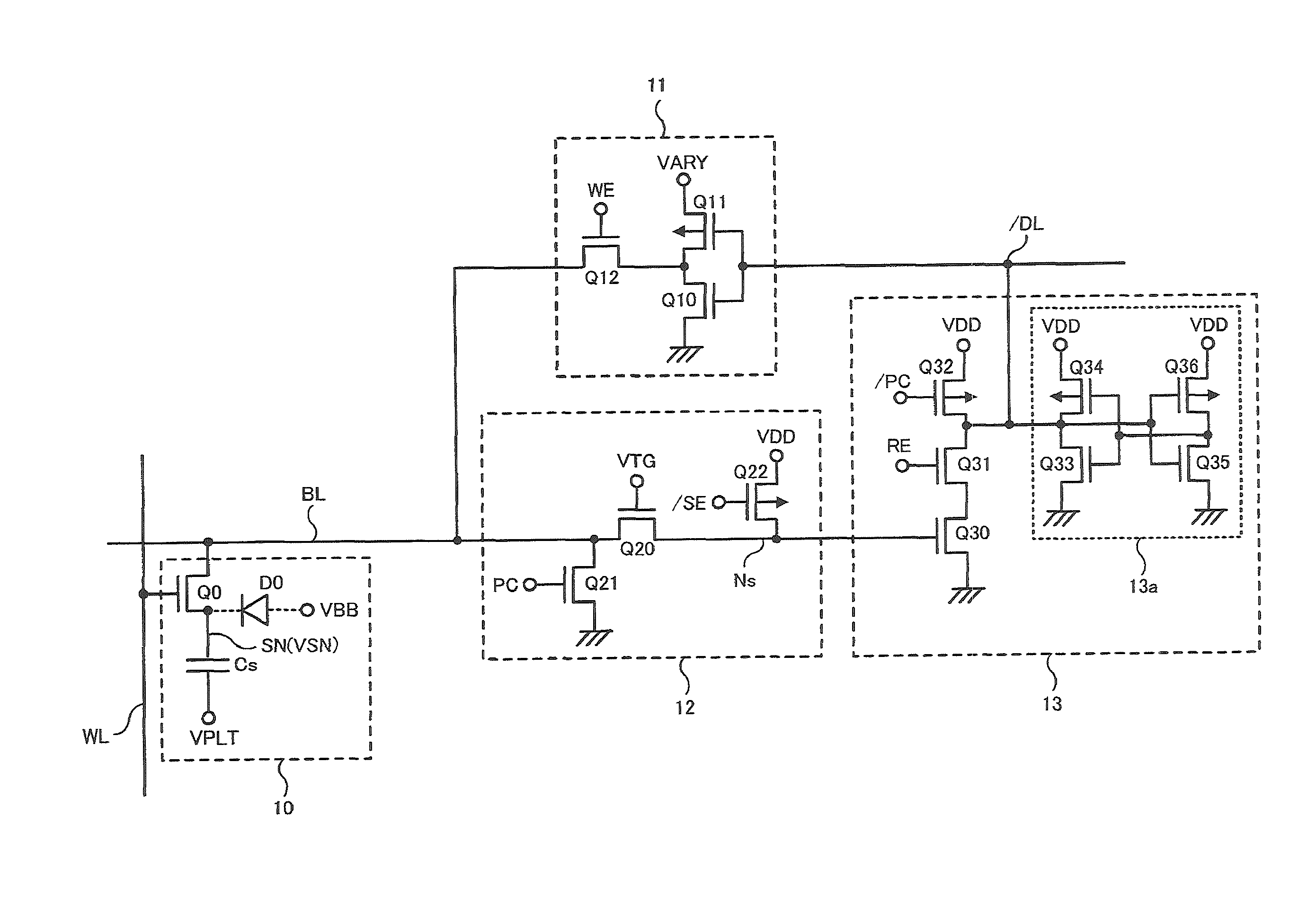

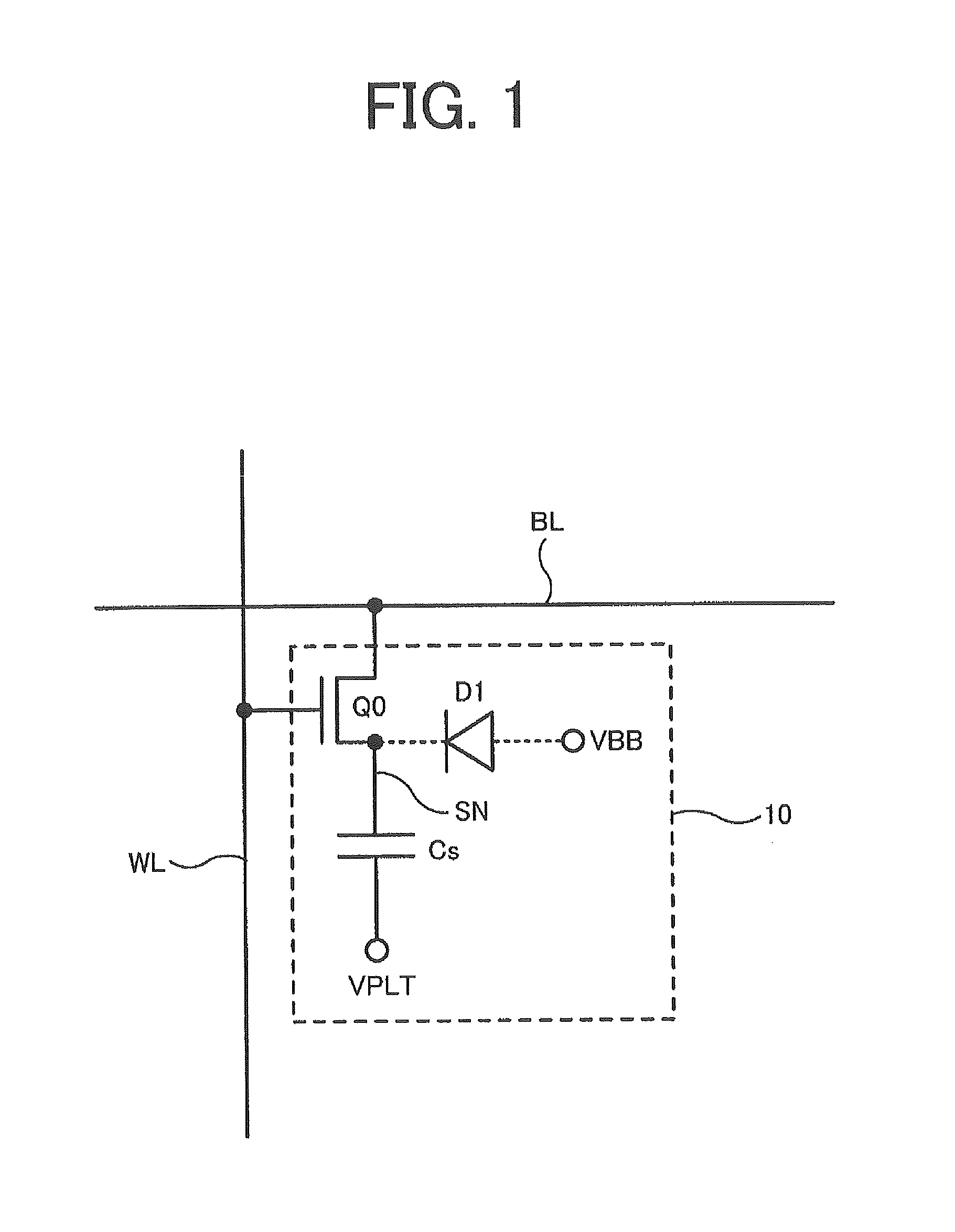

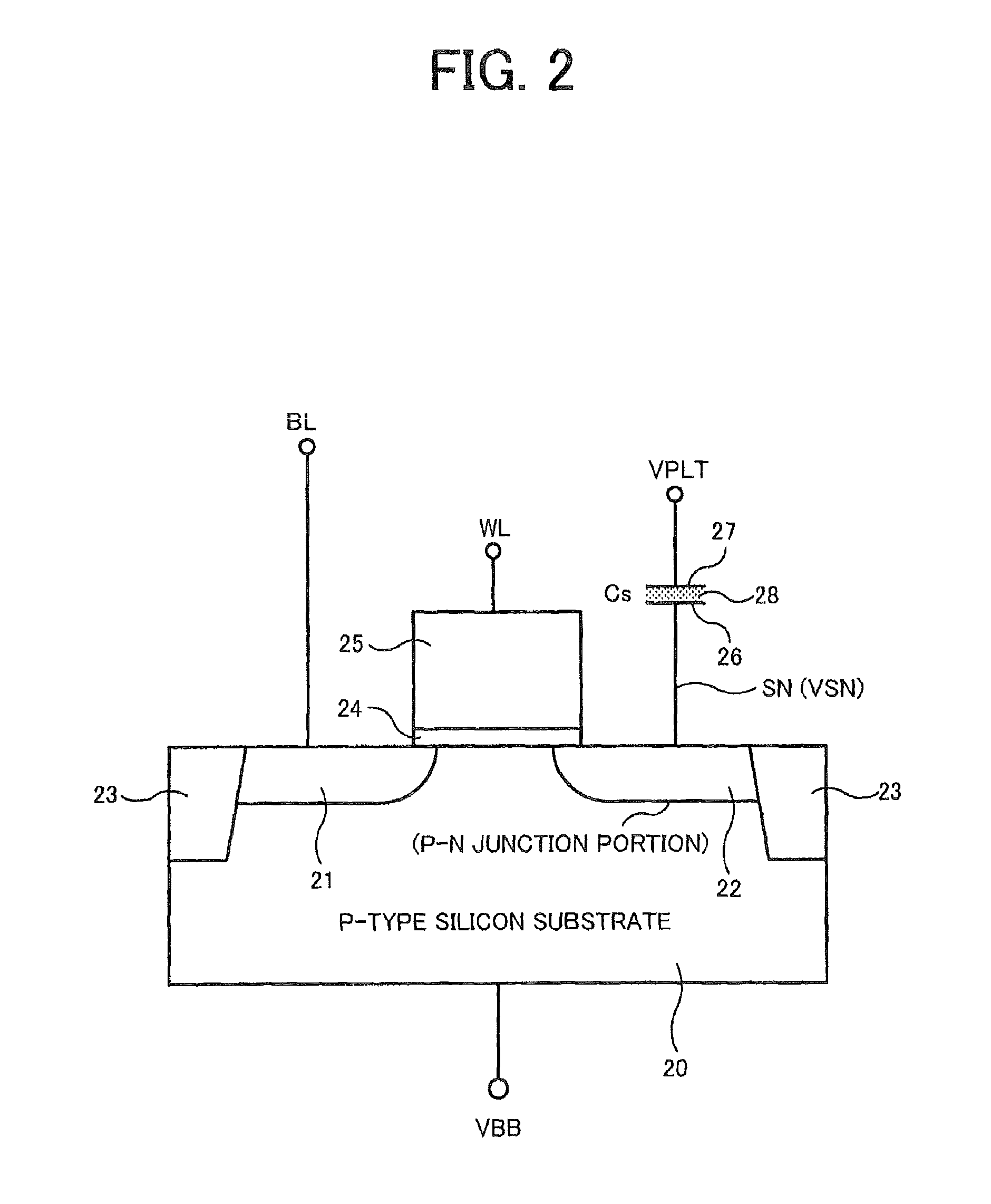

[0031]The technical idea of the present invention is that data (charge amount) of a memory cell (a capacitor) is read out to a bit line, a sense amplifier in which the bit line is connected to a gate of a transistor is configured to amplify the potential of the bit line to an operation voltage of the sense amplifier, a third voltage (VARY) corresponding to high-level data (generally corresponding to “1”) of the memory cell is set lower than a second voltage (VDD) as the operation voltage of the sense amplifier, while the third voltage (VARY) is set higher than a transfer control voltage (VTG) applied to a gate of a transfer transistor (transfer gate) of a transfer control circuit placed between the bit line and the gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More