Control method for automatic testing IC complete device

A technology for integrated circuit and complete machine testing, applied in electronic circuit testing, semiconductor/solid-state device testing/measurement, etc., can solve problems such as software conflicts, dynamic errors that cannot be detected, errors, etc., to improve accuracy and complete testing. , excellent quality effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

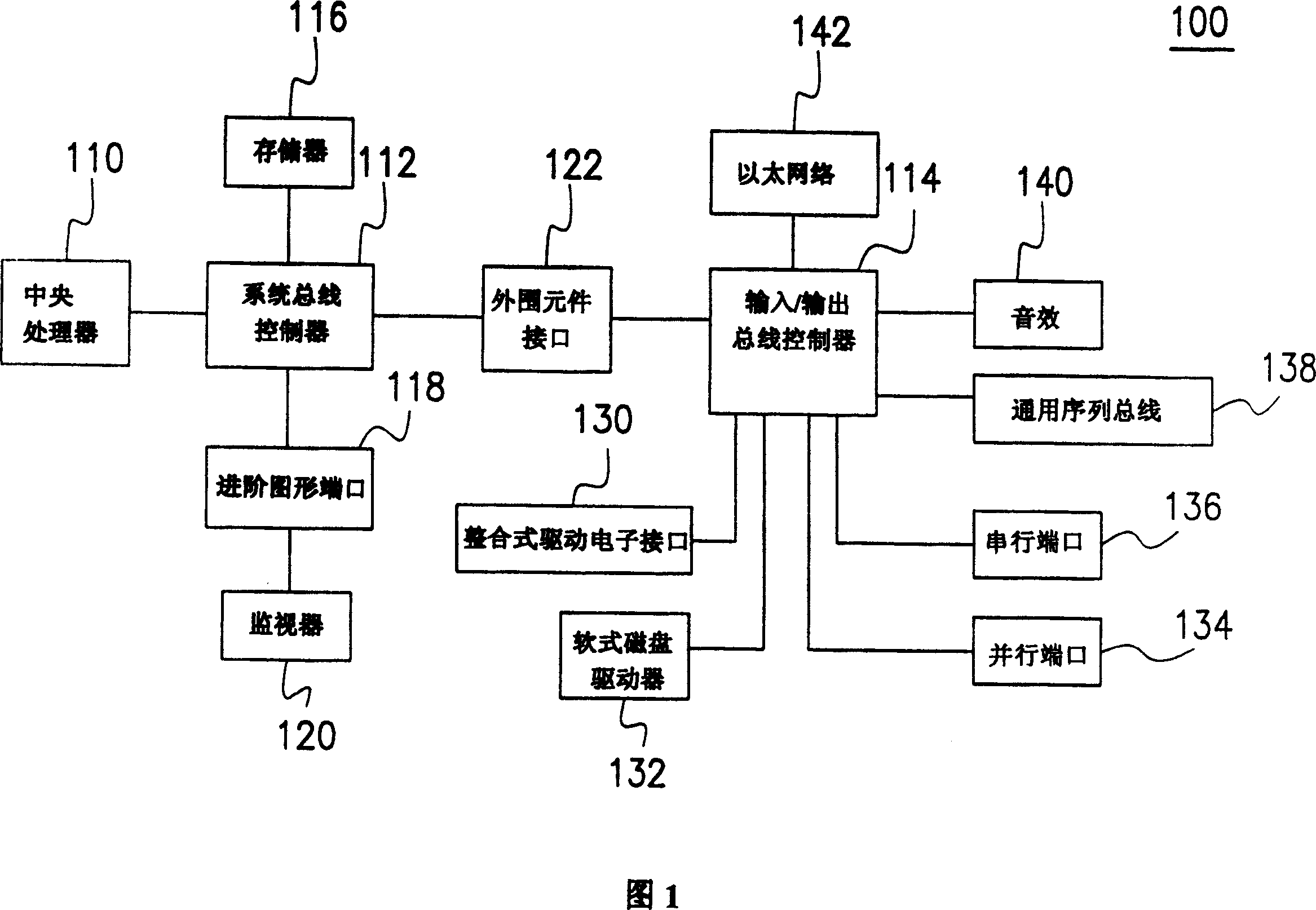

[0089] The automatic integrated circuit test equipment, device and method of the present invention are performed on a known good computer, and can be used to detect any integrated circuit in the test computer. In terms of personal computers, such as central processing units, system bus controllers, input / output bus controllers, or integrated circuits in interface modules, such as graphics accelerators. Generally speaking, these integrated circuits are configured on a printed circuit board, such as a central processing unit, a system bus controller, and an input / output bus controller are usually configured on a motherboard. Among them, the central processing unit is usually electrically connected to the motherboard through a connector, such as Socket 478, Socket 423, Socket 370, Socket 7, etc. The memory integrated circuit is configured on a module circuit board, and then is electrically connected to the motherboard through a connector, such as DIMM, RIMM, etc. As for the system bu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More