Local space shared memory method of heterogeneous multi-kernel microprocessor

A core microprocessor and shared storage technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve the problems of maintaining Cache consistency, increasing communication overhead, increasing shared data transmission delay, and extending development cycles, and achieves economical savings. The effect of reducing hardware overhead and communication overhead, reducing average access delay, and improving execution speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

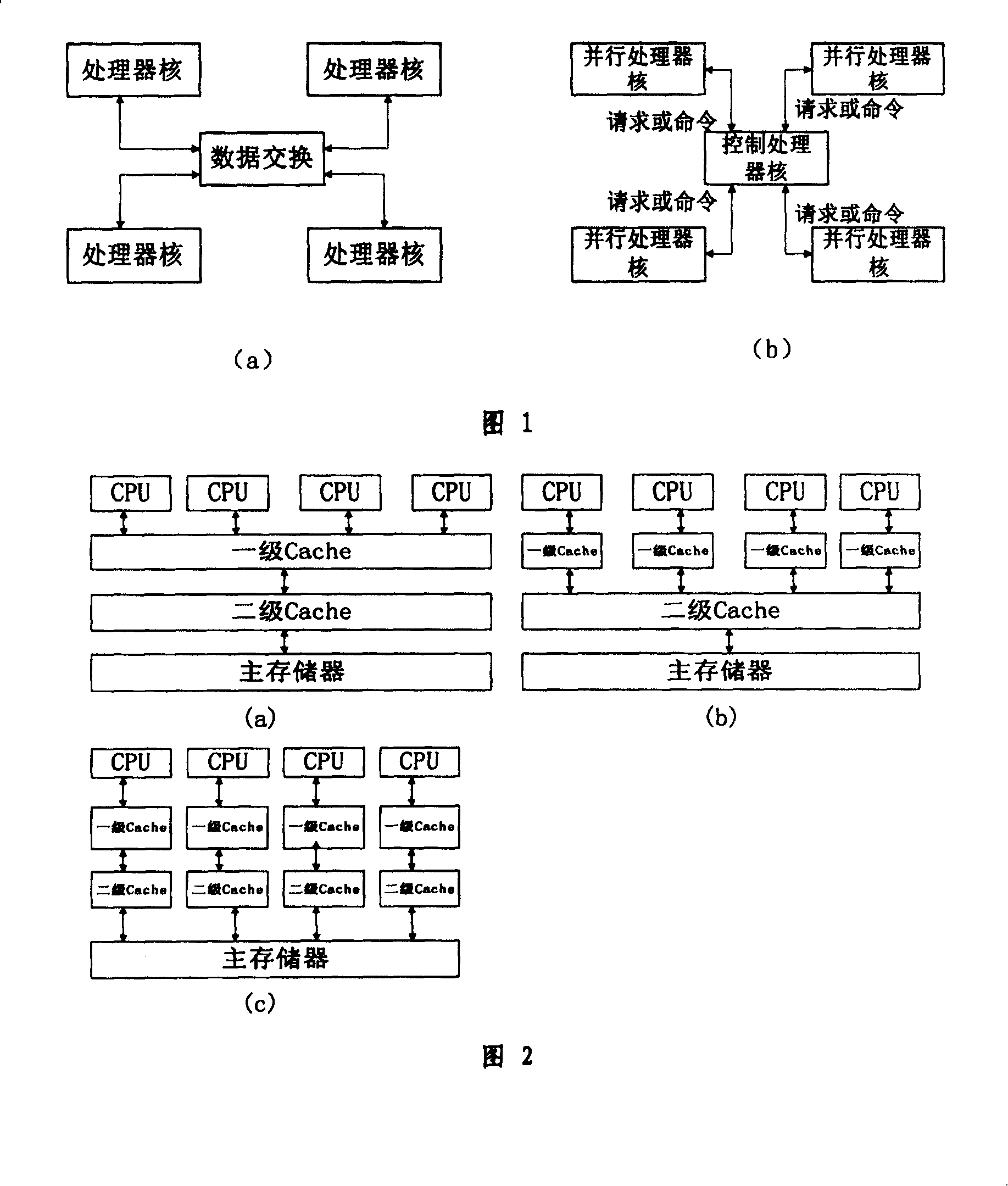

[0024] Fig. 1 is a structure diagram of two kinds of multi-core microprocessors at present: (a) is a homogeneous multi-core microprocessor; (b) is a heterogeneous multi-core microprocessor. A homogeneous multicore microprocessor contains multiple identical processor cores. A heterogeneous multi-core microprocessor contains different processor cores, usually a control processor core and multiple parallel processor cores. There is an exchange of control information such as requests or commands between the control processor core and the parallel processor core.

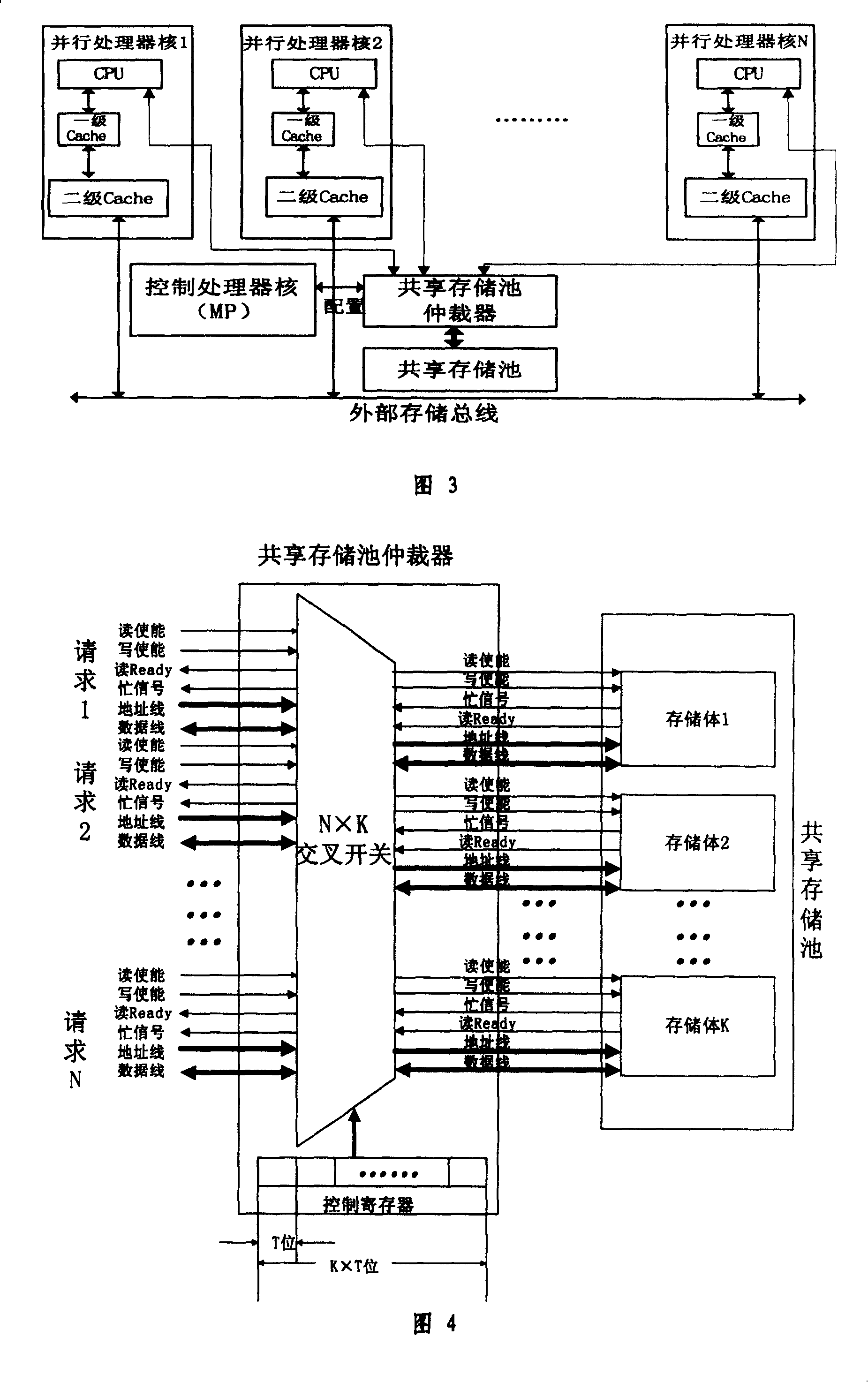

[0025] Figure 2 shows three shared storage methods based on different storage levels: (a) shared primary cache; (b) shared secondary cache; (c) shared main memory. The entire storage space is uniformly addressed, and the CPU (Central Processing Unit) of each processor core has the same priority when accessing the storage space. When the frequency of data exchange between processors is high, the performance of the share...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More