Trench MIS device having implanted drain-drift region and thick bottom oxide and process for manufacturing the same

A drift region and trench technology, applied in the manufacturing process of this MOSFET, in the field of trench gate power MOSFETs, can solve the problem of difficulty in reducing the on-state resistance of MOSFETs, achieve effective depletion, reduce on-state resistance, reduce Effect of on-state resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

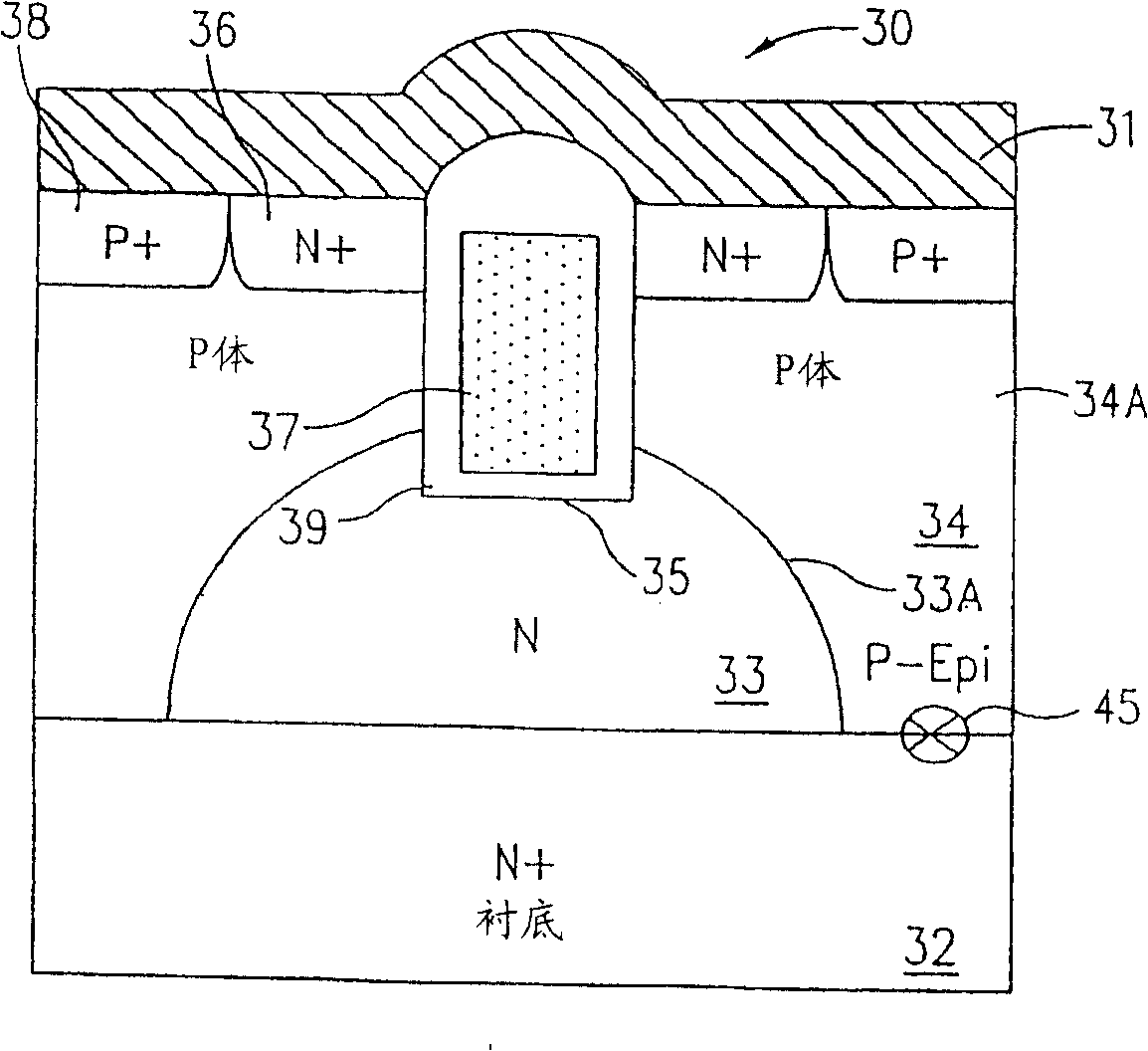

[0038] image 3 A cross-sectional view of a power MOSFET according to the invention is shown. MOSFET 30 is formed in N+ substrate 32 overlying epi layer 34, which is generally doped with P-type impurities (hereinafter simply referred to as P-epi layer 34). For example, N+ substrate 32 can have from 5×10 -4 ohm-cm to 5×10 -3 ohm-cm resistivity, P-epi layer 34 can be doped with from 1×10 15 cm -3 up to 5×10 17 cm -3 concentration of boron. N+ substrate 32 is typically about 200 microns thick, while epi layer 34 may be from 2 microns to 5 microns thick.

[0039] Trenches 35 are formed in P-epi layer 34 and trenches 35 contain polysilicon gates 37 . Gate 37 is electrically insulated from P-epi layer 34 by an oxide layer 39 extending along the sidewalls and bottom of trench 35 . MOSFET 30 also includes N+ source region 36 adjacent to the top surface of P-epi layer 34 and the sidewalls of trench 35 and P+ body contact region 38 . The remainder of the P-epi layer 34 forms a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More