Method for testing product fault-tolerant performance and fault inserting device thereof

A fault-tolerant test and fault insertion technology, which is applied to measuring devices, measuring electricity, and measuring electrical variables, etc., can solve problems such as inaccurate test results, low test efficiency, and inability to simulate fault modes, and achieve the effect of improving the degree of automated testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

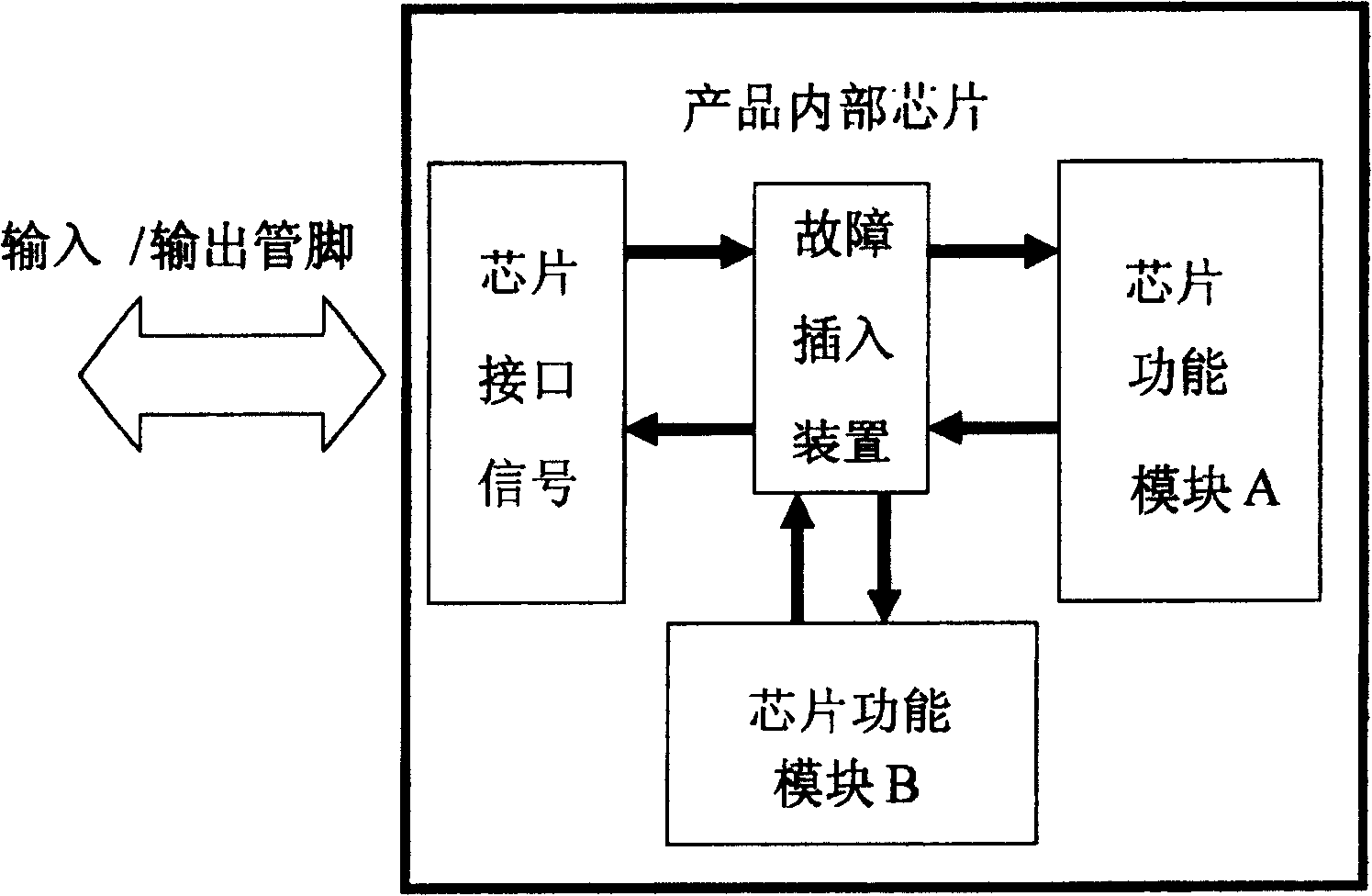

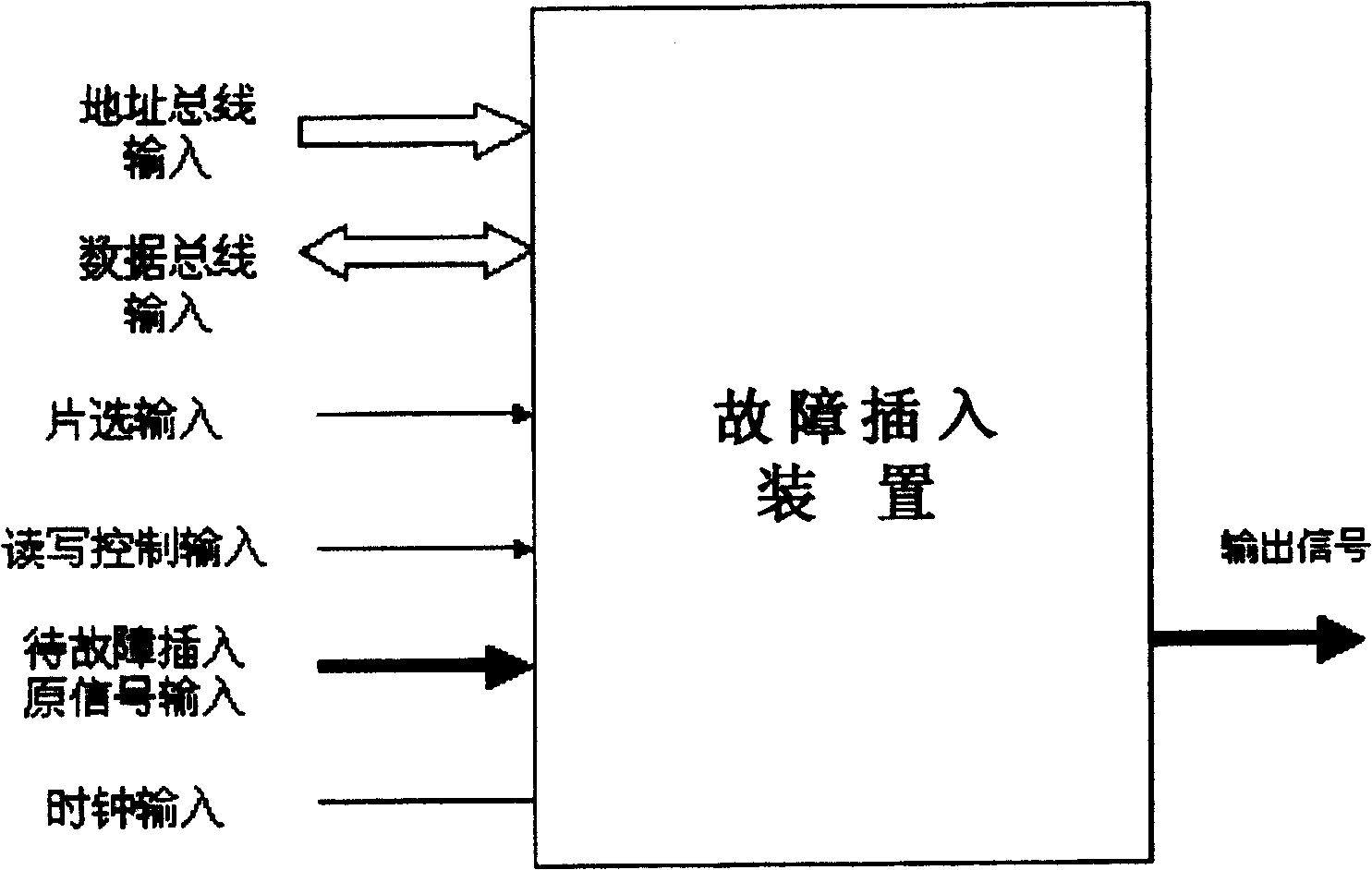

[0039] Such as figure 1 As shown, we embed a fault signal insertion unit in the programmable chip inside the product or a dedicated chip designed by ourselves. The signal that needs to be inserted into the fault is processed by the module and then connected to the corresponding functional unit. The fault unit can interface with the chip. The input and output signals of the chip and the signals between the internal functional modules of the chip are used for fault insertion processing, but it is not limited to the use at the chip I / O pins, and can also be used for the insertion of internal signal faults of the chip, such as the internal module A of the chip and the internal The fault insertion of the interface signal between modules B can also be used to simulate the failure of some functional modules of the chip, such as phase-locked loop, business processing module, CPU communication control module, etc. inside the chip.

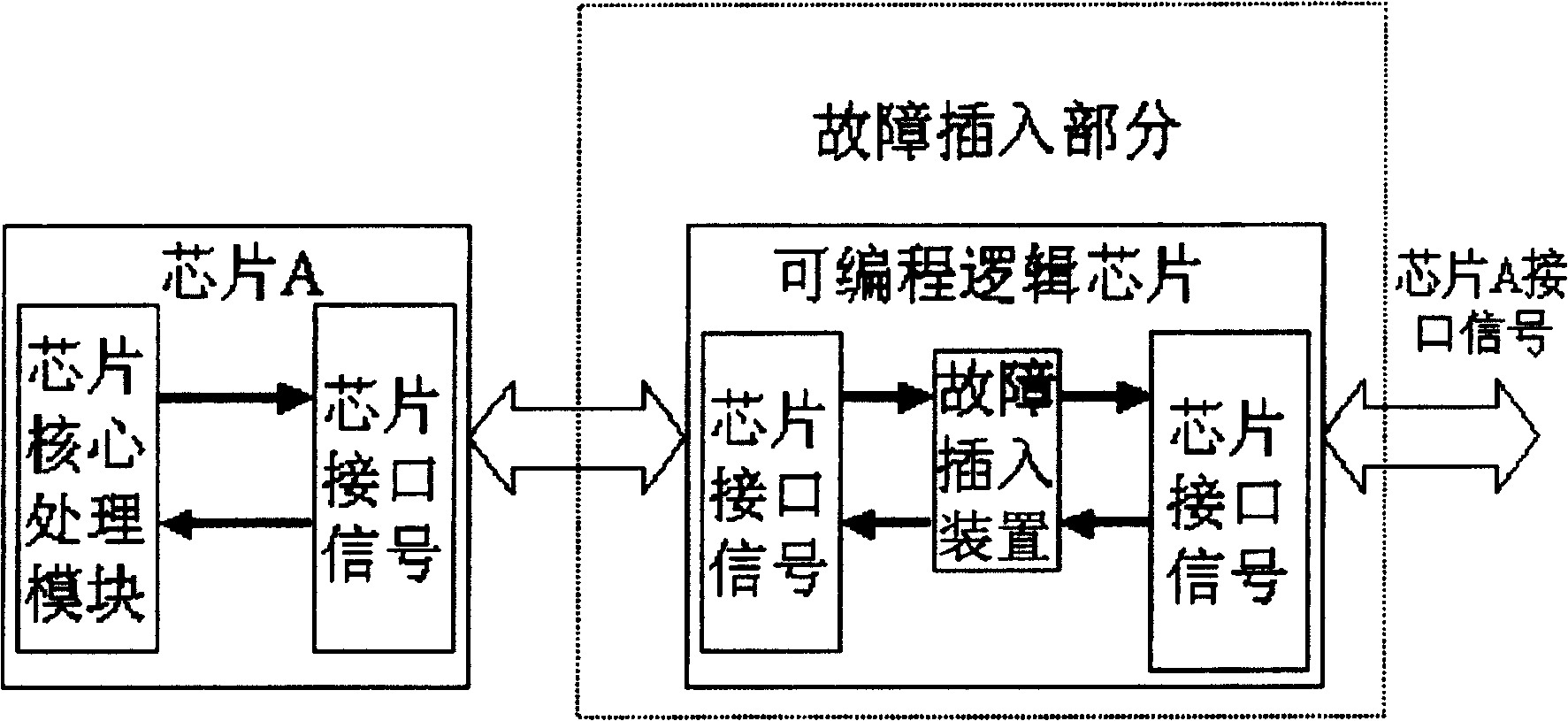

[0040] Such as figure 2 As shown, for chips that ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More