Protocol independent transmission using a 10 gigabit attachment unit interface

A protocol-independent, interface-based technology, applied in transmission systems, digital transmission systems, secure communication devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

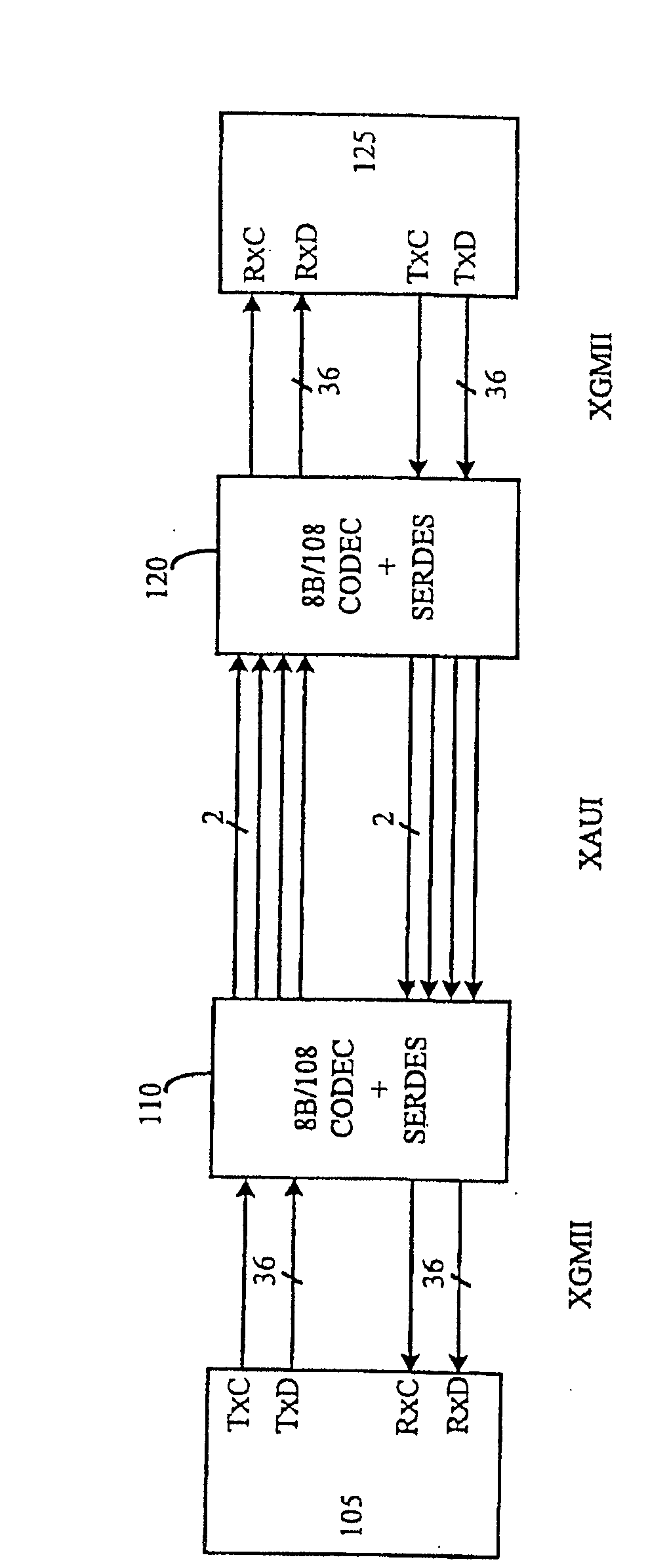

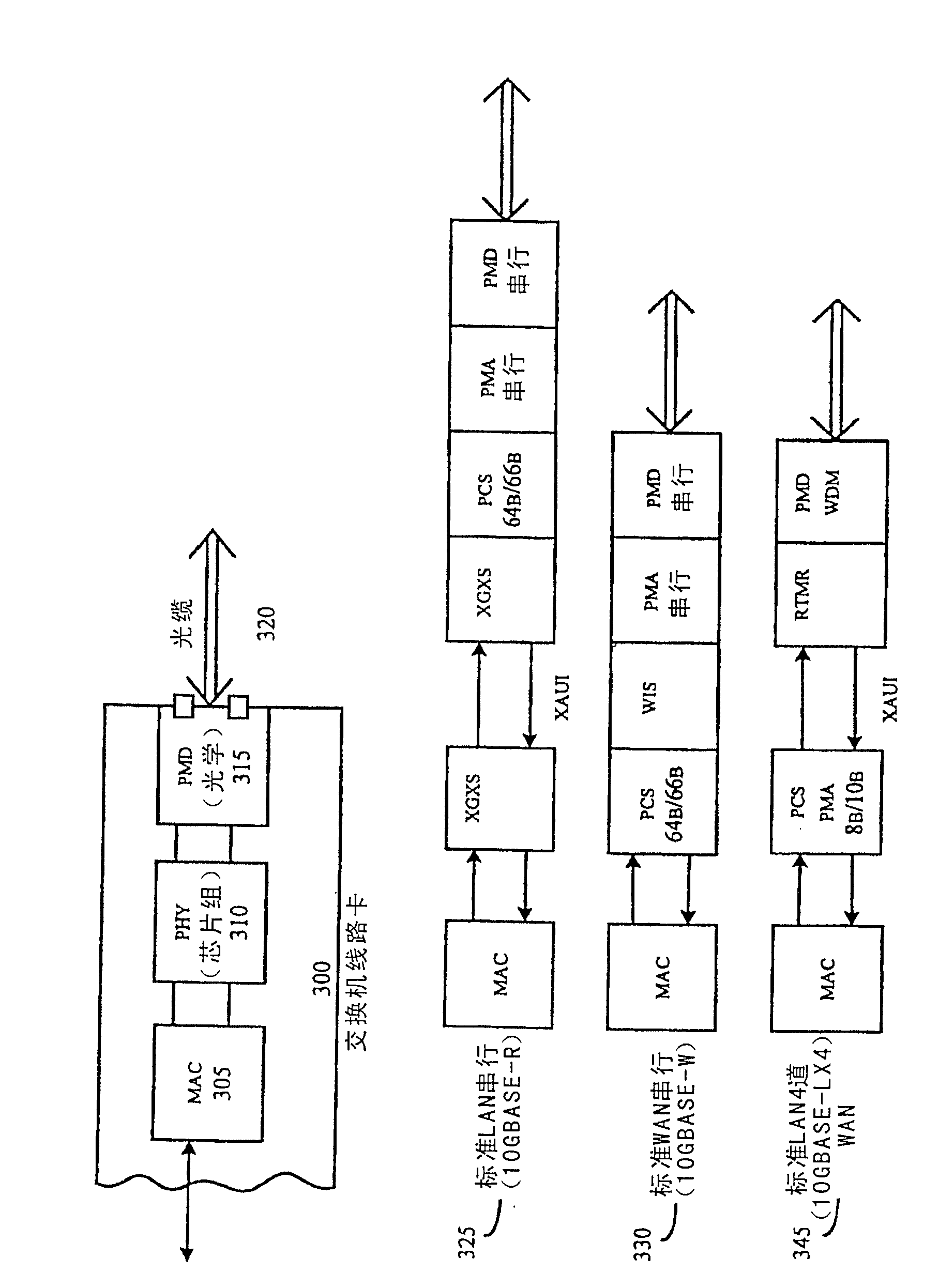

[0022] The 10GbE proposal presented in the IEEE draft P802.3ae specification defines a 10 Gigabit / s Media Independent Interface (XGMII) parallel bus architecture consisting of 74 signals (including two 32-bit data paths, one of which is in the transmit direction , the other in the receive direction; four control signals; and a clock signal). XGMII couples the Ethernet media access control (MAC) layer components (the MAC layer corresponds to the second layer of the International Standards Organization's Open Interconnection System (OSI), that is, the data link layer protocol) to the Ethernet physical (PHY) layer device (PHY layer corresponds to OSI Layer 1, which is part of the physical layer protocol).

[0023] The 10GbE specification also proposes optional XGMII extensions, consisting of two 10 Gigabit Media Independent Interface (XGMII) Extender Sublayers (XGXS) and an XAUI bus between them (“Optional XGMII Extender”; or simply "XGMII Extender") for extending XGMII up to, f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More