Non-volatile floating-gate memory based on two-layer nano silicon structure and its preparing method

A non-volatile, nano-silicon technology, used in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as affecting the charge storage capacity, and the charge storage time of nano-silicon memory can not be reached, and solve programming problems. The contradiction between time and storage time, the effect of improving charge storage capacity and controlling relative position

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

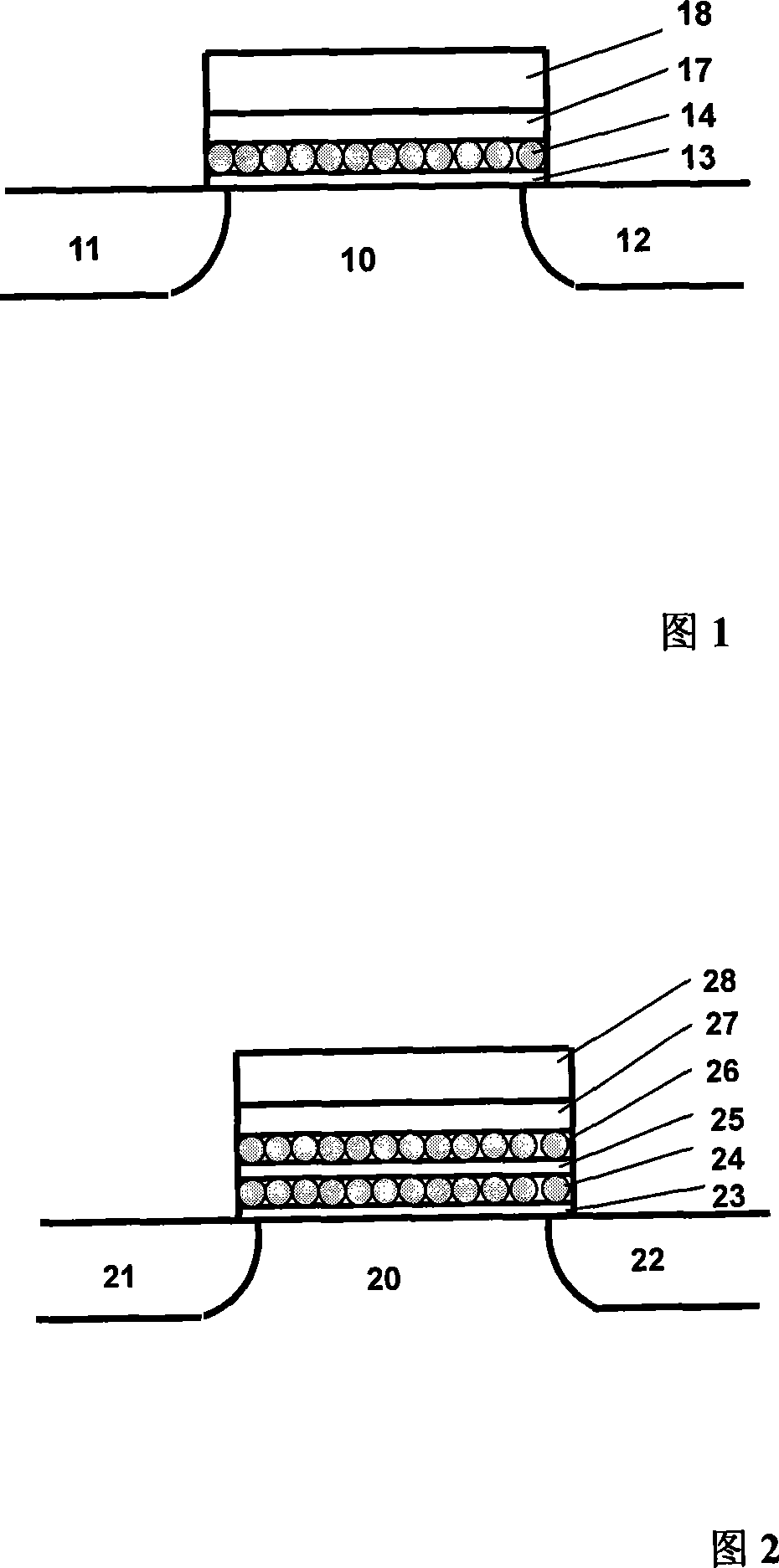

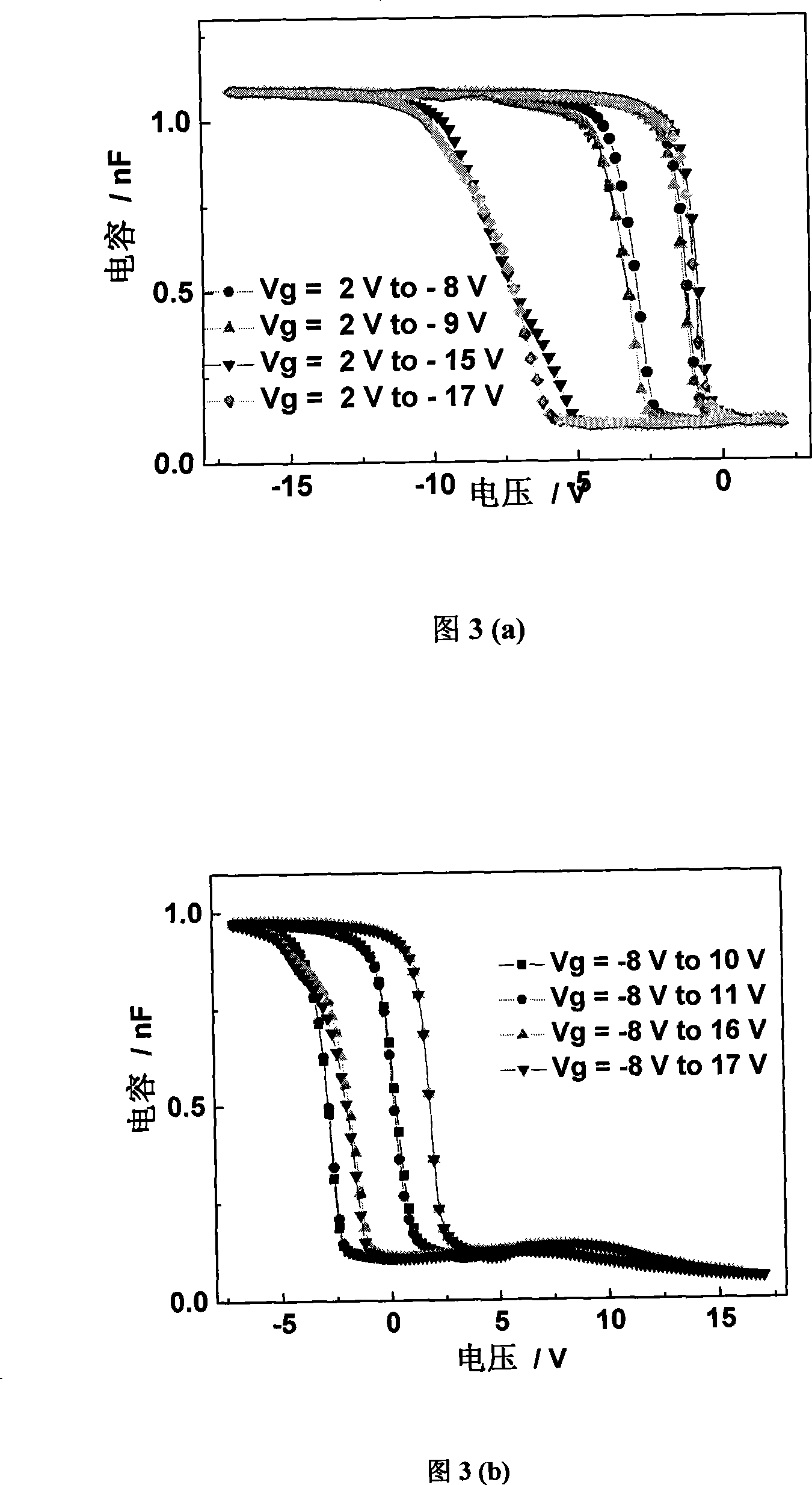

[0028] Referring to Fig. 2, the structure of the present invention: use p-type silicon (resistivity 1-10Ω·cm) as the substrate, the source and drain regions are on both sides of the substrate, and the thickness of the first layer of tunneling dielectric layer on the substrate is 1-2nm , such as 2nm SiO 2 layer; or 3-5nm, such as a 4nm SiNx layer, and then the first nano-Si layer, with a grain size of 2-7nm, such as 3 or 5nm; the second tunneling dielectric layer on the substrate is the same as the first tunneling dielectric layer; then the second nano-Si layer, with a grain size of 2-7nm, such as 3 or 5nm; deposited on the second nano-Si layer to form a silicon oxide or silicon nitride dielectric layer as a control gate, with a thickness of 10nm, 15nm also can.

[0029] 1. Use p-type silicon (resistivity 1-10Ω cm) as the substrate

[0030] 2. Formation of the first layer of tunneling dielectric layer (optional silicon oxide layer or silicon nitride layer)

[0031] 2.1 Tunne...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More