Frequency synthesizer

A frequency synthesizer, frequency signal technology, applied in the direction of automatic power control, electrical components, etc., can solve the problem of not preventing frequency deviation, increasing frequency error, and not preventing frequency deviation of input A/D converter level change shift and other issues to achieve the effect of improving frequency accuracy and preventing frequency offset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

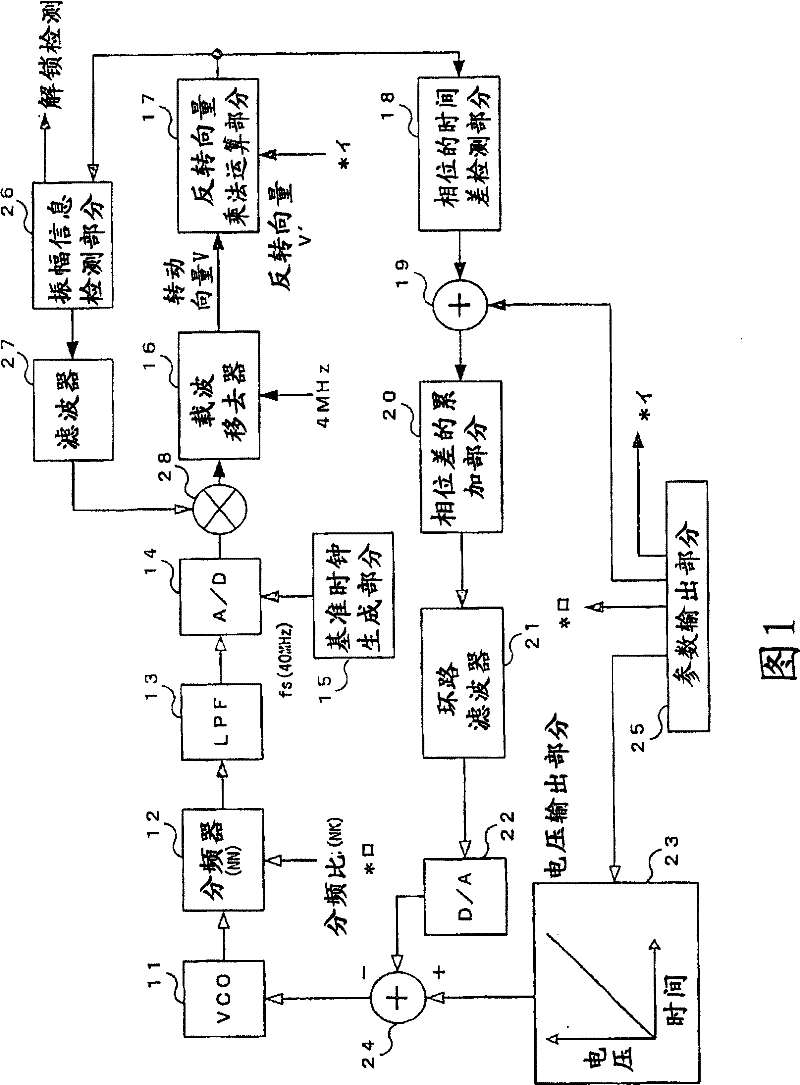

[0031] Embodiments of the present invention will be described with reference to the drawings.

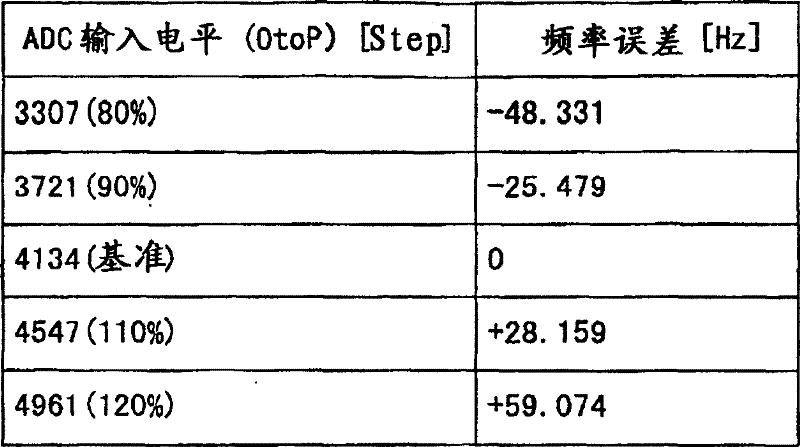

[0032] In the frequency synthesizer according to the embodiment of the present invention, an automatic gain control circuit (AGC circuit) is provided so that the output of the AD converter becomes constant, and the correction value to the AGC circuit is used to determine the input level to the AD converter. If the correction value In the appropriate range, the AGC circuit controls the gain on the output stage of the AD converter while performing the locking (synchronization) process in the PLL control. If the value is outside the appropriate range, the AGC circuit in the PLL control Unlocked for detection, thus preventing frequency drift.

[0033] [the constitution of embodiment: figure 1 ]

[0034] refer to figure 1 A frequency synthesizer according to an embodiment of the present invention will be described. figure 1 It is a block diagram showing the configuration of the fr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More