Register circuit, scanning register circuit applying same and scanning method

A technology of circuits and latch circuits, applied in the field of circuit testing devices, can solve problems such as inapplicability of consecutive domino logic gates, longer time, and increased difficulty in implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

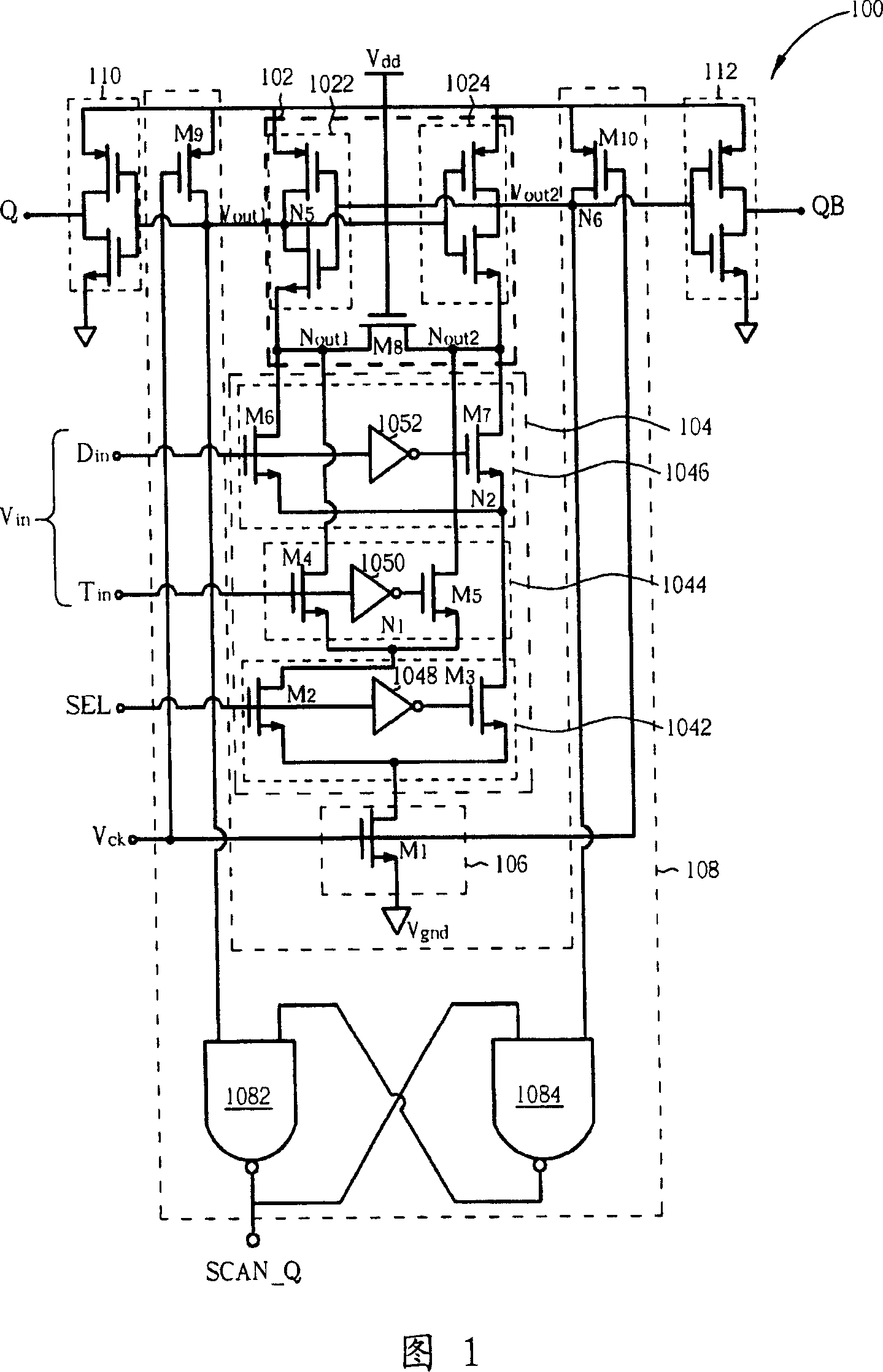

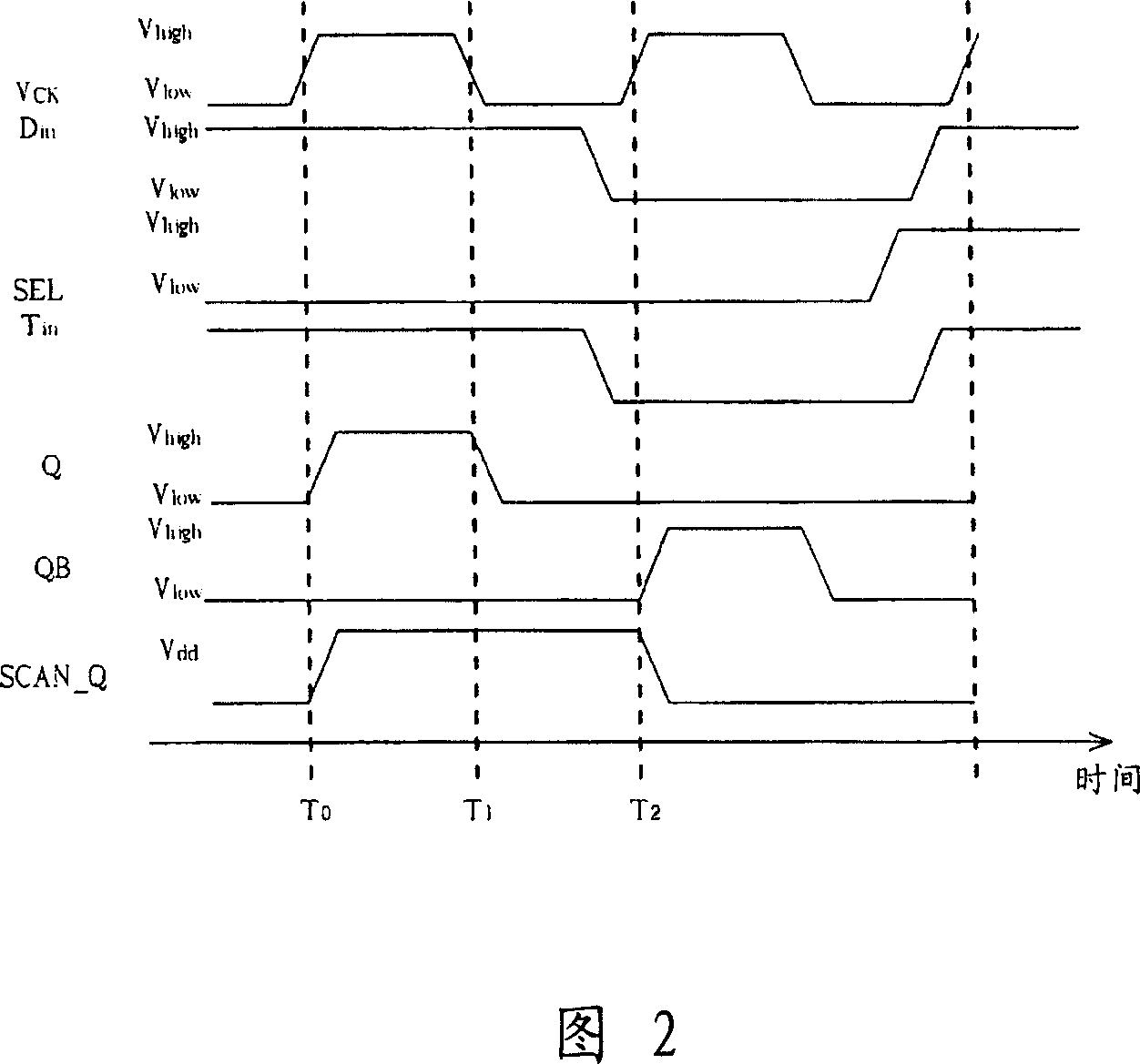

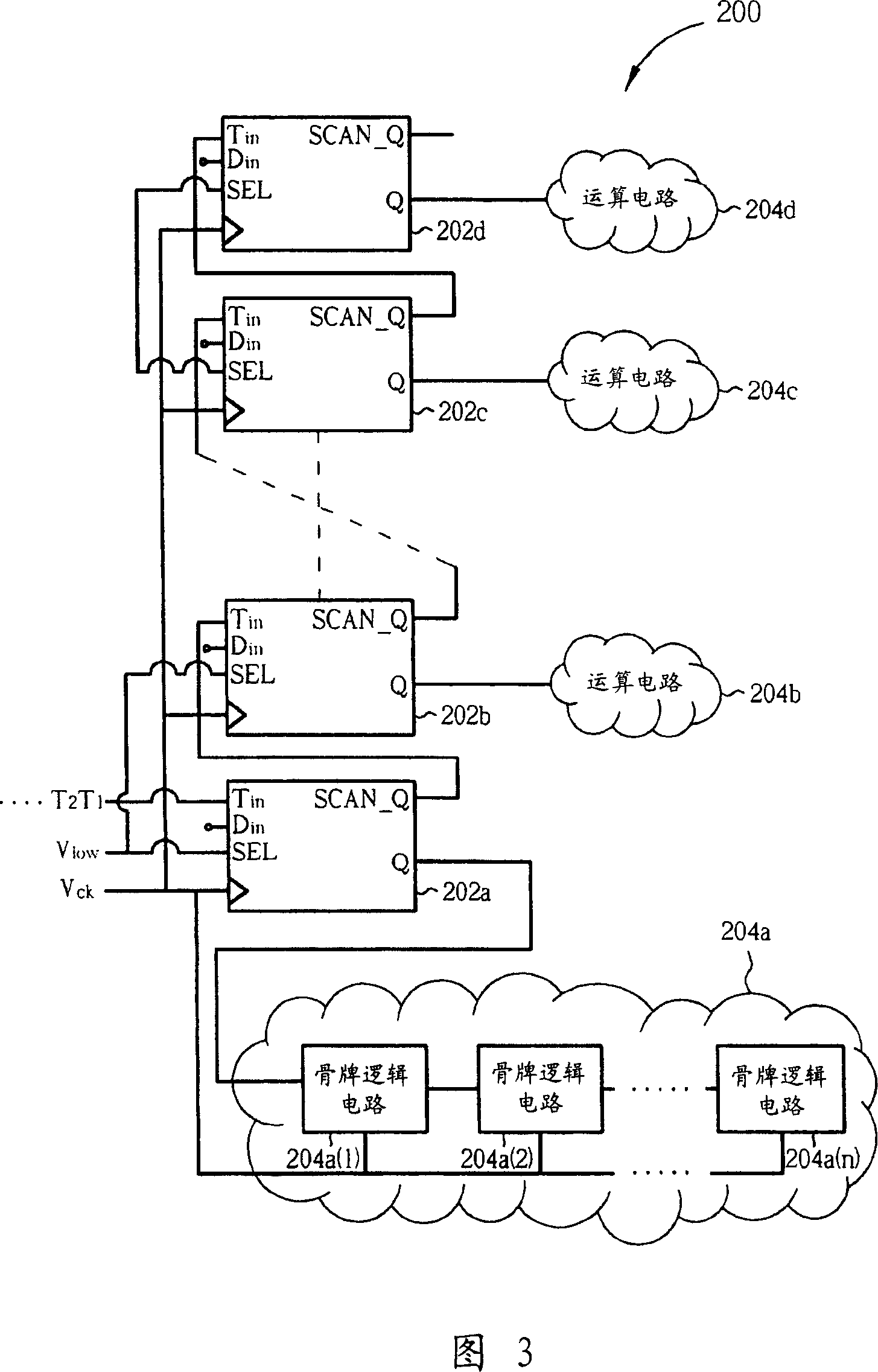

[0014] Please refer to FIG. 1 , which is a schematic diagram of an embodiment of a register circuit 100 of the present invention. The register circuit 100 includes: a latch circuit 102 , an input signal selection circuit 104 , a control circuit 106 and a scanning circuit 108 . The latch circuit 102 is used to latch an input data V in Generate an output data Q (please note that another output data QB is a complementary signal of the output data Q, so the output data Q or the output data QB can be selected according to the circuit design requirements). The input signal selection circuit 104 is respectively coupled to a non-test data D in with a test data T in , used to selectively output non-test data D in or test data T in to be processed by the register circuit 100 as the input data V in . The control circuit 106 is coupled to a drive clock V ck , used to drive the clock according to V ck Control whether the latch circuit 102 can latch the input data V in To determine...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap