Tri-states one-time programmable memory (otp) cell

A memory component and memory technology, applied in static memory, read-only memory, electrical components, etc., to achieve the effect of novel circuit and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

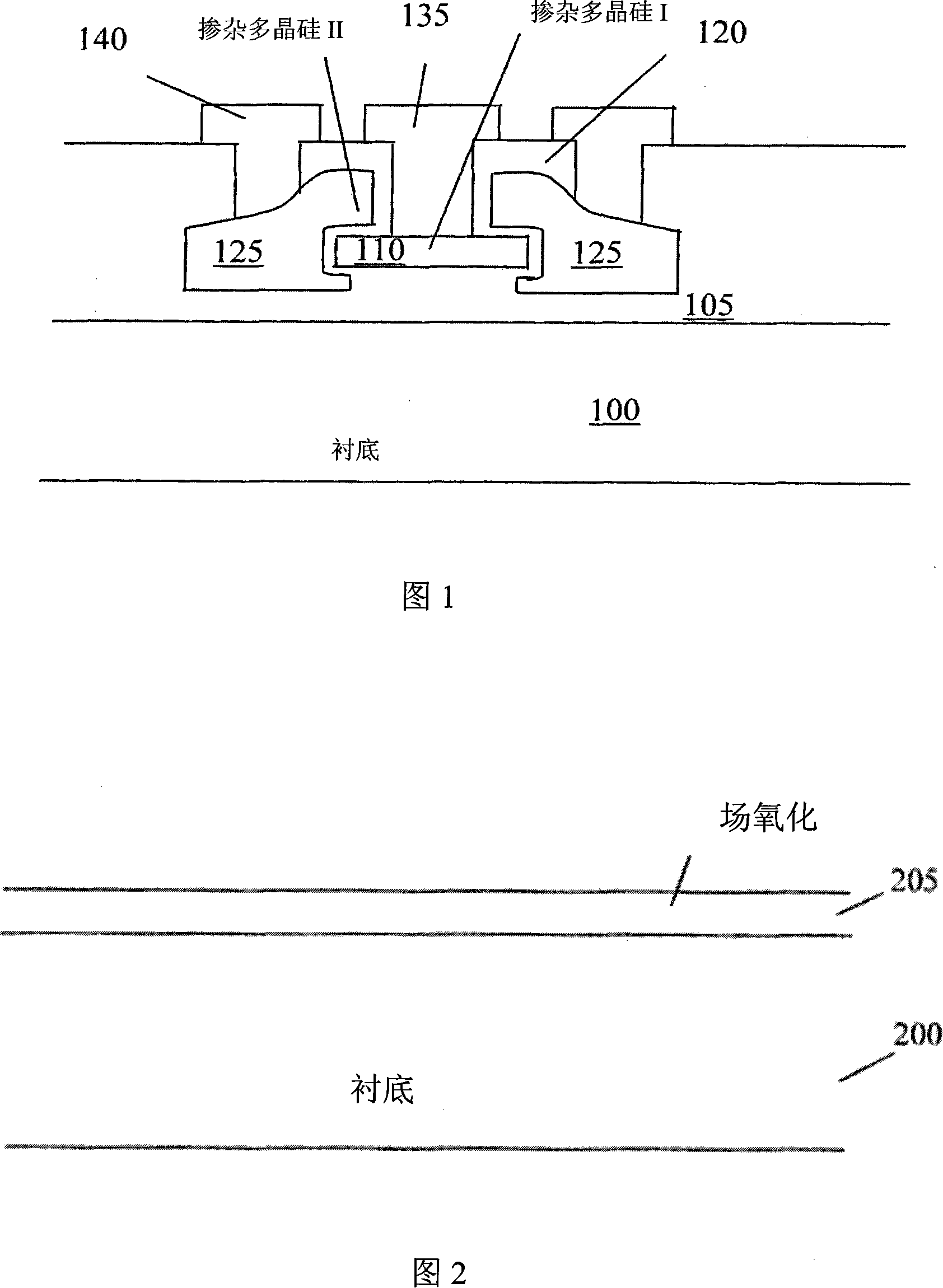

[0019]Referring to FIG. 1 , the OTP memory element of the present invention is supported on a thick field oxide layer 105 formed on the top surface of a semiconductor substrate 100 . This thick field oxide layer 105 insulates the components from the substrate 100 . The first doped polysilicon region 110 is invaded from the second doped polysilicon region 125 with a thin layer of low voltage gate oxide 120 . Each polysilicon region has electrodes such as electrodes 135 and 140 respectively connected for data recording and reading. The thin gate oxide layer 120 between the two doped polysilicon regions prevents conduction between the two doped polysilicon regions 110 and 125 . However, the conduction state between the two doped polysilicon regions 110 and 125 can be changed for memory programming purposes. In the process of programming a memory element as shown in FIG. 1 , a high voltage may be applied to the electrodes between doped polysilicon regions 110 and 125 . When the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com