Semiconductor integrated circuit and manufacturing method thereof

An integrated circuit and semiconductor technology, applied in the field of power integrated circuits and its production, can solve the problems of semiconductor integrated circuit reliability damage, power transistor damage, etc., and achieve the effect of improving reliability, low-cost manufacturing, and high-speed manufacturing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 Embodiment approach

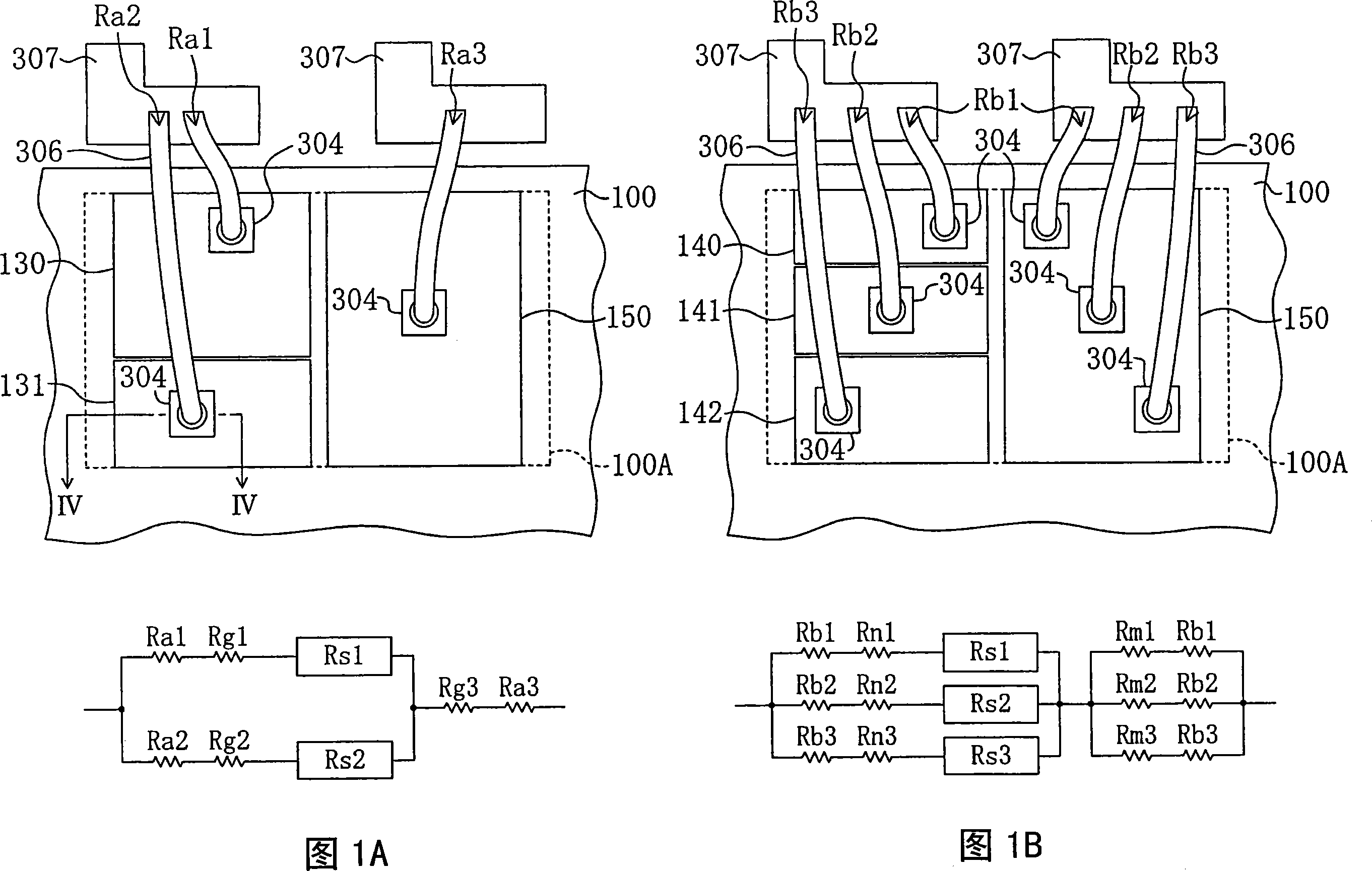

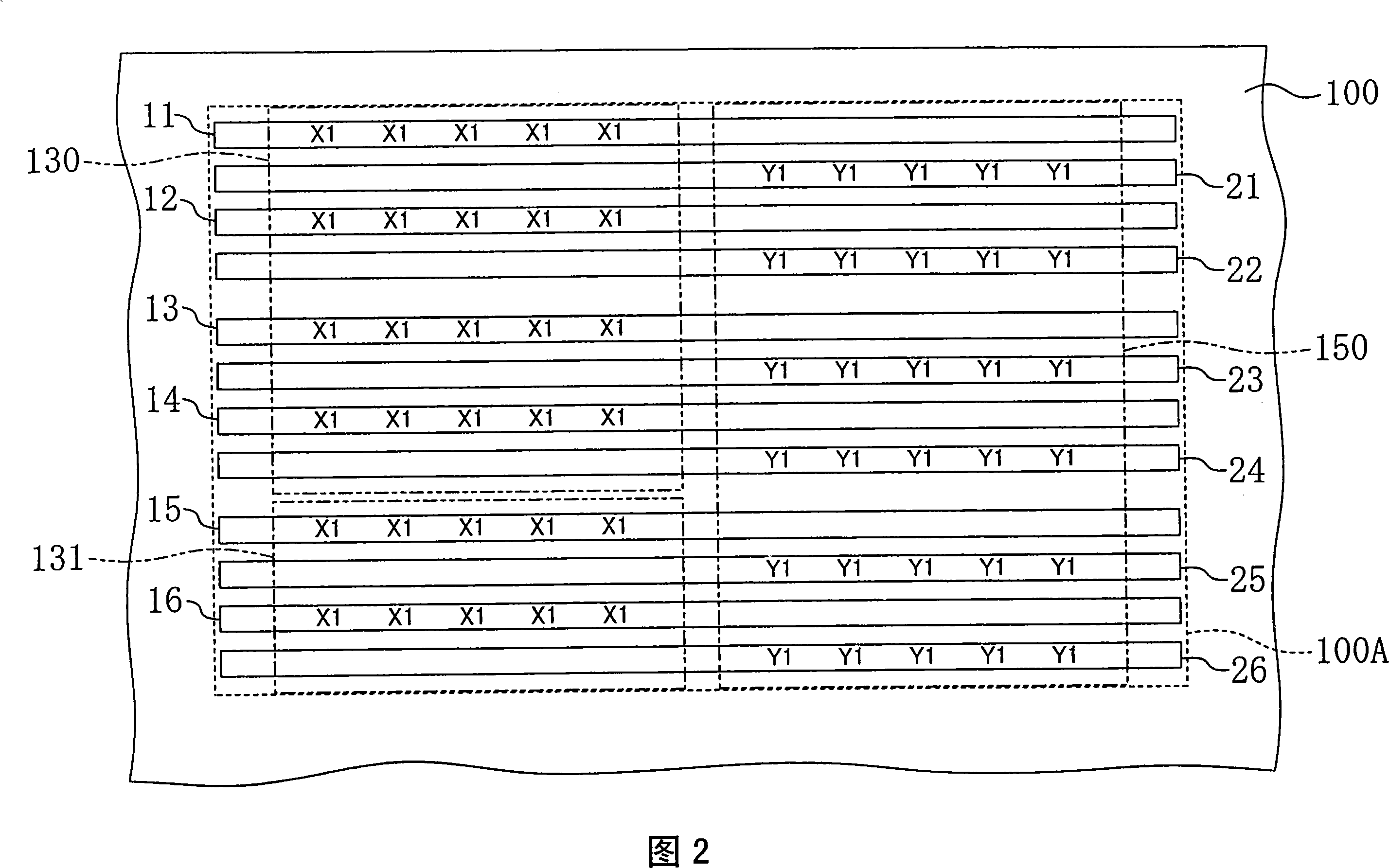

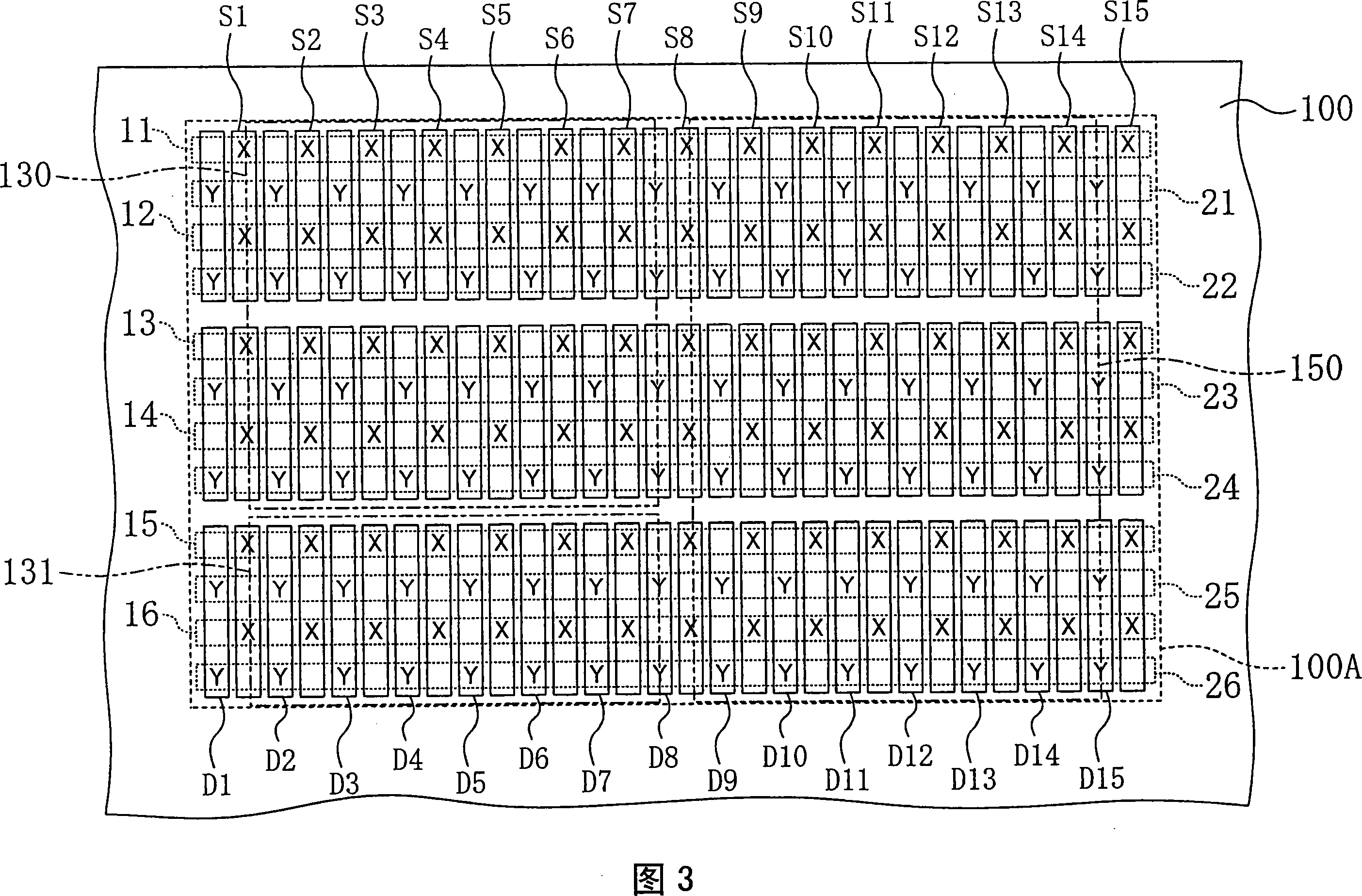

[0138] Next, a semiconductor integrated circuit and a manufacturing method thereof according to a second embodiment of the present invention will be described with reference to the drawings.

[0139] 5 and the aforementioned FIG. 1( b ) respectively show a schematic plan view and an electrical circuit diagram of a part of the semiconductor integrated circuit according to the first embodiment of the present invention.

[0140] The common feature of the semiconductor integrated circuits shown in FIG. 5 and the above-mentioned FIG. 1 (b) is that they have a plurality of divided buses and a single bus, and the areas of the multiple buses are different from each other. Starting from one side of the frame, it is sequentially reduced as it gets farther away. In addition, since the structure of the semiconductor integrated circuit shown in FIG. 1(b) above has already been described in the first embodiment, the structure of the semiconductor integrated circuit shown in FIG. Some of th...

no. 3 Embodiment approach

[0166] Next, a semiconductor integrated circuit and a manufacturing method thereof according to a third embodiment of the present invention will be described with reference to the drawings.

[0167] 6( a ) and ( b ) each show a schematic plan view of a part of the semiconductor integrated circuit according to the third embodiment of the present invention.

[0168] The semiconductor integrated circuits shown in FIGS. 6( a ) and ( b ) have a common feature that they include a plurality of divided buses and a single bus, and the areas of the plurality of buses are equal to each other. In addition, in the following description about the structure of the semiconductor integrated circuit shown in FIGS. 6( a ) and ( b ), parts that overlap with those described in the first embodiment will be omitted.

[0169] In the semiconductor integrated circuit shown in FIG. 6(a), two bus lines 130, 131 are provided which are connected to the source electrodes and have the same area as each other...

no. 4 Embodiment approach

[0184] Next, a semiconductor integrated circuit and a manufacturing method thereof according to a third embodiment of the present invention will be described with reference to the drawings.

[0185] In the fourth embodiment, first to third modification examples that can be applied to the semiconductor integrated circuit according to the above-mentioned first to third embodiments will be described. In addition, as the description of the first to third modification examples, the semiconductor integrated circuit shown in FIGS. application as an example to describe.

[0186] Modification 1

[0187] The first modification shown in FIGS. 7( a ) and ( b ) is characterized in that the active regions of the power transistors are electrically separated from each other by separation layers.

[0188] Specifically, in FIG. 7(a), the active region of the power transistor is divided into two active regions 100a1 and 100a2, and in the two active regions 100a1 and 100a2, separated layers are...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More